|

@8FEC.ADF IBM ARTIC960 Co-Processor Platform Adapter

C8FEC.ADF Init file for @8FEC.ADF

9mc105.exe ARTIC960 Startup/Option Diskette V1.05

r9mc105.txt ARTIC960 Startup/Option Diskette V1.05 README

193-258 IBM ARTIC960 CO-PROCESSOR PLATFORM

ZG93-0336 IBM ARTIC960 CO-PROCESSOR PLATFORM (HTML)

194-239 IBM ARTIC960 Coprocessor for IBM RISC System/6000 (HTML)

IBM ARTIC960 Programmable Co-Processors (overview)

Cashing in on the ARTIC960 caches

IBM ARTIC Product Support (Radisys site, archived)

IBM ARTIC Legacy Downloads (Radisys site, archived)

ARTIC Portmaster (Quadron site)

Quadron qCF C-language dev and runtime support package for ARTIC cards

Drivers & Software

Manuals

ARTIC960 Base Board

6-port V.36 AIB

Components

ADF Sections

Drivers & Software

ARTIC960 Support for AIX

ARTIC960 Support for AIX Developers Kit

ARTIC960 Support for AIX Supplemental Diskette

ARTIC960 Support for WinNT

ARTIC960 Support for WinNT Developers Kit

Realtime Interface Co-Processor C Language Support README

9as122o.txt Installation instr. for IBM ARTIC960 OS/2 ANDIS MAC Device Driver v1.2.2

9as122o.exe IBM ARTIC960 OS/2 ANDIS MAC Device Driver v1.2.2

9nw101n.exe Netware WAN HSM Installation file for the ARTIC960 PCI adapter

9nw101n.txt Netware WAN HSM Installation instructions for ARTIC960 PCI adapter

9od122o.exe OS/2 Developer's Kit for the ARTIC960 PCI adapter

9od122o.txt OS/2 Developer's Kit Installation for ARTIC960 PCI adapter

9os122o.exe Installation file for the ARTIC960 PCI adapter (OS/2)

9os122o.txt Installation instr. for the ARTIC960 PCI adapter (OS/2)

Note: It is conceivable that IBM included support for

MCA in some of the driver disks for the 960Hx and Rx PCI ARTICs.

Manuals

ARTIC 960/ARTIC 960PCI Co-Processor Guide to Ops Supplement (thx to Jiri Zlamal)

ARTIC STREAMS Support WAN Driver Interface Reference

ARTIC960 Co-Processor Platforms Hardware Technical Reference

ARTIC960 Programmer's Guide (Dec 2000), ARTIC960 PCI, 960Rx, 960Hx, 960RxD, 960 MCA

ARTIC960 Programmer's Reference

ARTIC960 STREAMS Environment Reference

ARTIC960 Co-Processor Platforms Application Interface Board Developer's Guide

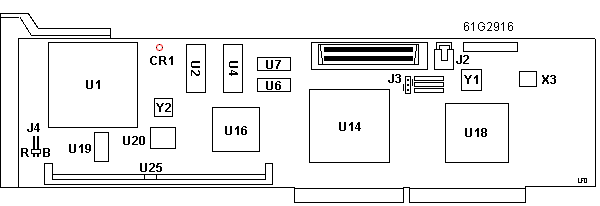

ARTIC960 Base Board FRU P/N 61G2916, P/N 06H4651

CR1 LED

J1 140 pin AIB connector

J2 Serial Debug Port ?

J3 Clock Signal Termination

J4 Unk RED / BLACK

U1 80960CF-25

U2,4 Micron MT4C16257DJ-7

U6,7 Fujitsu 81C4256A-70 256Kx4

U14 34G1519 "Brighton" Memory ctrl.

|

U16 06H2142

U18 34G1521 "Miami" MCA iface

U19 P174FCT

U20 06H3691

U25 Packet memory

X3 Spare

Y1 40.000 MHz osc (MCA Bus)

Y2 25.0000 MHz (i960)

|

U1 80960Cx 80960CA 25MHz (initial production) replaced by 80960CF (later production). The CA and CF are register compatible.

U2,4 Instruction memory (DRAM SOJ modules) 1 or 4 MB, 1 to 3 wait states. Could be ordered with 4MB!

SWAG - 4MB version adds U3, U5 Micron MT4C16257DJ-7?

U19 Pericom P174FCT - Fast CMOS Octal D Flip-Flop with Master Reset (datasheet)

U20 06H3691 EPROM?

U25 72-pin SIMM, 1 (std), 4, 8, or 16 MB (mine had a 1Mx40, ECC, 80 ns SIMM in it.

LED Codes

The LED flashing sequence may be particularly useful for errors that occur

very early on in Preliminary POST, thus preventing notification via the ISP

Register. The No. of Flashes defines a period of consecutive visible flashes

followed by a pause. This pattern is repeated indefinitely.

| Error Name |

Error Source and Description |

No. of Flashes |

| BaseCheckSum |

Base ROM checksum test failed |

1 |

| ProcessorBus |

Processor bus test failed |

2 |

| LocalBus |

Local Bus test failed |

3 |

| Reserved |

|

4 |

| NOMEM_FAIL |

Packet memory not detected during boundary test |

5 |

| P1MEG_FAIL |

Lower 1MB of packet memory failed memory test |

6 |

| ProcessorFault |

Processor fault occurred |

7 |

| SSID Mismatch |

The SSID is not as expected |

8 |

What is the purpose of the light on top of the ARTIC card?

The light on the ARTIC card indicates the status of the ARTIC POST routines.

The light normally comes on during POST (power on or reset), and goes off after

successful completion of POST. If the light remains on, an error has been

detected and an error code will be in task 0's secondary status buffer. A

flashing light indicates a memory error on the card (since the error code can

not be reported via memory).

One other difference in reset between Micro Channel and PCI systems is that

Ctrl+Alt+Del does not reset adapters in PCI systems.

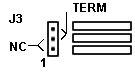

J3 Clock Signal on ARTIC960 Co-Processor Platform (Micro Channel)

The ARTIC960 supplies a clock signal (25MHz) to the AIB. This signal must be

terminated at all times. Normally, the AIB circuitry terminates this signal. The

ARTIC960 has a three-pin jumper (J3), which provides an on-card

resistance-capacitance (RC) termination for the clock. If you do not have an AIB

installed, J3 is jumpered 2-3 to terminate the clock signal on the ARTIC960.

When an AIB is installed, J3 is jumpered 1-2, which is a "no-connect" position

for the on-card termination circuitry, and allows the termination to take place

using the AIB circuitry.

Note: On this ARTIC960

with an installed AIB, J3 was jumpered for 3-2, which is

supposedly for Termination. Possibly not correct...

Warning! Damage to the Memory Controller Chip

and/or the Micro Channel Interface Chip could occur if the termination is not

used when the co-processor is powered up without an AIB attached.

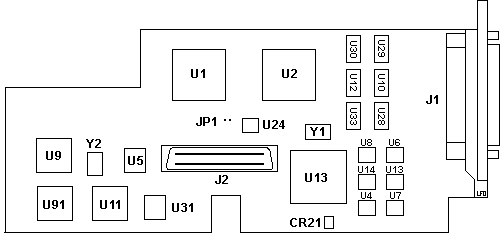

6-port V.36 AIB FRU P/N 11H3795, 52G0985?

CR21

J1 100-pin header

J2 140-pin AIB connector

JP1 Two solder pads

U1,2 34G1522 VERO AIB/DMA

U4,6,7,8,13,14 DS36950V

U5 AM28F256-200JC

|

U9,11,91 SC26C562C1A

U10,12,28,29,30,33 LT1141ACS

U13 06H6556

U24 06H3889

Y1 12.2880 MHz osc

Y2 14.7456 MHz osc (DUSCC clock)

|

U1,2 34G1522 VERO

AIB/DMA - CFE Local Bus/AIB Interface Chip Vero Datasheet

VERO was superseded by the VOLANT chip on ARTIC960 PCI AIBs. Volant Datasheet

U9,11,91 SC26C562C1A

Dual universal serial communications controller (DUSCC) Datasheet

DS36950 Quad

Differential Bus Transceiver Datasheet

LT1141A Advanced Low

Power 5V RS232 Drivers/Receivers with Small Capacitors Datasheet

Components

# 6930 ... ARTIC 960 Adapter 61G2925

# 6933 ... 4 MB memory

# 6934 ... 8 MB memory

# 6940 ... Application Interface Board, 4-port Selectable 61G2960 / 61G2961 4-port Multi-interface Aib

High-speed 4-Port Multi-interface AIB that offers either EIA-232, EIA-530 (RS-422), ISO 4903

(X.21), or ISO 4902 (V.36) electrical interfaces for

generalized applications. The

selection of the specific interface is achieved by

a matching cable (four ports of either 232, 422, X.21, or V.36)

|

# 6930 ... ARTIC 960 Adapter 61G2925 |

|

# 6941 ... cable, 4-port EIA-232 61G2918 |

|

# 6932 ... cable, 4-port EIA-530 / EIA-422 61G2923 |

|

# 6943 ... cable, 4-port X.21 61G2928 |

|

# 6944 ... cable, 4-port V.36 61G2933 |

- At least four to six times the performance

of Portmaster Adapter/A. The 4-Port Multi-interface

Application Interface Board handles four lines of

communications data at 2.048 megabits per second.

- Intel (1) 80960ca 25-MHz processor

- Support for DMA 32-bit bus master and

peer-to-peer capability on the Micro Channel

- 64-bit streaming data (80MB/s) capability

- From 2 to 17MB of memory (capability

of 1 to 20MB through an RPQ)

- Architected to accept a 32MB single

in-line memory module (SIMM)

- System Control Block (SCB) Move-mode

For the '94 RS/6000 versions, memory supported has

dropped to the 1, 4, or 8MB SIMM.

- From 2 to 9MB of memory (additional memory available via an RPQ)

Included in this announcement is a high-speed 4-Port multi-interface

Application Interface Board (AIB). The AIB offers either EIA-232D

(asynchronous), or EIA-530 (RS422), or ISO 4903 (X.21) or ISO 4902 (V.36)

electrical interfaces for communications applications. The selection of the

specific interface is achieved by a matching cable (4 ports of 232 or 4 ports

of 422 or 4 ports of X.21 or 4 ports of V.36).

The application development driver is intended to provide a level of

interface to the adapter for those developing applications using the ARTIC960

and is not a full-function driver. The application development driver is

contained in the diagnostic diskette.

A developer's kit is offered that provides AIB design information, sample

programs, a programmer's guide/reference, and a hardware technical reference

manual. As part of the developer's kit a Developer's Assistance Program (DAP)

is provided for parties who will be developing their own software applications

and/or designing their own application interface board. The ARTIC960 DAP

Limitations

The ARTIC960 adapter requires a 32-bit slot in the following Micro Channel

machines

There is no limitation on the quantity of ARTIC960 cards per

system other than 32-bit Micro Channel long slot availability and the amount of

power furnished by the system. A typical ARTIC960 adapter, without the AIB,

draws 12.5 watts of 5VDC power. The Multi-interface AIB draws an additional 3.7

watts.

Limitations RS/6000

There is a limitation of 5 IBM ARTIC960 coprocessor with the supplied driver

in all models except Machine Type 7009 Model C10 which has a limit of 2.

Memory

The adapter is designed with two memory banks. The instruction memory is 1MB

large and is soldered in place. The other memory bank or data memory (also

referred to as "packet") is provided in the form of a selectable pluggable SIMM

package. The SIMM sizes are 1, 4, 8, and 16MB, with the card designed to accept

a 32MB SIMM. A SIMM must be installed for the ARTIC960 to operate.

Note: I have an ARTIC960 with a 6 port V.36 AIB,

and the SIMM is a 4M ECC SIMM. 68X6356 1Mx40 E 80 ns, 5 V

@8FECH ARTIC960 Co-Processor Platform Adapter

Modify the ADF file so that all features are "disabled" and remove the

ability to disable channel check sources. Channel check sources is always

enabled. Change Advanced Co-Processor Platform Adapter to ARTIC960 Co-Processor

Platform Adapter.

Device I/O Address Six-bit field that

selects the I/O address of the ARTIC960 Adapter. The six bits represent bits 15

through 10 of the I/O address. Address bits 15, 14, and 13 are in POS register

5. Address bits 12, 11, and 10 are in POS subaddress 100 (POS register 3A).

<"1C00H-1C1FH">,

3C00-3C1F, 5C00-5C1F, 7C00-7C1F, 9C00-9C1F, BC00-BC1F, DC00-DC1F, FC00-FC1F

Interrupt Level

Prioritized interrupt request line on which the ARTIC960 Adapter

interrupts the system. The highest to lowest interrupt priorities are as

follows: 9, 10, 14, 7. The interrupt level may be shared with another adapter.

The preferred interrupt level is 7.

<"Level 7">, 10,

14, 9

Primary Arbitration Level

Primary arbitration level for the ARTIC960 Adapter Busmaster DMA

transfers. Arbitration level of 0 has highest priority, and increasing levels

have corresponding decreased priority

<"Level E">, D, C,

B, A, 9, 8, 3, 2, 1

Streaming Data

Enable or disable Streaming Data feature of the ARTIC960 Adapter

as both a Bus Master and a Slave. Default is disable, which causes the adapter

to use the basic data transfer procedures. When enabled, the streaming data

procedure is supported.

<"Disabled">,

Enabled

Selected Feedback Return

Enable or disable checking and reporting of loss of Selected

Feedback Return by the ARTIC960 Adapter Bus Master. Default is disable.

<"Disabled">,

Enabled

Address and Data Parity

Enable or disable address and data parity checking / generation by

the ARTIC960 Adapter. The default is disable.

<"Disabled">,

Enabled

Asynchronous/Synchronous Channel Check

Mode that the ARTIC960 Adapter uses when driving -CHCK active.

When synchronous mode is selected, -CHCK is signaled by the adapter with a

pulse on -CHCK during the data transfer cycles. When selected for asynchronous

mode, the adapter drives -CHCK active asyschronously to a data transfer, i.e

-CHCK remains active until reset by the system master. Default is

Asynchronous.

<"Asynchronous">,

Synchronous

1st Shared Storage Window Location

There are two independent windows into the RAM on the ARTIC960

Adapter. The first window is located in the ROM/RAM area. The window can be

either 8 KBytes or 16 KBytes

<"DE000H-DFFFFH, 8K Window">,

DC000-DDFFF, DA000-DBFFF, D8000-D9FFF, D6000-D7FFF, D4000-D5FFF, D2000-D3FFF,

D0000-D1FFF, CE000-CFFFF, CC000-CDFFF, CA000-CBFFF, C8000-C9FFF, C6000-C7FFF,

C4000-C5FFF, C2000-C3FFF, C0000-C1FFF

<"DC000H-DFFFFH, 16K Window">,

D8000-DBFFF, D4000-D7FFF, D0000-D3FFF, CC000-CFFFF, C8000-CBFFF, C4000-C7FFF,

C0000-C3FFF

2nd Shared Storage Window Location

(This field will call the ADP)

There are two independent windows into the RAM on the ARTIC960

Adapter. The second window is located above 1 MEG. The size of this window is

equal to the amount of RAM installed on the adapter

<"Above 1M,

Window=Memory Size">

|