|

Unboxing the PS/2 8590-402! A Model 90 "Special Bid" unit! (by David Beem; YouTube)

Type 0 Complex (general info)

Model 90 with Type 0 Complex

Weitek 3167 on Type 0 Complex

AdapterID DF9F Integrated Fixed Disk and Controller

Model 90 with Type 0 Complex

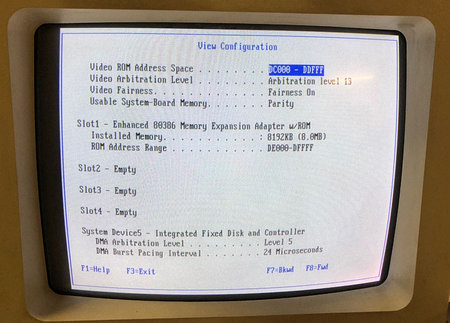

A good image showing the clean configuration. Planar XGA, 160 MB

DBA-ESDI, 4x 2 MB 85 ns on one riser, 8 MB

(4x 2 MB 80 ns) on a 2-14 80386

Memory Adapter w/ROM. About the only thing missing is support for 8x 2 MB

85 ns on the risers. That would give us 16 MB with no need for a memory

expansion adapter taking one MCA slot.

This side view shows the DBA-ESDI edge

connector seated into the planar socket. I do not know if the old style risers

(with electrolytic caps between SIMMs) is the key to success, or if the new

memory risers also work.

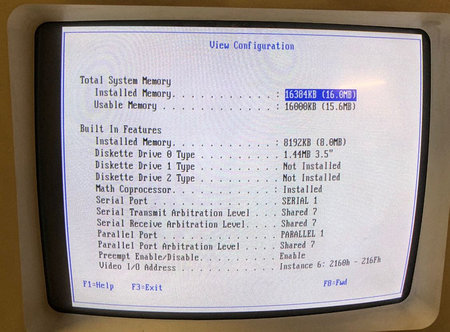

Total System Memory reports 16.0 MB Installed, 15.6 MB Usable. This includes

the memory expansion adapter!

Built In Features, Installed Memory reports 8.0 MB (planar memory).

Usable System-Board Memory is "Parity". The only type of memory supported by

the Type 0 complex.

Enhanced 80386 Memory Expansion Adapter w/ROM

Installed Memory is 8.0 MB

ROM Address DE000 - DFFFF

And here is the 160 MB DBA-ESDI, Integrated Fixed Disk and Controller.

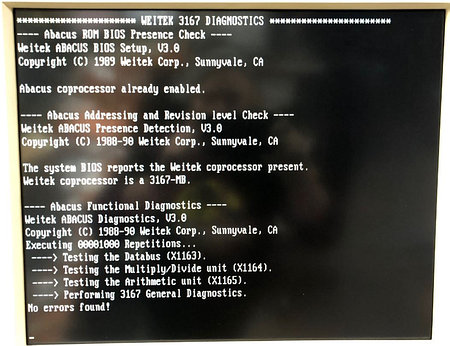

Weitek 3167 on Type 0 Complex

The 3167 Floating-point coprocessor

is a single chip successor to the three-chip 1167 (X1163 - Databus, X1164 -

Multiply / Divide Unit, X1165 - Arithmetic Unit)

This proves the 3167 is socket compatible with the Type 0 complex FPU

socket.

3167 Diagnostics

3167 looks to be supported by the Type 0 complex.

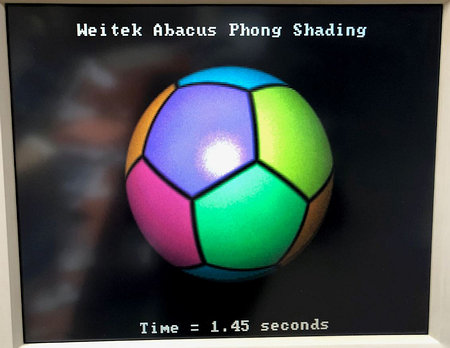

3167 Phong Shading Demo

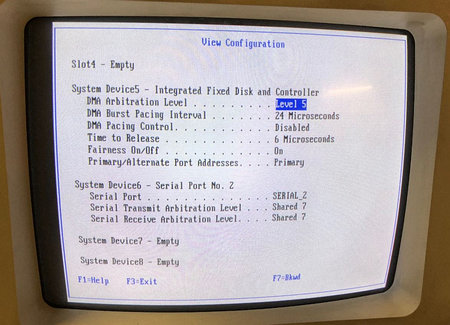

AdapterID DF9F Integrated Fixed Disk and Controller (integrated into planar ADF)

DMA Arbitration Level

DMA channel used to transfer data

<"Level

5">, 6, 7, 0, 1, 3, 4

DMA Burst Pacing Interval

Time interval between DMA transfer bursts

during which the Micro Channel is released by the fixed

disk controller for use by the processor.

<24

Microseconds>, 31, 16, Burst Disabled"

DMA Pacing Control

Enables or disables the DMA Burst Pacing Interval.

<"Disabled">,

Enabled

Time to Release

Time the fixed disk controller keeps MC after

being preempted. If 'DMA Pacing Control' is

<Enabled>, Time to Release default is immediate.

Normally, select <6 Microseconds>.

<"6

Microseconds">, 3, Immediate

Fairness On/Off

Bus Arbitration. Will adapter release control

of MC bus after using it exclusively

<"On">,

Off

Primary/Alternate Port Addresses

<Primary> or <Alternate> work

equally well. If there are two integrated fixed disks, then

select <Primary> for one and <Alternate>

for the other.

<"Primary" (io

3510h-3517h)>, Alternate (3518-351f)

|