# intel

APPLICATION NOTE

October 1986

# 82786 Hardware Configuration

Order Number: 292007-002

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

Above, BITBUS, COMMputer, CREDIT, Data Pipeline, GENIUS, i, <sup>î</sup>, ICE, iCEL, iCS, iDBP, iDIS, I<sup>2</sup>ICE, iLBX, i<sub>m</sub>, iMDDX, iMMX, Insite, Intel, int<sub>e</sub>l, int<sub>e</sub>lBOS, Intelevision, int<sub>e</sub>ligent Identifier, int<sub>e</sub>ligent Programming, Intellec, Intellink, iOSP, iPDS, iPSC, iRMX, iSBC, ISBX, iSDM, iSXM, KEPROM, Library Manager, MAP-NET, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, ONCE, OpenNET, PC-BUBBLE, Plug-A-Bubble, PROMPT, Promware, QUEST, QueX, Quick-Pulse Programming, Ripplemode, RMX/80, RUPI, Seamless, SLD, UPI, and VLSiCEL, and the combination of ICE, iCS, iRMX, iSBC, iSBX, iSXM, MCS, or UPI and a numerical suffix 4-SITE.

Ethernet is a trademark of Xerox.

MDS is an ordering code only and is not used as a product name or trademark. MDS<sup>®</sup> is a registerec trademark of Mohawk Data Sciences Corporation.

\*MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Literature Inquiries SC6-58 P.O. Box 58065 Santa Clara, CA 95052-8065

## 82786 HARDWARE CONFIGURATION

## CONTENTS

| P | ٥Δ | G |     |

|---|----|---|-----|

|   |    | Š | L., |

| 1.0 INTRODUCTION                                                        | 1    |

|-------------------------------------------------------------------------|------|

| 2.0 OVERVIEW                                                            | 1    |

| 2.2 System Bus Interface2.3 Video Interface2.4 82786 Internal Registers | 2    |

| -                                                                       |      |

| 3.0 DEDICATED GRAPHICS MEMORY<br>INTERFACE                              | 3    |

| 3.1 DRAM Configurations                                                 | 5    |

| 3.2 DRAM Timing Parameters                                              | 9    |

| 3.3 Initializing the DRAM Controller                                    | . 11 |

| 4.0 SYSTEM BUS INTERFACE                                                | . 13 |

| 4.1 Memory Map                                                          |      |

| 4.2 BIU Registers                                                       |      |

| 4.3 80286 Synchronous Interface                                         |      |

| 4.4 80186 Synchronous Interface                                         |      |

| 4.5 Asynchronous Interface                                              |      |

| 4.6 Multiple 82786 Interface                                            | . 30 |

| 5.0 VIDEO INTERFACE                                                     | . 30 |

| 5.1 Various CRT Interfaces                                              |      |

| 5.2 CRTs with TTL-level Inputs                                          |      |

| 5.3 CRTs with Analog Inputs                                             |      |

| 5.4 Using a Color Palette RAM                                           |      |

| 5.5 Using the Window Status Signals                                     |      |

| 5.6 Higher Resolutions                                                  |      |

| 5.7 Multiple 82786s                                                     |      |

|                                                                         |      |

| 5.9 External Character ROM                                              | 44   |

| 5.10 Combining the 82786 With Other<br>Video Sources                    | 45   |

| 5.11 Other Types of Displays and<br>Printers                            | 47   |

| 5.12 Calculating the Video Parameters                                   | 48   |

| 5.13 A Spreadsheet for Calculating Video<br>Parameters                  | 53   |

|                                                                         |      |

| APPENDIX A—SAMPLE<br>INITIALIZATION CODE                                | A-1  |

#### **1.0 INTRODUCTION**

The 82786 is an intelligent co-processor capable of creating and displaying high performance graphics. Both drawing and display functions are integrated into a single VLSI chip to provide an inexpensive solution for bit-mapped graphics subsystems.

This application note is intended to show, through examples, use of the 82786 and the hardware interfaces between the 82786 and the rest of the system. Because the 82786 integrates many functions onto one chip, the hardware design of a graphics system is greatly simplified.

#### 2.0 OVERVIEW

Internally, the 82786 consists of two independent processors.

| - Graphics Processor: | executes  | high-leve                   | el line |

|-----------------------|-----------|-----------------------------|---------|

|                       | drawing,  | character                   | drawing |

|                       | and bit-b | lock-transf                 | er com- |

|                       | mands to  | create and                  | modify  |

|                       | bit-maps  | in memory                   |         |

| — Display Processor:  |           | ortions of t<br>s on the CR |         |

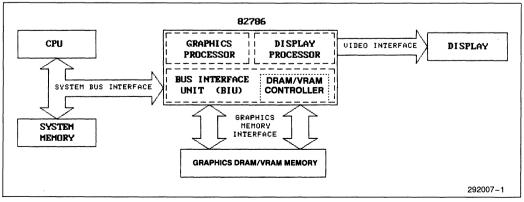

Figure 1 illustrates these processors and their hardware interfaces.

| — Graphics Memory<br>Interface: | connects dedicated graphics memory to the 82786 |

|---------------------------------|-------------------------------------------------|

| — System Bus<br>Interface:      | connects CPU and system memory to the 82786     |

| — Video Interface:              | connects the 82786 to CRT or other display      |

The video interface is controlled directly by the Display Processor. The other interfaces are controlled by the

82786 Bus Interface Unit (BIU). The BIU connects the internal Graphics and Display Processors to the CPU and system memory as well as to the graphics memory through the internal DRAM/VRAM controller.

#### 2.1 Dedicated Graphics Memory

The dedicated graphics memory provides the 82786 with very fast access to memory without contention with the CPU and system memory. Typically, the bitmaps to be drawn and displayed, the character fonts, and the command lists for the 82786 processors are all stored in this memory. In some instances it is desirable to have the Graphics Processor command lists stored in system memory.

The 82786 contains a complete DRAM/VRAM controller on-chip which interfaces directly with a wide variety of DRAMs without external logic. This direct connection not only reduces chip count but also allows the 82786 to perform very fast burst accesses to the DRAMs. The DRAM/VRAM controller can take advantage of the quick burst-mode sequential accesses made possible by page-mode, fast-page-mode (sometimes called Ripplemode<sup>TM</sup>), and Static Column DRAMs. In addition, interleaved DRAM/VRAM arrays are fully supported by the on-chip DRAM/ VRAM controller allowing even faster burst access.

#### 2.2 System Bus Interface

The system bus interface connects the CPU and its system memory to the 82786 and its graphics memory.

The most common 82786 configuration (shown in Figure 1) allows the CPU to access the system memory while the 82786 accesses its dedicated graphics memory simultaneously. It also allows the CPU to access the graphics memory and for the 82786 to access the system memory (but not simultaneously). The system bus

Figure 1. 82786 System Block Diagram

connects the 82786 graphics subsystem to the system CPU and memory. If DMA capability is also provided in the system, it interfaces to the 82786 exactly as the CPU does. The interface allows accesses in two directions.

- --- Slave Mode: CPU or DMA read or write access of the 82786 internal registers or dedicated graphics memory through the 82786

- Master Mode: 82786 read or write access to system memory

Therefore, any processor (CPU, DMA, Graphics and Display Processors) can access both the system memory and the graphics memory. The 82786 BIU arbitrates between both of the internal 82786 processors as well as the external processor (CPU and DMA) to decide which processor gets access of the bus.

The CPU software accesses both system and graphics memory in an identical manner (except that the specific memory addresses are different). Therefore the actual location of the memory (whether in system or graphics memory) is transparent to the software. However, the CPU can access the system memory faster than the graphics memory because there is less contention with the Graphics and Display Processors. When the CPU accesses the 82786, the 82786 BIU is said to be running in slave mode.

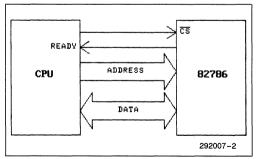

In slave mode, the 82786 looks like an intelligent DRAM/VRAM controller to the CPU (Figure 2). The CPU can chip-select the 82786 and the 82786 will acknowledge when the cycle is complete by generating a READY signal for the CPU.

Figure 2. Slave Bus Cycle

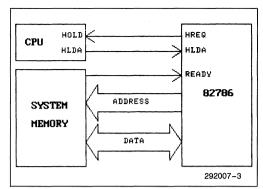

Figure 3. Master Bus Cycle

Conversely, the 82786 Graphics and Display Processors access both system memory and graphics memory in an identical manner. However, they can access the graphics memory faster than the system memory because there is less contention with the CPU. When the 82786 accesses the system memory, the 82786 BIU is said to be running in master mode.

In master mode, the 82786 looks like a second CPU controlling the local bus (Figure 3). The 82786 activates HOLD to request control of the system bus. When the CPU acknowledges the HLDA line, then the 82786 will take over the bus. When the 82786 is through with the bus, it will release HOLD and the CPU can remove HLDA to regain control of the bus.

The 82786 system bus interface is optimized to interface to an 80286 synchronously (using the same bus clock). As a synchronous slave it interprets the 80286 status lines directly and performs the requested bus accesses. As a master it generates 80286 style bus signals.

The 82786 system bus may alternatively be set up to interface asynchronously to virtually any processor. In this mode, read and write signals are used when slave accesses are performed.

#### 2.3 Video Interface

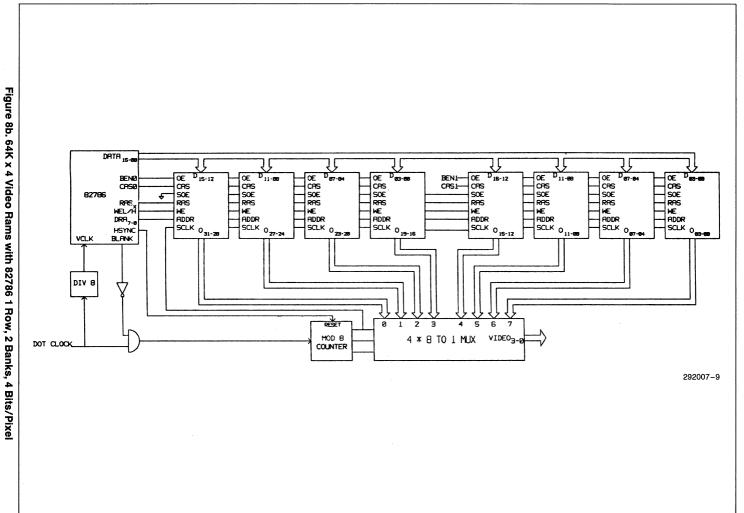

The 82786 supports two different video interfaces in order to support both standard DRAMs and dual port video DRAMs/(VRAMs). When using standard

DRAMs the 82786 reads the video data from memory and internally serializes the video data to generate the serial video data stream up to 25 MHz. When using VRAMs the 82786 loads the VRAM shift register periodically and the internal system generates the serial video data stream.

With standard DRAMs displays up to 640 by 480 by 8 resolution can be generated at 60 Hz non-interlaced refresh. With VRAMs displays up to 2048 by 1936 by 8 can be generated at 60 Hz without interlacing.

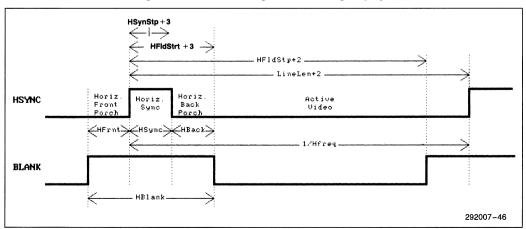

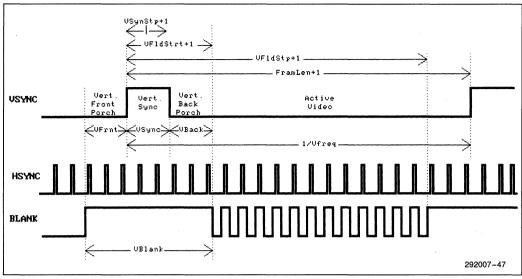

In addition, horizontal and vertical sync signals and a blanking signal are provided and may be programmed to satisfy the requirements of nearly any CRT.

In the standard DRAM mode all of the logic to support the advanced capabilities of the Display Processor such as panning, zooming, windowing, and switching between various bits/pixel in various windows is contained internally in the 82786. Provision is also made for the addition of up to four external color look-up tables.

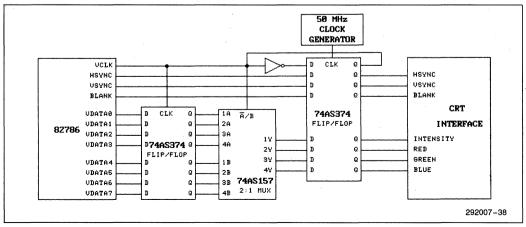

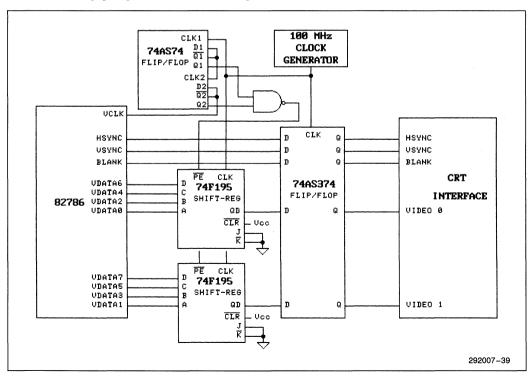

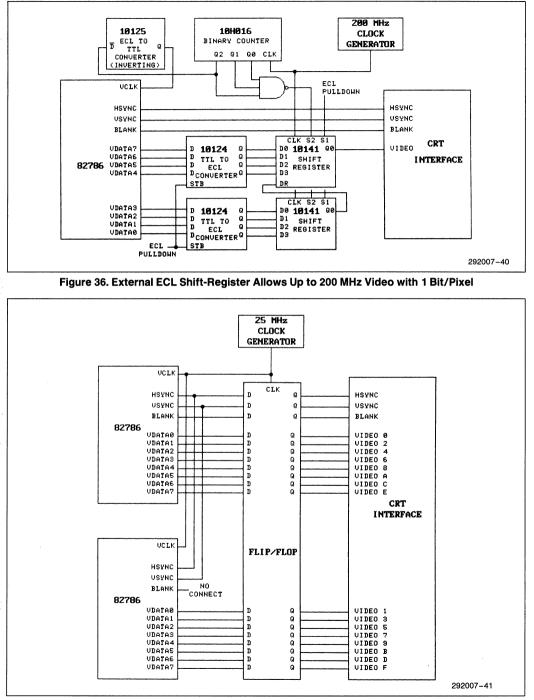

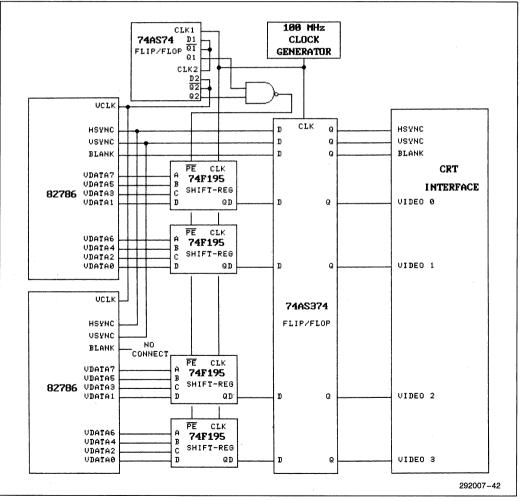

Higher resolution displays (dot clock rates greater than 25 MHz) can also be implemented by using external logic to trade-off bits/pixel for dot clock rates. Also, multiple 82786s can be used together for even greater performance.

#### 2.4 82786 Internal Registers

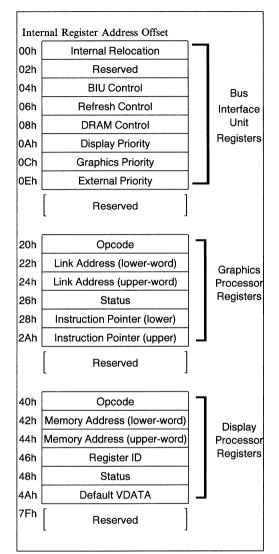

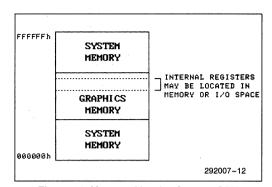

A 64 word (128 byte) direct-mapped register block is contained internally in the 82786 (Figure 4). Software may locate this register block to the beginning of any 128 byte boundary anywhere in the 82786 I/O or memory address space. No matter where these registers are mapped, they are only accessible by the external CPU. The Graphics and Display Processors can not access these registers.

Registers, located at specified offsets within this block, allow programming of the BIU and Graphics and Display Processors. The Graphics and Display Processors also have other registers which are only accessible through commands to these processors. These commands are initiated by writing into the corresponding opcode and address registers within this 128 byte register block.

All of these registers are described in detail in the 82786 data sheet. Be careful when using "reserved" registers. When these reserved registers are read, the data returned is indeterminate. When these reserved registers are written, they should only be written as zeros to ensure compatibility with future products.

Figure 4. 82786 Internal Registers

#### 3.0 DEDICATED GRAPHICS MEMORY INTERFACE

The 82786 contains a full DRAM/VRAM controller on-chip which allows it to be connected directly to arrays of DRAMs without external logic.

A wide range of DRAM configurations are possible for x 1, x 4 and x 8 bit wide DRAMs. Both Page mode and

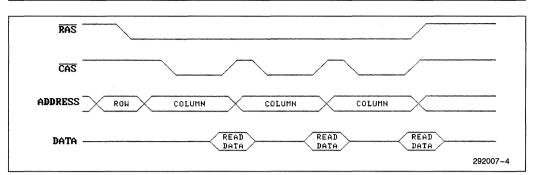

Fast-page-mode burst accesses for block transfers are supported directly by the 82786 to take advantage of the fast sequential addressing capability of DRAMs (see Figure 5). Once the DRAM is set-up with the row address, the column addresses can be quickly scanned in for several burst-accesses to the same page. With the 82786, fast-page-mode bursts for block transfers run at twice the speed of page mode.

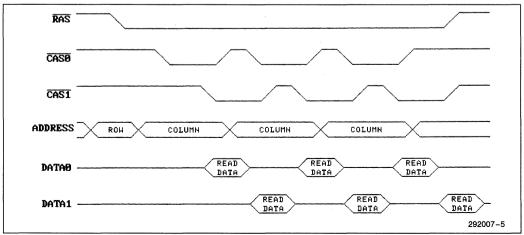

Interleaving of two banks of DRAMs is also supported directly by the 82786. For a sequential burst access, DRAM cycles for both banks can be initiated. Then, during the burst access, the 82786 can alternate accesses between the two banks, thus cutting the effective DRAM access time in half (see Figure 6).

Static Column DRAMs can also be used to get the same performance as fast-page-mode. The only difference between the two types is that Static Column DRAMs do not latch the column address, whereas, fast-page-mode DRAMs do latch the column address on the falling edge of CAS. In non-interleaved configurations, Static Column DRAMs can directly replace fast-page-mode. However, in an interleaved configuration, the column address must be latched externally for Static Column DRAMs. The following table shows the burst-access rate of these various configurations for a 10 MHz 82786.

|                  | Page Mode                  | Fast-page-mode<br>and Static Column |

|------------------|----------------------------|-------------------------------------|

| Non-interleaved: | 10 Mbyte/sec<br>(2 cycles) | 20 Mbyte/sec<br>(1 cycle)           |

| Interleaved:     | 20 Mbyte/sec<br>(1 cycle)  | 30 Mbyte/sec<br>(0.5 cycle)         |

The other cycle times, and speeds at 10 MHz, are the same for all DRAM configurations:

| Single Reads        | 3 cycles | 300 ns |

|---------------------|----------|--------|

| Single Writes       | 3 cycles | 300 ns |

| Read-Modify-Writes  | 4 cycles | 400 ns |

| Burst-Access Set-Up | 2 cycles | 200 ns |

| Refresh             | 3 cycles | 300 ns |

All burst-accesses for block transfers perform an even number of 16-bit word accesses.

Figure 6. Interleaved Fast-Page-Mode Burst-Access Read Cycle

Burst-accesses for block transfers are used by all Display Processor memory accesses except the operand for LD\_REG and DMP\_REG operands. Block-read accesses are used by the Graphics Processor for command-block fetching and to fetch the character fonts. The Graphics Processor uses a block-read followed by a block-write for the read-modify-write operations of BitBlt, Scan\_Line, and Character drawing. All other pixel drawing uses single read-modify-write cycles.

#### 3.1 DRAM Configurations

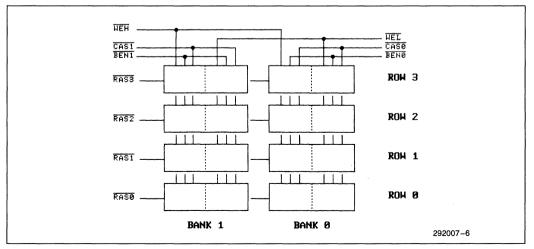

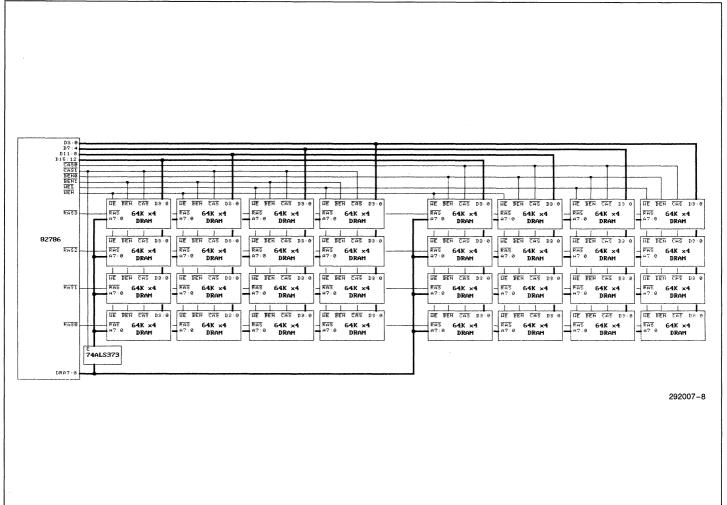

Up to 4 rows per bank, and 1 non-interleaved or 2 interleaved banks are supported (see Figure 7). Each bank must always be 16 bits wide. If only one non-interleaved bank is used, it must be bank 0 (using  $\overline{CASO}$  and  $\overline{BENO}$ ). If interleaving is used, both banks must have the same number of rows. In either case, if only one row is used, it must be row 0 (using  $\overline{RASO}$ ). For only two rows, row 0 and 1 are used ( $\overline{RASO}$  and  $\overline{RAS1}$ ). Similarly, three rows use row 0, 1, and 2.

The 82786 can directly drive up to 32 DRAM/VRAM chips. One 82786 pin shares two DRAM functions DRA9/RAS3. These functions are never both used in the same configuration. DRA9 is only used by 1M x 1 DRAMs, which limit the number of rows to only two due to both addressing (4 Megabytes) and drive (32 chips) limitations.

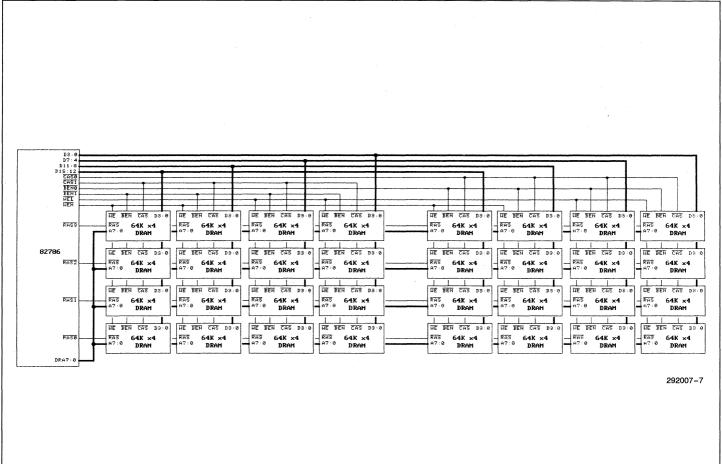

Figure 8 shows a full connection diagram for thirty-two 64K x 4 DRAMs. Two interleaved banks of four rows each are used. Unlike most DRAM/VRAM controllers, no impedance-matching resistors are usually needed between the 82786 chip and the DRAM/VRAM chips. The impedance-matching for most configurations is handled internally by the 82786. This is also the connections required for x4 VRAMs which use the  $\overline{\text{BEN}}$  signal to control their  $\overline{\text{DT}}/\overline{\text{OE}}$  input which is used to determine when to load their internal shift register (Figure 9).

If Static Column DRAMs are used in an interleaved configuration, an external latch is required to latch the column address for the second bank (Figure 8a). The 82786 can directly drive up to thirty-two DRAM devices. For configurations requiring more than thirty-two devices, external buffering must be used.

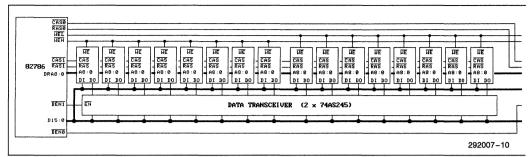

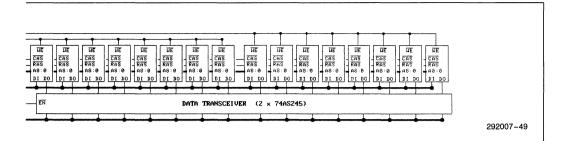

DRAMs with separate data-in and data-out pins (such as the x 1 DRAMs) require a tristate buffer for the data-out lines of each bank. (All of the rows within each bank may share the same tristate buffer). Figure 10 shows a full connection diagram for thirty-two 256K x 1 DRAMs including the tristate buffers. Two interleaved banks of one row each are used. This is a special case for the RAS lines. Normally RAS0 would drive all of the DRAMs in both banks for the one row as in Figure 7. However, because the RAS lines have drive capability for only 16 DRAMs, both RAS0 and RAS1 are used. The 82786 recognizes this special case and automatically drives RAS1 identically to RAS0.

The other special DRAM case is using two rows of x 1 DRAMs in a non-interleaved configuration. This configuration has the advantage that only one bank of transceivers is required, but burst access time is reduced by half from the previous example. Normally, CAS0 would be used to drive all 32 DRAMs, but because of drive limitations, both CAS0 and CAS1 are used, (one for each bank). Again the 82786 recognizes this special case and automatically drives CAS1 identically to CAS0.

Figure 7. 82786 Supports up to 4 Rows of 2 Interleaved Banks of DRAMs 64K x 4 Video RAMs with 82876 1 Row, 2 Banks, 4 Bits/Pixel

AP-270

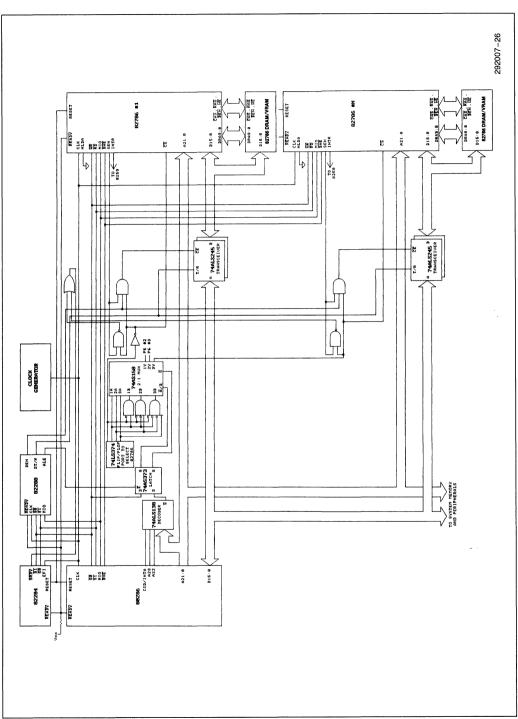

Figure 8. 82786 Driving 4 Rows of Two Interleaved Banks of 64K x 4 DRAMs

ത

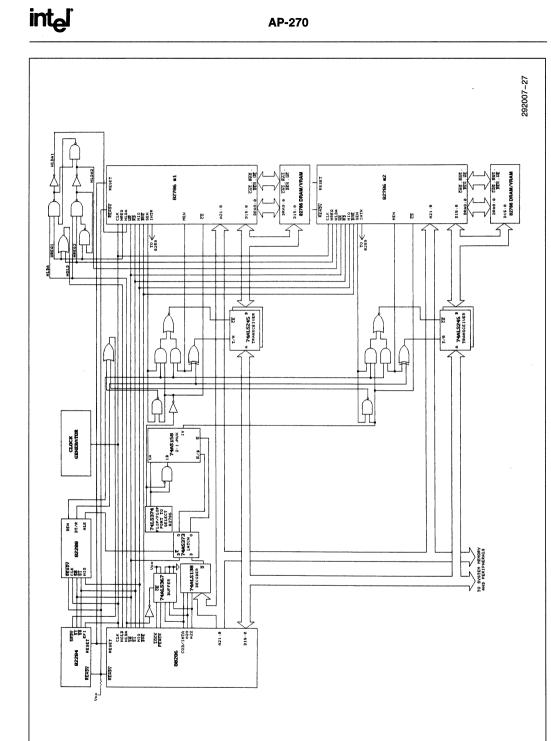

Figure 8a. 82786 Driving 4 Rows of Two Interleaved Banks of 64K x 4 Static Column DRAMs

4

AP-270

в

AP-270

int of

The table in Figure 11 shows all the possible configurations for 64K bit, 256K bit and 1 Mbit DRAMs.

#### 3.2 DRAM Timing Parameters

Care should be taken to ensure that all of the timings of the DRAMs used, fit with those in the 82786 data sheet. To make the comparisons easier, the names of the parameter in the 82786 data sheet exactly correspond to the names in most DRAM data sheets. In addition, the parameters have been broken into the same four groups used by most DRAM data sheets.

The critical parameters for page mode DRAMs are generally:

| Single<br>rd/wrt/RMW | Single wrt | RMW     | Page rd/wrt |

|----------------------|------------|---------|-------------|

| Tcac                 | Trwl       | Tds(rw) | Tds(i)      |

| Trp                  | Tcwl       | Toff    |             |

| Trcd                 |            |         |             |

| Trah                 |            |         |             |

| Tasc                 |            |         |             |

| Ton                  |            |         |             |

Some of the 82786 parameters may not be found in all page-mode data sheets. If no corresponding DRAM parameters for Tcaa or Tcar is specified, then the 82786 spec may be ignored. The reason is that, if no such DRAM parameters exists, then the resulting minimum values for these parameters are at most:

| Tcaa | = | Tasc | $^{+}$ | Tcac |

|------|---|------|--------|------|

| Tcar | = | Tasc | $^{+}$ | Trsh |

Then as long as the Tasc, Tcac, and Trsh specs fit, the 82786 timings guarantee Tcaa and Tcar to fit.

A third parameter that may not be found in all pagemode data sheets is Ton. If  $x \ 1$  DRAMs are used, the external data transceiver is responsible for meeting this and the DRAM is not required to meet this spec. If, however,  $x \ 4$  or  $x \ 8$  DRAMs are used, without the data transceiver, care must be taken to ensure that this spec is met. The critical parameters for Fast-page-mode and Static Column DRAMs are generally:

| Single<br>rd/wrt/RMW | Single wrt | RMW     | Fast-page-mode<br>rd/wrt |

|----------------------|------------|---------|--------------------------|

| Trp                  | Trwl       | Tds(rw) | Тср                      |

| Trah                 | Tcwl       | Toff    | Tcaa                     |

| Tasc                 |            |         | Тсар                     |

|                      |            |         | Tds(n)                   |

|                      |            |         | Tcah(i)                  |

|                      |            |         | Tds(i)                   |

|                      |            |         | Tdh(i)                   |

|                      |            |         | Ton(ri)                  |

For interleaved Static Column DRAMs, the address latch delay must be added to the DRAM parameters corresponding to the row and column addresses. These parameters are:

> — Tasr — Tasc — Tcaa

For all types of x1 DRAMs, page-mode, Fast-pagemode and Static Column, the transceiver delay must be added to the DRAM parameters which correspond to read-data. These parameters are:

| <br>Trac |

|----------|

| <br>Tcac |

| <br>Tcaa |

Notice that all of the 82786 DRAM timings are specified relative to the bus clock (CLK). This has two implications. First, a slower bus clock can be used to allow the 82786 to use slower DRAMs. Secondly, many of the parameters are determined by the duty cycle of the bus clock (as their specification is dependent on clock high or low time). A slightly non-symmetric clock, such as the clock for the 80286, can be used for the 82786 CLK, but care should be taken to examine the effects on the DRAM timing. In some circumstances, it may be advantageous to use a slightly nonsymmetric clock.

Some of the specifications are relative to the 82786 clock period (Tc), while others are relative to a specific phase (THigh, TLow).

|          | Non-Interleaved |          |        |        | Interleaved |        |        |        |

|----------|-----------------|----------|--------|--------|-------------|--------|--------|--------|

|          | 1-row           | 2-rows   | 3-rows | 4-rows | 1-row       | 2-rows | 3-rows | 4-rows |

| 64K x1   | 128K            | 256K     | 384K   | 512K   | 256K        | 512K   | 768K   | 1024K  |

|          | 16              | 32       | 48*    | 64*    | 32          | 64*    | 96*    | 128*   |

| 16K x4   | 32K             | 64K      | 96K    | 128K   | 64K         | 128K   | 192K   | 256K   |

|          | 4               | 8        | 12     | 16     | 8           | 16     | 24     | 32     |

| 8K x8    | 16K             | 32K      | 48K    | 64K    | 32K         | 64K    | 96K    | 128K   |

|          | 2               | 4        | 6      | 8      | 4           | 8      | 12     | 16     |

|          |                 |          |        |        |             |        |        |        |

| 256K x 1 | 512K            | 1024K    | 1536K  | 2048K  | 1024K       | 2048K  | 3072K  | 4096K  |

|          | 16              | 32       | 48*    | 64*    | 32          | 64*    | 96*    | 128*   |

| 64K x4   | 128K            | 256K     | 384K   | 512K   | 256K        | 512K   | 768K   | 1M     |

|          | 4               | 8        | 12     | 16     | 8           | 16     | 24     | 32     |

| 32K x8   | 64K             | 128K     | 192K   | 256K   | 128K        | 256K   | 384K   | 512K   |

|          | 2               | 4        | 6      | 8      | 4           | 8      | 12     | 16     |

|          |                 |          |        |        |             |        |        |        |

| 1M x1    | 2M<br>16        | 4M<br>32 | _      |        | 4M<br>32    |        |        | _      |

| 256K x4  | 512K            | 1M       | 1.5M   | 2M     | 1M          | 2M     | 3M     | 4M     |

|          | 4               | 8        | 12     | 16     | 8           | 16     | 24     | 32     |

| 128K x8  | 256K            | 512K     | 768K   | 1M     | 512K        | 1M     | 1.5M   | 2M     |

Figure 10. Two Interleaved Banks of 256K x 1 DRAMs

Figure 11. Possible DRAM configurations for 64K, 256K and 1 Mbit DRAMs. The top number in each box is total memory size in bytes, the bottom is the number of DRAM chips required.

Look at this example. Suppose you use 51C256H Fastpage-mode DRAMs with the 82786 as in Figure 10. First, look at the critical parameters shown above. Since it is not possible to create a precisely 50% duty cycle clock, you must consider clocks with a few percent tolerance. The table compares the 82786 using several clock frequencies and duty cycle tolerances with two versions of the 51C256H. The table is ordered with the tightest timings first. From the table, you can see that the fast 120 ns access DRAMs can be used with the 82786 with a 10 MHz clock with as much as a 40%-60% duty cycle skew. The slower DRAMs can be used at 9 MHz with a tighter 45%-55% duty cycle skew or at 8 MHz with a 40%-60% skew.

| Paran | neter |          | 8278             | 51C256H D        | RAM Specs       |                 |                |                |

|-------|-------|----------|------------------|------------------|-----------------|-----------------|----------------|----------------|

|       |       |          | 10 MHz<br>45-55% | 10 MHz<br>40-60% | 9 MHz<br>45-55% | 8 MHz<br>40–60% | — 12<br>120 ns | — 15<br>150 ns |

| Tdh   | Min   | Tph      | 22.5             | 20               | 25              | 25              | 20             | 25             |

| Toff  | Max   | T1 + 3   | 25.5             | 23               | 28              | 28              | 20             | 25             |

| Tcah  | Min   | Tch + 2  | 26.5             | 22               | 24.5            | 27              | 15             | 20             |

| Тср   | Min   | Tcl – 5  | 17.5             | 15               | 20              | 20              | 10             | 10             |

| Tds   | Min   | Tcl — 8  | 14.5             | 12               | 17              | 17              | 0              | 0              |

| Тсаа  | Max   | 2Tc – 27 | 73               | 73               | 83              | 98              | 55             | 70             |

| Тсар  | Max   | 2Tc - 21 | 79               | 79               | 89              | 104             | 60             | 75             |

| Tasc  | Min   | Tcl – 5  | 17.5             | 15               | 17.5            | 17.5            | 5              | 5              |

| Trp   | Min   | 2Tc – 5  | 95               | 95               | 105             | 120             | 70             | 85             |

| Trwl  | Min   | Tc — 9   | 41               | 41               | 46              | 53.5            | 25             | 30             |

| Tcwl  | Min   | Tc – 12  | 38               | 38               | 43              | 50.5            | 25             | 30             |

| Trah  | Min   | Tc + 3   | 53               | 53               | 58              | 65.5            | 15             | 20             |

| Ton   | Max   | Tc – 24  | 26               | 26               | 31              | 38.5            | 25             | 30             |

Figure 10. Two Interleaved Banks of 256K x 1 DRAMs (Continued)

Because these x 1 DRAMs require transceivers between their data outputs and the 82786, the transceiver delays must also be considered. The two parameters in the table above, that are affected are Tcaa and Tcap. The transceiver delay must be added to the DRAM access time for these parameters. This implies that the data-in to data-out time of the transceivers must be 18 ns or less for the 10 MHz-120 ns case and the 8 MHz-150 ns case. The delay must be 28 ns or less for the 9 MHz-150 ns case and the 8 MHz-150 ns case.

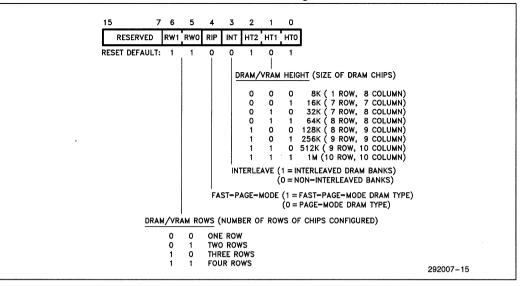

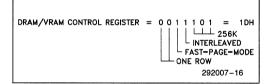

#### 3.3 Initializing the DRAM Controller

Two of the 82786 Internal Registers are used to configure the DRAM/VRAM Controller. Both of the registers are typically set once during initialization and then never changed. The DRAM/VRAM Control Register is set to indicate the configuration of the DRAMs/ VRAMs used. The DRAM/VRAM Refresh Control Register is set to indicate the frequency of refresh cycles. Once programmed, the settings can be write-protected using the write-protect bits discussed in Section 4.2.

It is recommended that all fields of the DRAM/ VRAM Control Register be written simultaneously to avoid illegal combinations. Also, no DRAM accesses should be attempted until the DRAM/VRAM Control Register has been set. For the configuration in Figure 10 using one row of 256K Fast-page-mode DRAMs in two interleaved banks:

#### DRAM/VRAM Control - Internal Register Offset 08h

DRAM/VRAM Refresh Control—Internal Register Offset 06H

| 15             | 6 | 5 | 4   | 3    | 2  | 1    | 0 |

|----------------|---|---|-----|------|----|------|---|

| Reserved       |   |   | Ref | rest | Sc | alar |   |

| RESET Default: |   | 0 | 1   | 0    | 0  | 1    | 0 |

The 82786 CLK input is internally divided by 16 and then divided by the refresh scalar + 1 in the DRAM/ VRAM Refresh Control Register to determine the time between refresh cycles. Only one row of each DRAM/ VRAM is refreshed at a time so refresh of the entire DRAM/VRAM requires 128, 256, 512 or 1024 of these refresh cycles depending on the number of rows in the DRAM/VRAM.

For example, the 51C256H DRAMs require a complete refresh every 4 ms (Tref). These DRAMs consist of 512 address rows of 512 address columns. However, for refresh purposes, only 256 row addresses (A0–A7) need to be refreshed within the 4 ms refresh time. The A8 input is not used for refresh cycles. (The 82786 maintains a full 10-bit refresh address, the upper 2 bits are simply not used in this configuration). Assuming a 10

MHz 82786 CLK, we can determine the value for the DRAM/VRAM Refresh Control register as follows:

Refresh Count =

$$\frac{\text{Tref} \times \text{CLK}}{16 \times \text{Refresh} \text{Rows}} - 1$$

=  $\frac{4 \text{ ms} \times 20 \text{ MHz}}{16 \times 256} - 1 = 18.53$

The result should always be rounded down, so the DRAM/VRAM Refresh Control Register should be programmed with 18. This result is dependent only on the DRAM/VRAM type and the 82786 CLK frequency. The configuration of the DRAM/VRAM chips does not matter.

There is a latency time between the refresh request generated by this count and the actual refresh cycle. The refresh will always occur as soon as the current bus cycle finishes. Refresh cycles can interrupt block transfers, but only at double-word boundaries. The worst case is if a refresh request occurs just after the 82786 receives HLDA to begin a master-mode block transfer. The 82786 must complete two master cycles before the refresh cycles can be performed. During this latency, further refresh requests may be generated. The 82786 contains a refresh request queue that allows up to three refresh requests to be pending. As soon as the bus is freed, all queued refresh cycles will be run consecutively.

For the above example, refresh requests are generated every 15.2  $\mu$ s.

$Request\_time = \frac{16 \times (RefreshCount + 1)}{CLK}$

$$=\frac{16\times(18\,+\,1)}{20\,\text{MHz}}=\,15.2\,\,\mu\text{s}$$

The amount of latency that the DRAMs will tolerate for each row is:

Allowed\_Latency=Tref-(RequestTime

$$\times$$

Refresh\_

Rows)

=4 ms-(15.2  $\mu$ s  $\times$  256)=108.8  $\mu$ s

But the real latency limit is that the 82786 allows only three requests to be queued:

Therefore, the maximum number of wait-states allowed for a 82786 master mode transfer is:

Clearly, in this situation, refresh latency is not a problem. If the system memory caused the 82786 to delay over 224 wait-states for a master-mode access, not only would DRAM/VRAM refresh be missed, but the display refresh would also be lost.

The 82786 always issues three refresh cycles following a RESET. Besides these first three refresh cycles, the 82786 does not perform any other DRAM/VRAM warm-up after cold or warm-reset. If the DRAMs/VRAMs require other warm-up cycles, the CPU should either perform dummy cycles to the DRAM/VRAM or wait until the refresh counter has requested enough refresh cycles to occur.

If the DRAM/VRAM Refresh Control Register is set to all ones, refresh cycles are disabled.

#### 4.0 SYSTEM BUS INTERFACE

The 82786 system bus structure allows the 82786 to be easily connected to a variety of CPUs. The 82786 can act as both a slave and a master to the CPU's bus. As a slave, the CPU or DMA can perform read and write cycles to the 82786 internal registers or to the 82786 DRAM/VRAM. As a master, the 82786 Graphics and Display Processors can perform read and write cycles to the CPU's system memory.

The 82786 bus can operate in three different modes to handle various CPU interfaces. The 82786 determines which mode to use by sampling the  $\overline{BHE}$  and MIO pins during RESET:

|                       | BHE | MIO |

|-----------------------|-----|-----|

| Synchronous 80286 bus | 1   | 0   |

| Synchronous 80186 bus | 1   | 1   |

| Asynchronous bus      | 0   | Х   |

For synchronous 80286 interfaces, the Reset and Clock inputs into the 80286 and 82786 must be common. For synchronous interfaces to 80186, the 80186 CLKIN must be the same as the 82786 CLK (so external clock source must be used). The RES input into the 80186 must meet a set up and hold time with respect to the CLKIN. The RESET for the 82786 should be generated from the RES (for 80186) by delaying RES by one CLKIN cycle and inverting it. This ensures that the 82786 ph1 is coincident with 80186 CLKOUT low.

These pin states are easy to achieve for the synchronous modes. During RESET, the 80286 always drives  $\overline{BHE}$  high and MIO low.

CPUs with timings different from the 80286 must use asynchronous mode (however, CPUs such as the 80386 can easily generate 80286 style timings). Care should be taken in this case to ensure BHE is low during RESET.

In each of these three modes it is possible to configure the 82786 to allow both master and slave accesses or to simplify the logic to allow only slave access. In the master mode, the 82786 always generates 80286 style bus signals.

If the 82786 is used as a master, it will activate its HREQ line when it needs to become the system master to access system memory. It waits until HLDA is received and then begins driving the system bus. Once HLDA is received, a 10 MHz 82786 can perform system bus accesses at the following rate (assuming 0 wait-states).

| single reads/writes     | 4 cycles | 5 Mbyte/sec   |

|-------------------------|----------|---------------|

| read-modify-writes      | 6 cycles | 3.3 Mbyte/sec |

| burst-access read/write | 2 cycles | 10 Mbyte/sec  |

The 82786 will begin the first master-mode bus access on the cycle after HLDA is activated. The only delay is the time between when the 82786 activates HREQ and the system can release the bus and return HLDA. Most synchronous CPUs require a minimum of three cycles between the time HOLD is activated until they can return HLDA. The 82786 will keep HREQ activated until it no longer has more accesses to perform to system memory. (Until either the next 82786 access is to the dedicated graphics DRAM/VRAM or until neither the Graphics or Display Processors require the bus.) Once the 82786 is done using the system bus, it will remove HREQ and is able to immediately access its Graphics DRAM/VRAM on the next cycle. It is potentially possible for the 82786 to require the system bus for a lengthy period of time. For example, if the 82786 has been programmed to give the Graphics Processor high priority, and the Graphics Processor executes a command that requires a lot of access to system memory, then the system bus could potentially be held by the 82786 for several consecutive accesses. Drawing a long vector into a bit-map residing in system memory is such a command. In this case, the maximum time the 82786 can potentially keep the system bus is determined by the frequency of DRAM/VRAM refresh cycles programmed into DRAM/VRAM Refresh Control Register.

If the CPU needs to regain control of the bus before the 82786 is done, it may remove HLDA early. The 82786 will then complete the current access and remove HREQ to indicate to the CPU that it may now takeover control of the bus. If the 82786 still requires more access to the system bus, it will re-activate HREQ two cycles after it had removed it and wait until the next HLDA. Since the 82786 removes HREO for only two cycles, it is important that the CPU recognize it immediately. Otherwise a lock-out condition will occur in which the CPU is waiting for the 82786 to remove HREQ and the 82786 is waiting for the CPU to issue HLDA. This is not a problem for the synchronous interfaces. Extra logic may be required to prevent this situation if the 82786 is used as a master in an asynchronous interface and HLDA is ever removed prematurely, especially if the CPU clock is significantly slower than the 82786 clock.

#### 4.1 Memory Map

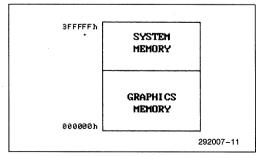

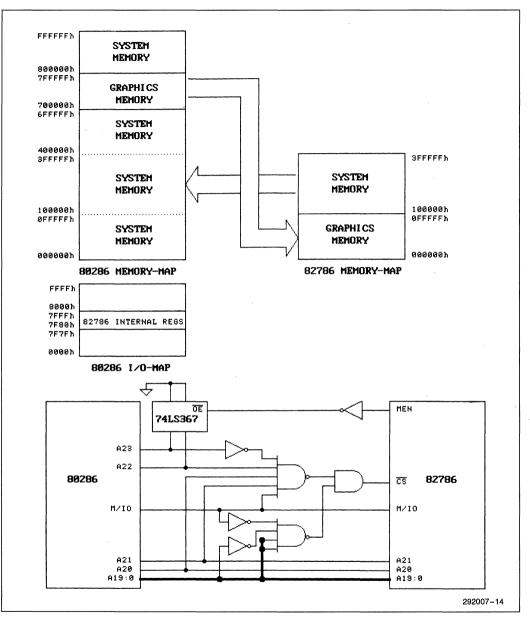

Figure 12 shows the memory map as it appears to both the 82786 Graphics and Display Processors. These processors both use a 22-bit address which provides for up to 4 Megabytes of address space. They are only allowed to make memory accesses so no I/O map is applicable.

Figure 13. Memory Map for System CPU

The 82786 dedicated graphics DRAM/VRAM always starts at location 000000h and grows upwards. The upper address depends on the amount of DRAM/VRAM memory configured. The system bus memory begins where the DRAM/VRAM ends and continues to the highest addressable memory location 3FFFFFh.

The memory map as it appears to the system CPU is shown in Figure 13. The area that the 82786 Graphics DRAM/VRAM is mapped into can be anywhere in the CPU address space and is completely defined by the address decode logic of the CPU system. Normally only the space for the configured graphics memory is mapped into CPU address space. If addresses above the configured graphics memory are mapped into the CPU address space, and the CPU writes to addresses above the configured 82786 memory, the write will be ignored. If it reads from these locations, the data returned is undefined.

The 82786 internal registers may be configured to reside in memory or I/O address space. If configured to reside in memory, then they will override a 128 byte area of the 82786 memory address space for external (CPU) accesses. The internal registers are only accessible by the external CPU and therefore are never found in the 82786 Graphics or Display Processor memory maps.

Suppose the 82786 is configured with 1 Megabyte of Graphics DRAM/VRAM and is used in an 80286 system. A possible memory map and connection diagram is shown in Figure 14. All of the 82786 memory is mapped into the 80286 address space. Also, a 3 Megabyte portion of the 80286 system memory is mapped into the 82786. Since the 80286 has two more address bits than the 82786, a tristate buffer is used to supply the top two address bits when 82786 enters master mode.

Figure 14. Possible Memory Mapping for 80286/82786 82786 Internal Registers are Memory Mapped

Notice that the same memory corresponds to one set of memory addresses for the CPU and a different set of memory address for the 82786 Graphics and Display Processors. Although it is possible to make these addresses match, it is not necessary as long as the controlling CPU software understands the relationship and makes the simple conversion. Often it is not desirable to make the addresses match. For example, most CPUs use the lowest memory addresses for special purposes, such as for interrupt vectors. If the lowest CPU memory were 82786 memory rather than the faster (for CPU access) system memory, then these operations would execute significantly slower.

Even though the real addresses don't match, the operating system for a CPU such as the 80286 could make the CPUs virtual addresses map easily to the 82786 real addresses. The 82786 internal registers may either be memory or I/O mapped. If they are memory mapped over the Graphics DRAM/VRAM, the CPU will not be able to access the 128-bytes of DRAM/VRAM which they cover, (although the Graphics and Display Processors can). If they are memory mapped above the Graphics DRAM/VRAM (over non-configured memory), then they will not prevent the CPU from accessing any of the 82786 memory, but they must be included in the CPU memory space that the address decoder allocates for the 82786. The 82786 internal registers may be I/O mapped, so they do not overlap any memory, however the CPU chip select logic for the 82786 becomes slightly larger. Figure 15 shows a circuit similar to Figure 14, except the registers are I/O mapped. Memory mapping the internal registers allows the software slightly more flexibility in accessing the registers.

Figure 15. Possible Memory Mapping for 80286/82786 82786 Internal Registers are I/O Mapped

intel

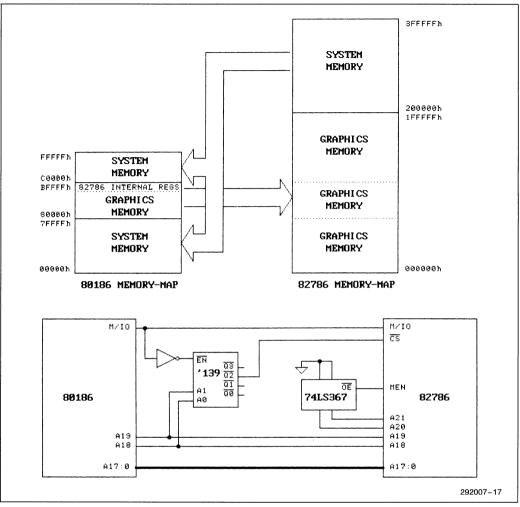

Figure 16. Possible Memory Mapping for 80186/82786

Because graphics memory can be quite large, some system designs might not allow all of the configured Graphics DRAM/VRAM to be directly mapped by the CPU. For example, if the 82786 has 2 Megabytes of Graphics DRAM/VRAM and is used with a 80186 processor, which can only address 1 Megabyte, then the 80186 can not directly access all of the 82786 memory. In this case the CPU can be permitted to only access a portion of the Graphics DRAM/VRAM. Figure 16 shows a memory map and connection diagram for such a system. Since the 82786 has two more address bits than the 80186, a tristate buffer is used to supply the two highest address bits when the 82786 is in slave mode.

In many cases the CPU does not require access to all of the graphics memory. For example, many situations will not require the CPU to directly access the bitmaps. If the CPU must gain access to the Graphics memory which is not directly mapped to the CPU, the 82786 Graphics Processor can be instructed (using the BitBlt command) to move portions of the Graphics memory to and from the area accessible by the CPU.

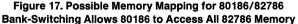

Alternatively, the Graphics DRAM/VRAM areas can be bank switched to allow the CPU direct access at any portion of the graphics memory. Figure 17 shows the use of an I/O port (74LS173 latch) to which the CPU can write the highest 3 bits of the address for the 82786 slave accesses.

In both Figures 16 and 17, it is possible for the 82786 in master-mode to access the CPU memory addresses that

intel

correspond to the 82786 slave addresses. In this case, the circuit will generate a 82786 chip-select, but the 82786 will not respond to this chip-select while it remains in master-mode. As long as the READY logic goes high (it may not since the 82786 will not perform the slave-access) then the 82786 will complete the master-mode cycle. By the time the 82786 returns to slavemode, the chip-select will have gone away.

#### 4.2 BIU Registers

Within the 82786 internal register block, the registers at offsets 00h–0Fh are used by the Bus interface Unit to

control the system configuration (Figure 4). These registers are normally set once during power-up intialization and never changed.

Two of these registers, DRAM/VRAM Refresh Control and DRAM/VRAM Control have already been discussed in Section 3.3. The rest of the registers are discussed in this section.

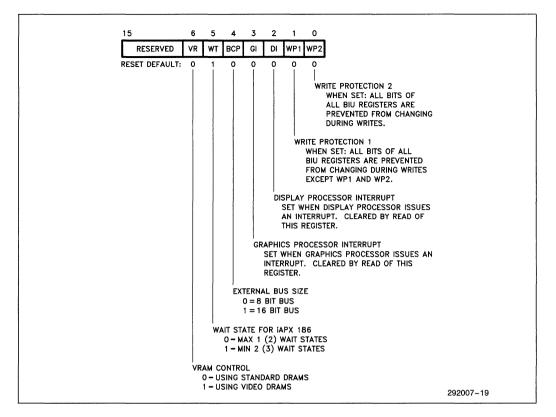

The Internal Relocation Register is used to locate the 82786 internal registers anywhere in the 82786 memory or I/O address space.

Internal Relocation - Internal Register Offset 00h

Base Address: determines bits 21:7 of internal register address (bits 6:0 of address are used as offset)

0 = I/O mapped

1 = memory mapped

After RESET, any CPU slave I/O address to the 82786 (which activates the 82786 Chip-Select) will access the internal register block. During initialization, a write to the Internal Relocation Register should be performed to locate the register at the specific memory or I/O address desired. Once the write to the Internal Relocation Register occurs, the 82786 internal register block no longer occupies all of 82786 I/O space, rather it is restricted to just the 128 memory or I/O bytes specified. The internal registers can be located anywhere accessible by the CPU, however, if they are memorymapped and located over configured graphics memory, they will take precedence over the memory for CPU accesses to those addresses. Graphics or Display Processor accesses to these addresses will still be directed to DRAM/VRAM. For example, writing the value of 03F8h locates the internal registers at I/O addresses FE00h – FE7Fh.

$03F8h = 00\ 0000\ 1111\ 1110\ 0$ 0 I/O mapped Base Address 00FE00h(offsets 0-7Fh)

Note that the address written to the Internal Relocation Register determines the memory or I/O address that is required to be placed on the 82786 address pins during a CPU access to the 82786 internal registers. The actual CPU address used may be different, and is dependent on the chip select and memory mapping logic described in Section 4.1.

There are four sources of requests for the 82786 bus:

- DRAM/VRAM refresh

- Display Processor

- Graphics Processor

- External Processor (CPU or DMA slave accesses)

The DRAM/VRAM refresh requests are always top priority. That is, once the DRAM/VRAM refresh request is made, the 82786 bus will complete the current bus access and then perform the DRAM/VRAM refresh. Three BIU registers are used to set the priorities of the other three bus requests. Two priority values are used:

FPL - First Priority Level - priority used when processor first requests bus.

SPL - Subsequent Priority Level - priority used for processor to maintain bus during a block transfer. If a block transfer is interrupted, this is also the priority used for regain bus to complete the burst access.

When a processor first requests the 82786 bus, its FPL value is used. The processor with the highest priority gets access to the bus. Once the bus is granted, the first access occurs. If a multiple-word block transfer is performed the SPL value is then used as the priority to maintain the bus for subsequent cycles. As long as no other processor of higher priority requests the bus, the burst-access is allowed to continue to completion. If a higher priority request is made, the block transfer will be suspended and the bus granted to the new request. The suspended block transfer will not get the bus back until its SPL value is again the highest priority request.

A separate register is used to program the priority for each of the three processors. Because the External Processor can not perform block transfers, no External SPL value is required for it.

| Display Priority - Internal Register Offset 0Ah  |      |      |      |      |       |       |   |

|--------------------------------------------------|------|------|------|------|-------|-------|---|

| 15                                               | 6    | 5    | 4    | З    | 2     | 1     | 0 |

| Reserved                                         |      | É    | ۶P   | L    |       | SPL   |   |

| RESET Default:                                   |      | 1    | 1    | 0    | 0     | 1     | 1 |

|                                                  |      |      |      |      |       |       |   |

| Graphics Priority - In                           | tern | al F | legi | ster | Offse | t 0Ch |   |

| 15                                               | 6    | 5    | 4    | З    | 2     | 1     | 0 |

| Reserved                                         |      | F    | P    | L    |       | SPL   |   |

| RESET Default:                                   |      | 1    | 0    | 1    | 0     | 1     | 0 |

|                                                  |      |      |      |      |       |       |   |

| External Priority - Internal Register Offset 0Eh |      |      |      |      |       |       |   |

| 15                                               | 6    | 5    | 4    | 3    | 2     | 1     | 0 |

|                                                  |      |      |      |      |       |       |   |

| Reserved       | F | ۶P | L | Reserved |

|----------------|---|----|---|----------|

| RESET Default: | 1 | 1  | 1 |          |

All of the priorities are programmable values from 0 to 7 with 7 being the highest priority. If two processors that are programmed with the same priority both request the bus, the priority in which the bus will be granted for the two will be (from highest to lowest):

- Display Processor

- Graphics Processor

- External Processor

There are two exceptions to these programmable priorities. If the CPU makes a slave request while one of the 82786 processors makes a master request, the CPU's request will always be handled first by the 82786 regardless of priority settings. This is necessary to prevent the lock-out situation where the CPU will not grant HLDA until it completes the bus access to the 82786 and the 82786 will not complete the CPU bus cycle until the higher priority master cycle completes. Refresh cycles also always will be handled while the 82786 is in a HLDA loop.

The values programmed into these priority registers should be selected carefully. There is a performance penalty whenever a block transfer is interrupted. However, if block transfers are not interrupted, then it is possible that one processor must wait a long time to get the bus while another is finishing. A balance between overall bus performance and maximum tolerable latency must be made.

For example, if the Display Processor is not given high enough priority, it may not always be able to fetch the bit-mapped display data fast enough to keep up with the CRT. When this happens, the Display Processor will not be able to send the correct video data to the CRT and will instead place the value in the Default-VDATA register on the VDATA pins. To prevent this "snow" on the display, the Display Processor can be programmed for the highest priority (after DRAM/ VRAM refresh).

The Display Processor internally contains a FIFO which is used to buffer the bit-map data to be displayed. The FIFO consists of 32-double-words of 32 bits each. Each FIFO double-word contains the results of a 32-bit fetch from the bit-map memory. A double-word can therefore contain as many as 32 pixels, or as few as 1 pixel (such as at window borders).

Display Processor Register 2 (TripPt) controls when this FIFO is loaded. If the trip point is set at 16, the Display Processor waits until the FIFO is half empty (only 16 double-words left) before it requests a new block transfer to refill the FIFO. The block transfer request will not end until the FIFO is again full (although the block transfer may be interrupted by a higher priority request). If the trip point is set at 28, the Display Processor will begin requesting a new block transfer after only 4 FIFO double-words are emptied (28 left remaining). A low trip point generates fewer but longer block transfers and therefore the overall Display Processor bus efficiency is increased. However, a low trip point also requires that the bus latency be smaller. A low trip point means that there are less double-words left in the FIFO when the bus request is

made. If the FIFO drains completely before the bus has been granted, then the DefaultVDATA will be used from the current pixel through the end of the current scan line. The trip point may be programmed to 16, 20, 24, or 28 using the Display Processor LD\_REG or LD\_ALL commands.

The Display Processor also keeps busy during blank times. During Vertical Blank time it performs any command loaded into its Opcode Register. During Horizontal Blank time it loads a new Strip Descriptor if necessary and begins fetching the first pixels on the line. (Actually, the descriptor fetch begins as soon as the last pixel of the last line has been placed in the FIFO). If the Display Processor priority is not high enough to allow these fetches during blank time, then again part of the display can not be generated correctly and Field Color will be used. Two bits in the Display Processor Status Register can be used to determine if the Display Processor ever gets behind:

- bit-5 DOV Descriptor Overrun set if strip descriptor fetch has ever not completed by the time horizontal blanking ends.

- bit-4 FMT FIFO Empty set if the Display FIFO has ever completely drained.

Both bits are reset after reading the Status Register.

The setting of the External Priority register can greatly affect the performance of the external CPU when it performs an access to the 82786. Unless the External Priority is greater than the Graphics Processor, whenever the Graphics Processor is busy with a command stream that demands significant bus bandwidth, the CPU may have to wait a significant amount of time before it can complete an access to the 82786. The CPU waits for the 82786 in the middle of a bus access until the 82786 returns the READY signal. During this wait time, the CPU will not be able to process anything, including interrupts. Of course, if the application is very Graphics intensive and the CPU throughput is of lesser concern, then the Graphics Processor can be programmed with a higher priority.

Use the following priority values during your initial design. Once the system is working properly, you may wish to tweak the values for optimum performance. The optimum values are dependent on the CPU and video speeds as well as the CPU and graphics instruction mix and the window arrangement. In most cases, these registers will be initialized once and never changed. It may, however, be advantageous in some specialized applications to adjust these values when the application changes modes.

|                    | FPL | SPL |

|--------------------|-----|-----|

| Display Processor  | 6   | 6   |

| Graphics Processor | 2   | 2   |

| External Processor | 4   |     |

| Trip Point         |     | 24  |

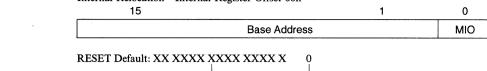

One final BIU register contains a miscellaney of bits.

After the BIU registers have been initialized, the WP1 and WP2 bits can be used to protect all of the BIU registers (82786 internal register offsets 00h - 0Fh) from being rewritten. This will prevent faulty software from going wild and placing the 82786 into an unwanted state. Once WP1 is set, the only way to change the BIU registers is to reset WP1 first. Once WP2 is set, there is no way for the software to modify the BIU registers until a 82786 hardware RESET is performed.

After the 82786 causes an interrupt, the GI and DI interrupt bits are used to allow the software to determine whether the Graphics or Display Processor caused the interrupt. It is possible that both of these bits may be set if both processors have caused an interrupt by the time the interrupt handler reads this register. In this case, both interrupts should be handled by the interrupt handler.

Although it is not absolutely necessary to allow the 82786 to interrupt the CPU, it is very desirable. Graphics Processor interrupts can inform the software when it has completed all the commands as well as to report

error conditions. Display Processor interrupts can inform the software when a new display field has begun. A new command can then be loaded into the Display Processor to be executed before the next display field. This facilitates operations such as smooth scrolling and blinking. The only hardware requirement to permit 82786 interrupts is that the 82786 INTR pin is tied to one of the interrupt controller inputs.

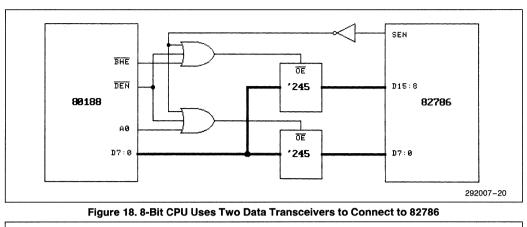

Although the 82786 always uses 16 bits, the 82786 can be used with both 8 and 16 bit processors. For an 8-bit CPU, separate transceivers are required for the low and high bytes to the 82786 (Figure 18). In both 8 and 16 bit modes, graphics memory may be accessed a byte at a time. Although the 82786 internal registers may be read a byte at a time, they all are considered to be 16 bits (even if some of the bits aren't used) and must always be written in 2-byte even-word pairs. In 16-bit mode, they must be written as a 16-bit word. In 8-bit mode, first the lower (even-address) byte is written and then the upper (odd-address) byte is written. With an 8bit processor such as the 8088, both of the following assembly routines may be used to load the 16-bit BI-UControl Register with AX.

```

mov dx,BIUControl

out dx,al ;write AL into low-byte of BIUControl

mov al,ah

inc dx

out dx,al ;write AH into high-byte of BIUControl

or:

mov dx,BIUControl

out dx,ax ;write AX into BIUControl word

```

In 8-bit mode, an even-byte write to a 82786 internal register does not change any of the 82786 internal registers, the data is simply saved until an odd-byte write to a 82786 internal register is performed. Then both the high and low bytes are written into that register. In effect, the even-byte address is ignored and an odd-byte write will write into the register both the odd-byte data and whatever even byte data was last written, into the register address specified by the odd-byte access. There is no limit to the amount of time allowed between the even-byte and corresponding odd-byte writes. An odd-byte write that is not preceded by an even-byte will be ignored.

The 82786 always comes up in 8-bit mode after RESET. This means that a 16-bit CPU should change the BCP bit to one. It must perform two byte-wide accesses to do this. The following initialization code can be used.

```

mov dx,BIUControl

mov al,30h

out dx,al ;write 30h into low-byte of BIUControl

xor al,al

inc dx

out dx,al ;write 00h into high-byte of BIUControl

mov dx,InternalRelocation

mov ax,03F8h

out dx,ax ;write 03F8h into InternalRelocation word

```

The 82786 is first placed in 16-bit mode (using two 8-bit writes), then the 82786 internal registers are located at the desired address (which is done with a 16-bit write). Next, the DRAM/VRAM and priority registers should be initialized. Byte-wide writes into the 82786 internal registers can not be performed while BCP = 1.

All the 82786 master mode operations are 16 bits wide independent of the BCP bit. This means that system memory must be accessible 16-bits at a time if master mode is to be used. The WT bit is set to 1 on reset. The VR bit is reset to 0 at reset.

#### 4.3 80286 Synchronous Interface

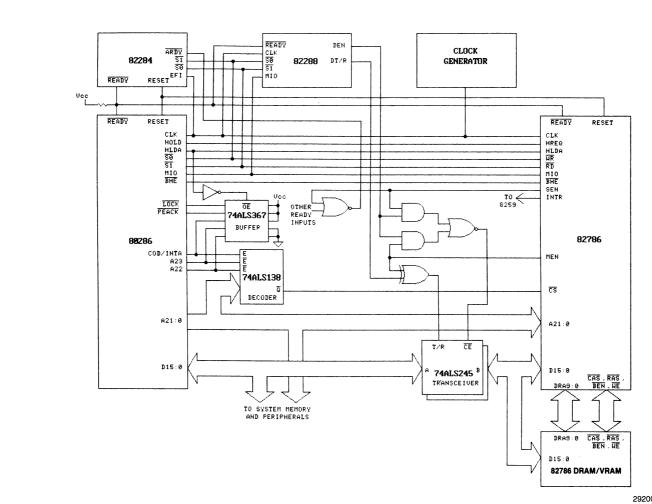

Since the 82786 has been optimized for the 80286, it is not surprising that the interface logic is very minimal. Figure 19 shows a 82786 connected synchronously to an 80286. Much of the logic, such as the 82288, chip-select, and ready, can be shared by the rest of the 80286 system.

This configuration allows both master and slave accesses. The data transceivers allow the 80286 to access the 82786 and graphics memory and the 82786 to access the 80286 system memory. They also provide the isolation required to allow the 80286 to access system memory while the 82786 accesses graphics memory simultaneously. The tristate buffer 74LS367 is used to pull the 80286 upper address lines, COD/INTA, LOCK and PEACK to their proper states during master-mode. If any of these signals are not used by the rest of the system, they need not be driven by a tristate buffer.

If master mode is not required, MEN will stay low and three of the four gates driving the data transceivers can be eliminated. Also, the tristate buffer, which is only used in master-mode, may be eliminated. HREQ should be left open and the 82786 HLDA pin should be tied to ground so that the 82786 will never enter master mode.

Both the 80286 and the 82786 internally divide-by-two the CLK input and use both phases. For the 82786 to run correctly with the 80286, these phases must be correlated correctly. This can easily be done by observing the setup and hold times for rising RESET for both chips (see 80286 data sheet specifications 6 and 7 and 82786 data sheet specifications C6 and C7). The 82284 chip will meet this requirement.

Depending on the CLK speed and the type of DRAM/ VRAM used, the 82786 may have very stringent CLK duty cycle requirements (see Section 3.2). It may not be possible to use the internal oscillator of the 82284 chip but it may be possible to use an external oscillator to drive the 82284 external clock (EFI) pin.

Clock skew between the 80286 and the 82786 should be kept to a minimum so the chips should be placed as close together as possible.

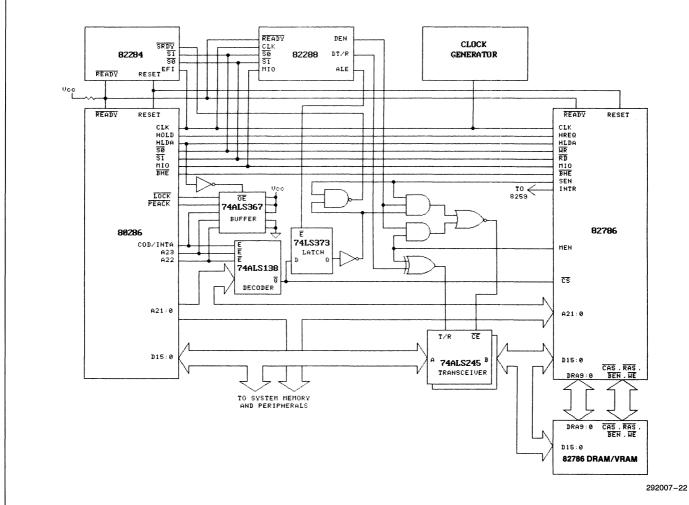

When the 82786 bus is free, the circuit in Figure 19 permits CPU slave accesses using 2 wait-states for writes and 3 wait-states for reads. Using DRAMs/ VRAM with slightly faster access times, the circuit in Figure 20 permits both read and write slave accesses using 2 wait-states. The 82284 SRDY input is used instead of ARDY. The 82786 SEN timing is such that a minimum of 2-wait states are always generated for writes but a minimum of 2 or 3 wait-states are used for reads depending on the use of SRDY or ARDY. Notice that with 2 wait-state reads, the SEN signal must be qualified with  $\overline{CS}$  so that SEN does not extend into the cycle following the slave write. The most critical relationship to be satisfied in order for 2 wait-state writes is:

$$Tcac < Tc + Tch - 15 - 45$$

For a 10 MHz 82786 the DRAM/VRAM column access time must be:

$$Tcac < 50 + 25 - 45 = 30 \text{ ns}$$

Note that x 1 DRAMs have two transceiver delays.

The critical timing calculations for slave mode are calculated as follows. The actual numbers calculated are for an 80286/82786 system running at 10 MHz.

| chip-select-logic | = | path from 80286 ad      | ldress to | 82786 <del>CS</del> pin |   |            |

|-------------------|---|-------------------------|-----------|-------------------------|---|------------|

|                   | < | 2	imes clock period     |           | address valid           |   | setup      |

|                   | < | 2	imes 286.T1           |           | 286.T13                 | _ | 82786.Ts1  |

|                   | < | $2	imes 50~\mathrm{ns}$ |           | 60 ns                   | _ | 5 ns       |

|                   | < | 35 ns                   |           |                         |   |            |

| ready-logic       |   | path from 82786 SI      | EN to 82  | 284 SRDY pin            |   |            |

|                   | < | clock period            |           | SEN active              | _ | ARDY setup |

| (if ARDY is used  | < | 286.T1                  |           | 82786.S18               |   | 82284.T13  |

| as in Figure 19)  | < | 50 ns                   |           | 25 ns                   |   | 0 ns       |

|                   | < | 25 ns                   |           |                         |   |            |

| ready-logic       | = | path from 82786 SI      | EN to 82  | 284 ARDY pin            |   |            |

|                   | < | clock period            |           | SEN active              |   | SRDY setup |

| (if SRDY is used  | < | 286.T1                  |           | 82786.S18               |   | 82284.T11  |

| as in Figure 20)  | < | 50 ns                   |           | 25 ns                   |   | 15 ns      |

|                   | < | 10 ns                   |           |                         |   |            |

read data valid  $\geq$  82786.Ts22 + transceiver delay

from SEN active to write data valid

from SEN active to read data valid

write data valid  $\geq 82786.Ts20$

The master mode signals generated by the 82786 are all within the specification range guaranteed by the 80286. In other words, if the system memory is designed to function with the 80286, it will also be able to function with the 82786. The only signals that may not be within the range of the 80286 specifications are the data bus signals due to the transceiver delays. Care must be taken to ensure that the memory subsystems that the 82786 is to be able to access in master mode can meet these more stringent requirements:

|                  |   | data valid to falling clock a | fter Tc pha  | ise 2               |

|------------------|---|-------------------------------|--------------|---------------------|

| read data setup  | > | 82786 read data setup         | +            | transceiver-delay   |

|                  | > | 82786.T8                      | +            | data in to data out |

|                  | > | 5 ns                          | +            | Tprop               |

|                  |   | data valid delay from fallin  | ng clock aft | er Ts phase 1       |

| write data valid | < | 82786 write data valid        |              | transceiver delay   |

|                  | < | 82786.T14                     |              | data in to data out |

|                  | < | 40 ns                         |              | Tprop               |

The clock skew between the 80286 and the 82786 must be considered in all these calculations.

Figure 19. 286/82786 Synchronous Master/Slave Interface Permits Minimum of 2 Wait-State Write, 3 Wait-State Read

З

nt of

**AP-270**

292007-21

Figure 20. 286/82786 Synchronous Master/Slave Interface Fast DRAMs Permit Minimum of 2 Wait-State Read/Write

26

AP-270

nt d

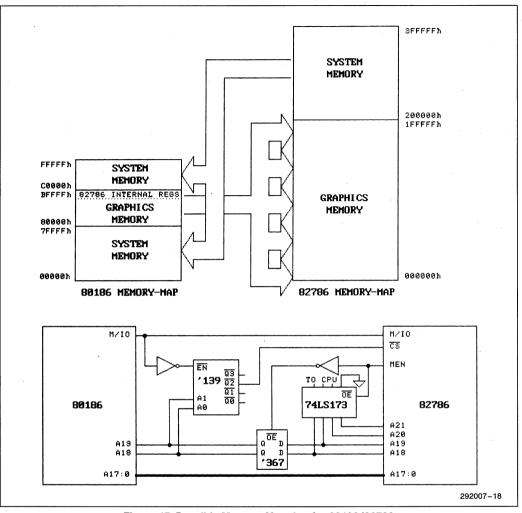

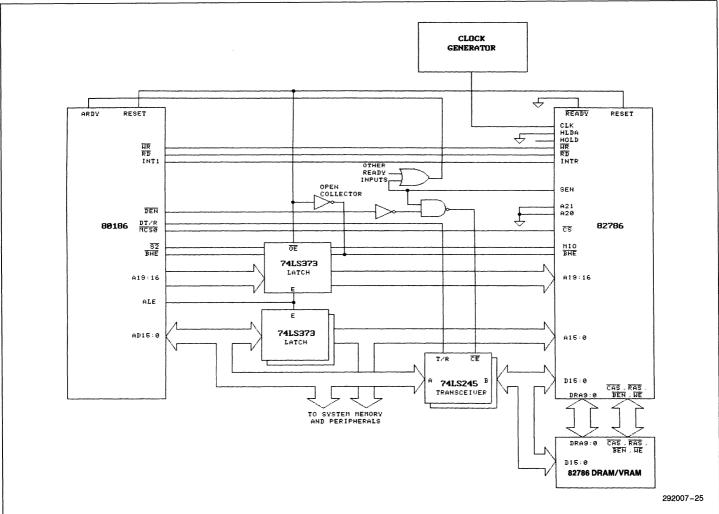

#### 4.4 80186 Synchronous Interface

The 82786 supports a synchronous status interface to the 80186. The 82786 and the 80186 must be driven with the same external clock (EFI). The Reset inputs to the 82786 must be generated from the RES for the 80186 by delaying it by one clock (input). This guarantees that the 82786 Clock phase 1 is coincident with 80186 CLKOUT low. A synchronous 80186 interface is selected if BHE is high and MIO is high prior to falling 82786 RESET.

Generally this configuration will be used with a minimum of 3 wait states for the 82786 slave read and write accesses. Therefore the WT bit in the 82786 BIU Control Register should be set. The 82786 slave accesses will then only be initiated when the 82786  $\overline{CS}$  is actually activated.

There is, however, a way to allow this interface to use a minimum of 2 wait states. (Set WT=0) Rather than wait for  $\overline{CS}$  to go active the 82786 can be allowed to request a slave access as soon as the 80186 status lines go active. If the 82786 is not in the midst of another bus cycle and the CPU request is the highest priority, the bus will immediately be granted to the CPU and a bus cycle started. If the  $\overline{CS}$  then goes active the 82786 can complete the access within 2 wait-states. If  $\overline{CS}$  does not go active (because the 80186 is not accessing the 82786 but rather its own memory or I/O) then the 82786 bus cycle.

If there is other RAM or ROM in the system besides the 82786 Graphics DRAM/VRAM that the 80186 often accesses, then this 2 wait-state will probably hinder rather than help performance. Every time the 80186 fetches from its own system memory (such as an opcode fetch or operand access), and the 82786 bus is idle, the 82786 will waste time running a dummy cycle. Fortunately, the busier the 82786 bus is, the less likely it will be free when the 80186 initiates a bus cycle, and therefore the less likely the 82786 will waste time running a dummy cycle.

#### 4.5 Asynchronous Interface

An asynchronous interface can be used to interface the 82786 with nearly any CPU. The CPU clock and the 82786 clock are independent and may run at different speeds. If the 80286 is connected asynchronously with the 82786 and both processors are run at approximately the same clock frequency, then the minimum possible wait-states is one more than for the corresponding synchronous mode.

Figure 21 shows a slave-only 10 MHz 82786 interface to an 8 MHz 80186. At 10 MHz, the 82786 requires that the address becomes valid S17 = 80 ns after  $\overline{RD}$  or  $\overline{WR}$  falls and remains valid for S16 = 130 ns. Because the 80186 address disappears the same cycle  $\overline{RD}$  and  $\overline{WR}$  fall, the address must be latched. This latched address can be shared by the other components on the 80186 bus.

Due to the indeterminate phase relationship between the CPU and 82786 clocks, care must be taken to ensure the read/write data timings have enough slack. When the read data is sampled, and when the write data is removed is determined by the CPU's ARDY input. The 82786 SEN signal is used to generate the ready signal which is responsible to ensure that the data is indeed available. D-flip-flops can be used to delay the SEN signal to delay the CPU ready signal. For a 10 MHz 82786:

| read data valid $\geq$  | from SEN active to read data valid<br>82786.Ts22 + Tprop |

|-------------------------|----------------------------------------------------------|

| write data valid $\geq$ | from SEN active to write data valid 82786.Ts20           |

To initially place the 82786 into the asynchronous interface mode, the 82786 BHE pin must be low during the falling edge of RESET. To ensure this, the 74LS373 latch for BHE is tristated and an open-collector inverter pulls down BHE during RESET.

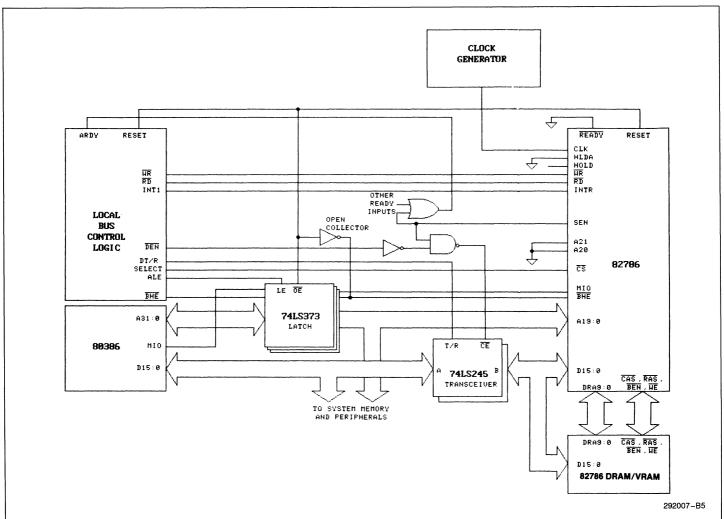

The 80386 processor can be interfaced to the 82786 either synchronously or asynchronously. For a synchronous interface, standard logic can be used around the 80386 to emulate a 80286 style bus for use with the interface described in Section 4.3. In this configuration the 82786 bus would run at half the clock rate of the 80386 (a 16 MHz 80386 would run with an 8 MHz 82786 bus). For an asynchronous interface, the standard local bus controller logic used by the 80386 to interface most peripherals can be used (Figure 22).

Although the actual bus transfers of a synchronous bus are faster than for an asynchronous bus, there are cases where an asynchronous interface provides the highest performance. For example, for a given display resolution, the Display Processor overhead of a 10 MHz 82786 is a lower percentage of the total bus throughput than for an 8 MHz 82786. If the 82786 is used with a 16 MHz 80386, then an asynchronous 10 MHz 82786 would have more bandwidth for the CPU and Graphics Processor than a synchronous 8 MHz 82786 and therefore CPU accesses, generally, will be completed faster with the asynchronous interface.

AP-270

Intel

Figure 21. 80186/82786 Asynchronous Slave-Only Interface 28

Figure 22. 80386/82786 Asynchronous Slave-Only Interface

29

AP-270

#### 4.6 Multiple 82786 Interface

For higher performance, it is possible to use several 82786 chips in the same system. Any of the above CPU/82786 interfaces can be used to attach multiple 82786s to one CPU in the system. Each 82786 will require its own separate DRAM/VRAM array.

The driving software for these multiple CPUs would most likely be sending nearly the same commands to all of the 82786s. Rather than forcing the software to write commands to each 82786 individually, it is possible to allow write commands to go to several or all the 82786s. One method of determining which 82786s should receive the write command would be to first write to an I/O port in which each bit corresponded to a different 82786. In Figure 23, the port bits set to 0 enable the corresponding 82786 for CPU writes. When a write to 82786 address-space occurs, all of the selected 82786s are chip-selected. The CPU will then wait for READY from all the selected 82786s before completing the bus cycle. In this manner, one, all, or any combination of 82786s can be written into at once.

Because it is impossible to read from several 82786s at once, a priority scheme is used on the I/O port to allow a read from only one of the selected 82786s. The circuit in Figure 23 only allows slave-accesses, the 82786s may not enter master-mode.

If master-mode operation of the multiple 82786s is desired, each 82786 must access the bus separately. A priority scheme is used to determine which 82786 is awarded the bus when the CPU issues HLDA. With only two possible 82786 masters, the random circuitry to hold one 82786 off the bus while the other is using it is straight-forward (Figure 24). With more 82786 masters, it is more feasible to use a state-machine (possibly implemented in PALs) to perform the arbiting.

#### 5.0 VIDEO INTERFACE

The video interface connects the 82786 to the video display. The 82786 is optimized to drive CRT monitors but may also be used to drive other types of displays. Because CRTs provide an inexpensive method of generating moderate and high resolution, monochrome and color displays, this application note will concentrate on CRT interfaces. Section 5.10 briefly describes other display interfaces.

The video interface for a CRT is very dependent on the CRT requirements and the resolution and depth (bits/ pixel) of the image desired. The 82786 can be programmed to directly generate all the CRT signals for up to 8 bits/pixel (256 color) displays at video rates up to 25 MHz. In addition, external hardware can be add-

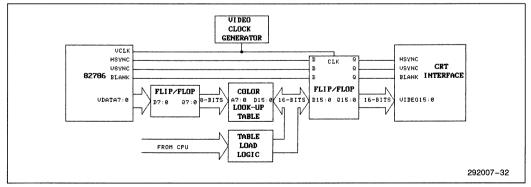

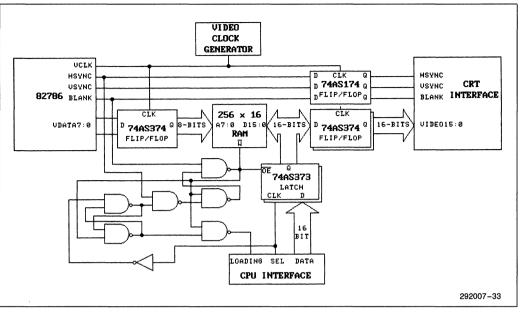

ed to allow a color look-up table or to trade-off the number of bits/pixel for higher display resolutions, or to use VRAMs.

Some of the possible display configurations are shown below. The calculations assume a 60 Hz refresh rate. High resolution CRTs are often run at a slower rate, which permits the 82786 to generate significantly higher resolutions than those in the following table. All cases assume a CRT horizontal retrace time of 7  $\mu$ s, except the 512  $\times$  512  $\times$  8 (10  $\mu$ s) and 640  $\times$  400  $\times$  8 (13  $\mu$ s) cases.

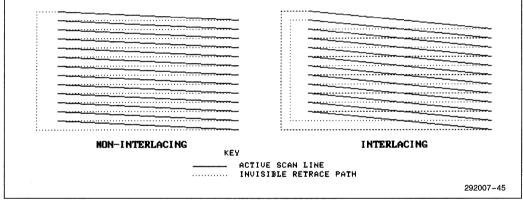

|                             | Non-<br>Interlaced                                 | Interlaced |  |  |  |

|-----------------------------|----------------------------------------------------|------------|--|--|--|

| 8 Bits/Pixel (256 colors)   | $512 \times 512$ $640 \times 400$ $640 \times 480$ | 900×675    |  |  |  |

| 4 Bits/Pixel (16 colors)    | 870×650                                            | 1290×968   |  |  |  |

| 2 Bits/Pixel (4 colors)     | 1144×860                                           | 1740×1302  |  |  |  |

| 1 Bit/Pixel<br>(monochrome) | 11472×1104                                         | 2288×1716  |  |  |  |

With Standard DRAMs

Multiple 82786s can be used together to generate even higher resolutions with more colors. For example, two 82786s allow a non-interlaced 1144  $\times$  860 sixteen color display.

With Video DRAMs\*

|                           | Non-Interlaced    |

|---------------------------|-------------------|

| 8 Bits/Pixel (256 colors) | 1024 $	imes$ 1024 |

| 4 Bits/Pixel (16 colors)  | 2048 $	imes$ 1024 |

| 2 Bits/Pixel (4 colors)   | 2048 $	imes$ 2048 |

| 1 Bit/Pixel (monochrome)  | 4096 $	imes$ 2048 |

\*For 64K by 4 - with 256K by 4 higher resolutions are supported

#### 5.1 Various CRT Interfaces

CRT monitors use a wide variety of interfaces. Some use TTL-levels on all inputs, others require analog inputs. Some use separate color inputs (red, green and blue) and separate horizontal and vertical sync while others require that some or all of these signals be combined into composite signals. This application note will concentrate on the generation of separate color and horizontal and vertical sync signals. Standard techniques can be used to convert these separate signals into composite signals to meet the requirements of other displays.

The video clock (VCLK) required by the 82786 may be generated by a simple oscillator with TTL-outputs. Alternatively, the VCLK can be tied to the bus clock (CLK) (or any other available clock) if they are to run at the same speed.

AP-270

Figure 23. This Configuration Allows Several 82786s to be Written by 80286 Simultaneously—Only Slave Accesses are Supported

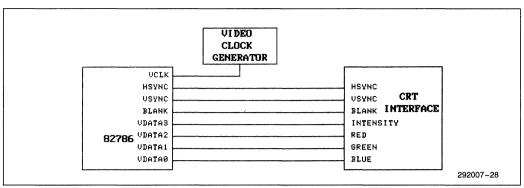

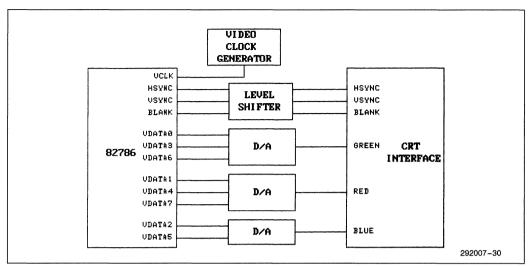

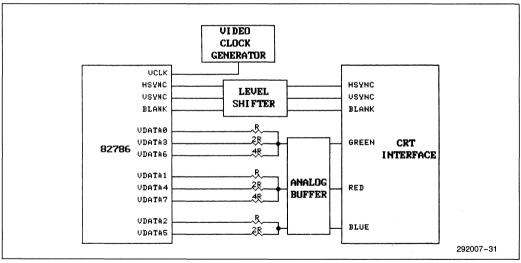

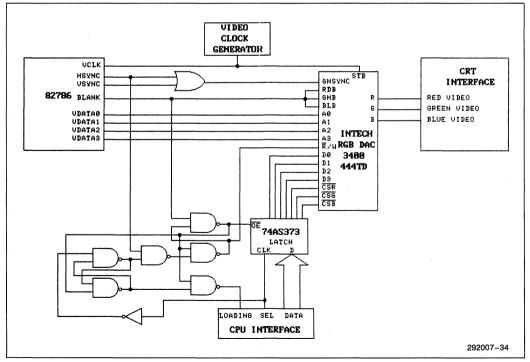

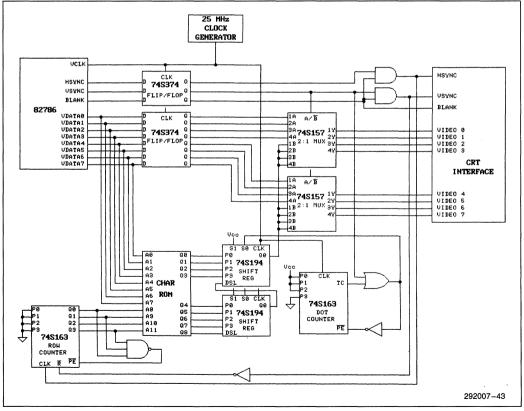

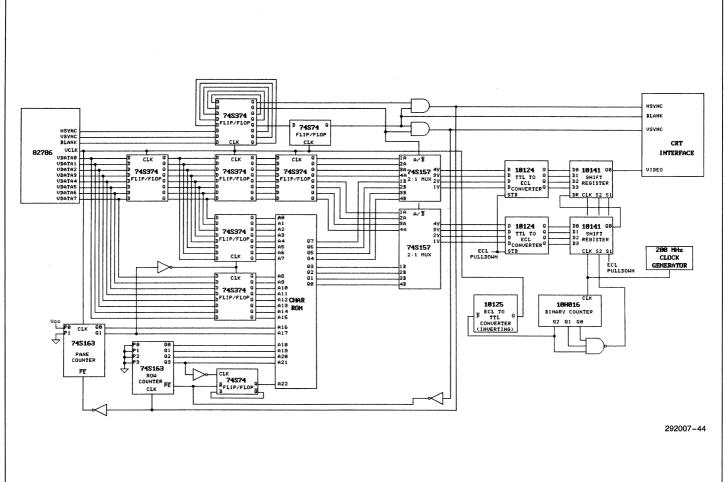

Figure 25. 82786 Can Directly Drive TTL-Input CRT Interface

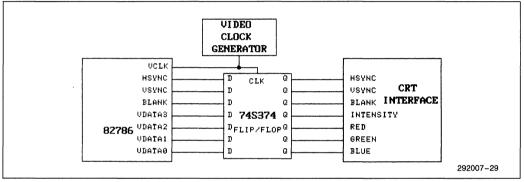

Figure 26. Buffer Used to Drive TTL-Input CRT Interface

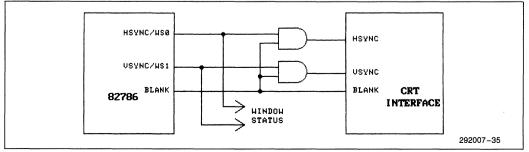

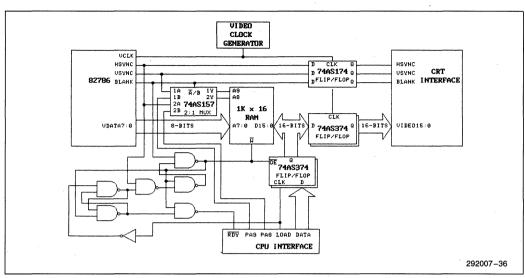

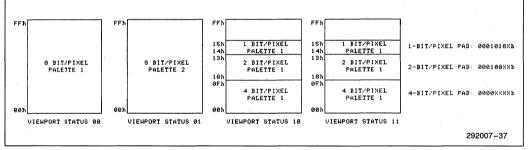

## 5.2 CRTs with TTL-level Inputs