# 82310/11 Micro Channel\* Compatible Peripheral Family

\*Micro Channel, PS/2, AT are trademarks of IBM.

# Micro Channel COMPATIBLE PERIPHERALS FAMILY

High Performance/High Integration/100% Compatibility

- Total Solution ... High Integration VLSI Components Implement Complete Micro Channel Compatible Motherboards

- Single Architectural Solution for 80386 and 80386SX Systems

- **■** High Performance

- 80386 Systems to 25 MHz

- Up to 16 MB of Zero Wait State Page-Interleaved DRAM

- Interface to Industry Standard 82385

Cache Controller for Maximum

Performance Memory Design

- 100% Compatible at All Levels

- Architecture Compatible

- Register Level Compatible

- Compatible with All Micro Channel Bus Timing and Drive Characteristics

- High Integration ... Two Chip Sets to Choose from, 82310 and More Highly Integrated 82311

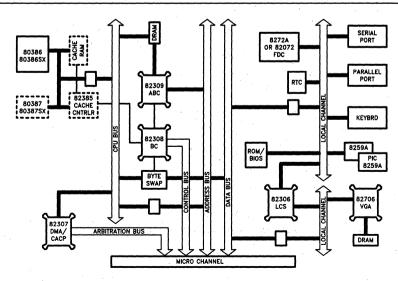

- 82310 Chip Set Includes:

- 82306 Local Channel Support Chip

- 82307 DMA Controller/Central Arbiter

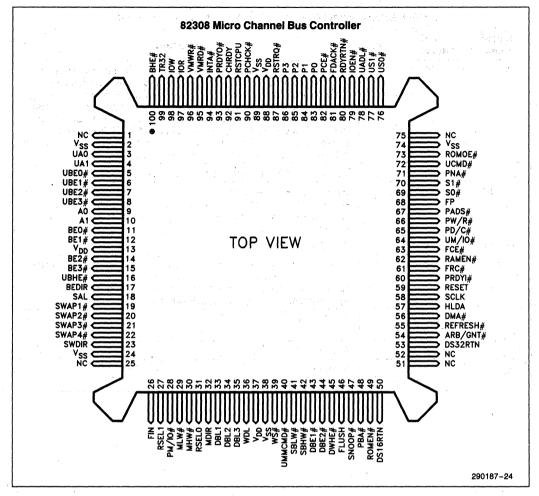

- 82308 Micro Channel Bus Controller

- 82309 Address Bus Controller

- 82706 VGA Graphics Controller

- 82311 Chip Set Includes:

- 82303 and 82304 Local I/O Channel Support Chips

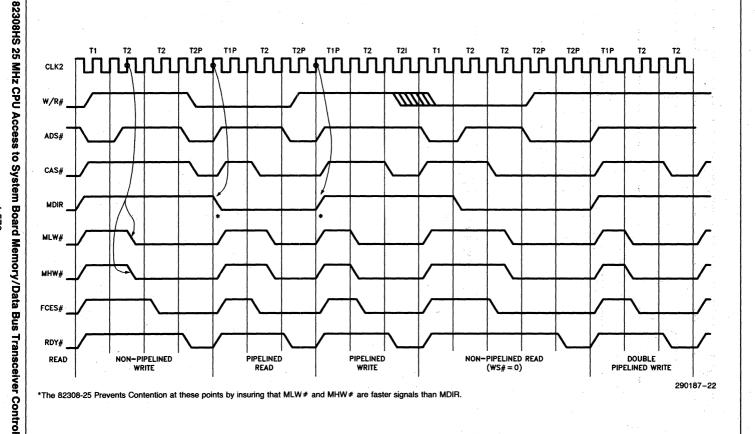

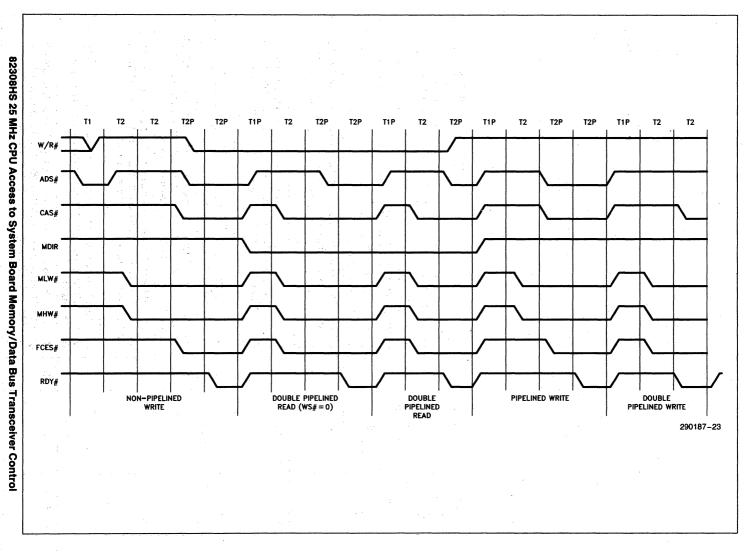

- 82307 DMA Controller/Central Arbiter

- 82308 Micro Channel Bus Controller

- 82309 Address Bus Controller

- 82706 VGA Graphics Controller

- 82077 Floppy Disk Controller

Intel's Micro Channel Peripheral Family consists of two chip sets, either of which can be used to build a high performance, 100% Micro Channel compatible motherboard. The two chip sets differ primarily in their implementation of the motherboard peripheral bus. The 82310 Chip Set supports either the 8272A or 82072 Floppy Disk Controller. The 82311 Chip Set features a more highly integrated peripheral bus, and includes the 82077 Single Chip Floppy Disk Controller. (The 82311 chip set does not support the 8272A or 82072.) Both chip sets support 80386 systems up to 25 MHz and 80386SX 16 MHz systems.

The following pages describe Intel's Micro Channel Peripheral Family. The first section presents an overview of the 82310 and 82311 chip sets, and discusses system issues such as clock requirements and Micro Channel interface logic. Following this are the individual component descriptions and specifications.

|       |                                             | 82310<br>Chip Set | 82311<br>Chip Set |

|-------|---------------------------------------------|-------------------|-------------------|

| 82303 | Local I/O Support Chip                      |                   | <b>/</b>          |

| 82304 | Local I/O Support Chip                      |                   | <b>~</b>          |

| 82306 | Local Channel Support<br>Chip               | . "               |                   |

| 82307 | DMA/Micro Channel<br>Arbitration Controller | ~                 | <b>∠</b> .".      |

| 82308 | Micro Channel Bus<br>Controller             | <b>–</b>          | ~                 |

| 82309 | Address Bus Controller                      | ~                 | ~                 |

| 82706 | VGA Graphics<br>Controller                  | -                 | <b>/</b> ,,,      |

| 82077 | Floppy Disk Controller                      |                   | · /               |

| Fic   | ure 1 Micro Channel Pe                      | arinheral E       | amily             |

Figure 1. Micro Channel Peripheral Family

# 82310 Micro Channel COMPATIBLE PERIPHERAL CHIP SET

- Highly Integrated VLSI Components to Implement Micro Channel™ Compatible Motherboard

- Single Architectural Solution for 80386 16 MHz, 20 MHz and 25 MHz systems, and 80386SX 16 MHz Systems

- Full Compatibility with IBM Micro Channel Architecture

- Zero-Wait State Performance

- Cache Interface (82385) for Highest Performance Compatible System Implementation with 80386

- Supports up to 16 MB of Memory on Motherboard

- Extended Memory for OS/2 Support

- 100% IBM Compatible VGA Graphics

- Flexible Memory Architecture Support

Up to 4 Banks of Interleaved Page Memory

- 256K, 1M, 4M DRAM Support

- Multiple Floppy Disk Controller Interface to Support 31/2" and 51/4" Disk Drives

- Keyboard and BIOS Support from 3rd Party

- Numeric Coprocessor(s) Interface (80387, 80387SX)

- Surface Mount Packaging for Small Footprint Design (0.025" Pitch)

- **Low Power CHMOS Technology**

- Available in 100 & 132-Pin Plastic Quad Flat Pack Packages.

(See Packaging Spec. # 231369)

Intel's peripheral chip family is designed to support the new generation of Micro Channel compatible systems. Intel's Micro Channel compatible peripheral solution consists of highly integrated VLSI components designed to support 80386 systems up to 25 MHz, as well as 16 MHz 80386SX systems.

The Intel solution is based on the high performance IBM Model 80 register model but it is highly integrated to provide full compatibility across all models. The specifications for 82310 VLSI components conform to architectural specifications defined for the Micro Channel Bus Architecture. The VLSI components are implemented in 1.5 micron CHMOS technology and packaged in space saving surface mount JEDEC flat pack packages.

290167-1

#### INTRODUCTION

The new generation of Personal Computer systems from IBM offers significant technological advantages over the PC/AT and XT systems. The most significant advancement is in the Architectural definition of the bus-Micro Channel Bus. Unlike the AT bus, the Micro Channel is well defined in terms of bus protocol timings. To create a compatible Micro Channel system requires adherence to the Micro Channel timings and electrical drive characteristics.

All IBM Micro Channel models have increased system functionality included on the motherboard. In the older PC/AT architecture, such functionality reguired the addition of peripheral cards. Specific features added to the motherboard include the Serial Port, Bi-directional Parallel Port and Video Graphics Control.

#### Micro Channel ARCHITECTURE

The Micro Channel Bus is defined to support an open architecture providing Multi-Master capability. Multi-Device arbitration with fairness, arbitration capability and easy configurability of the total system (Programmable Option Select-POS). Providing full details about the Micro Channel Bus Architecture is beyond the scope of this document. Please refer to IBM Technical Reference Manuals on Micro Channel systems.

To provide Multi-Master capability as defined in the Micro Channel Architecture, each Master device is responsible for driving the Address, Data, arbitration and control signals. For operation reliability and compatibility there are significant constraints in terms of timing and drive levels. These constraints are well documented in IBM's Technical Reference Manual for Micro Channel systems. Intel's chip set is designed to meet the Micro Channel timings.

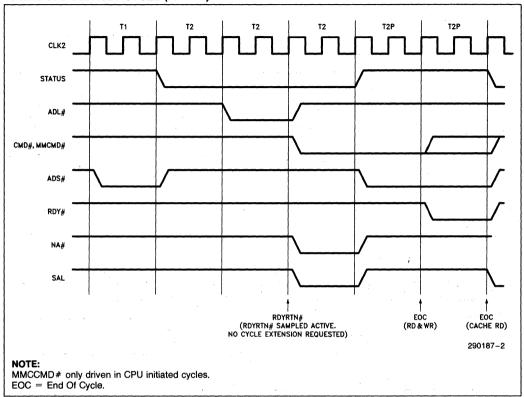

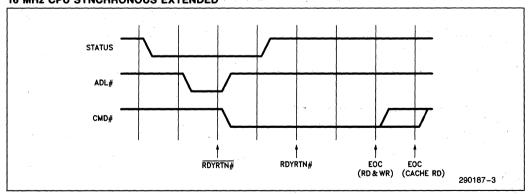

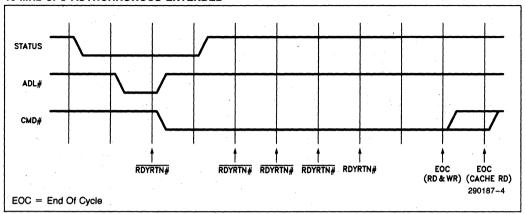

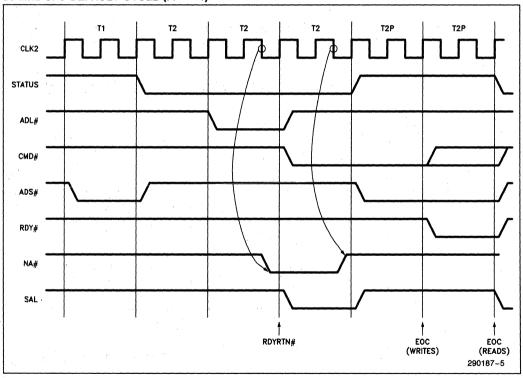

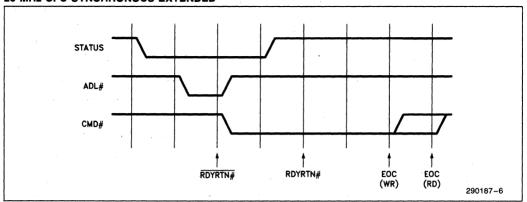

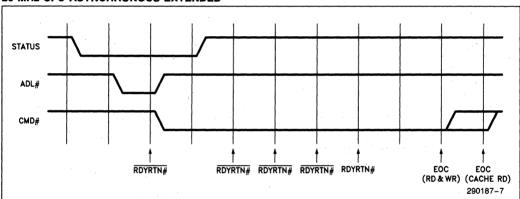

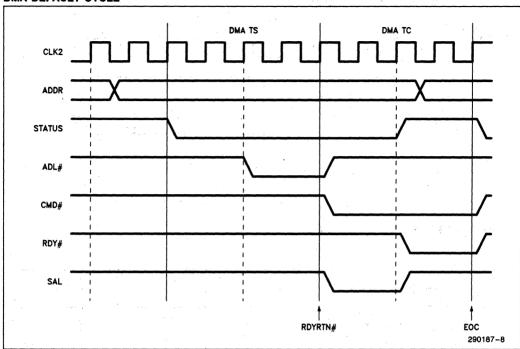

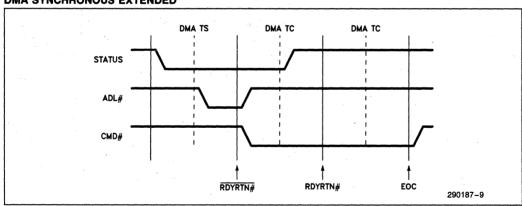

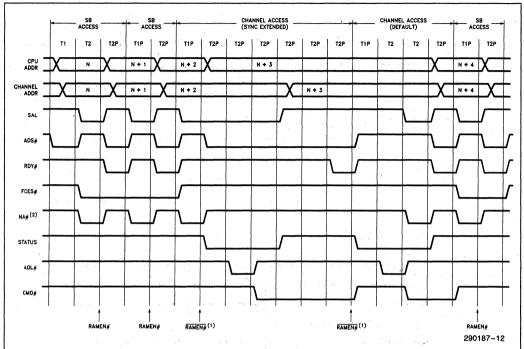

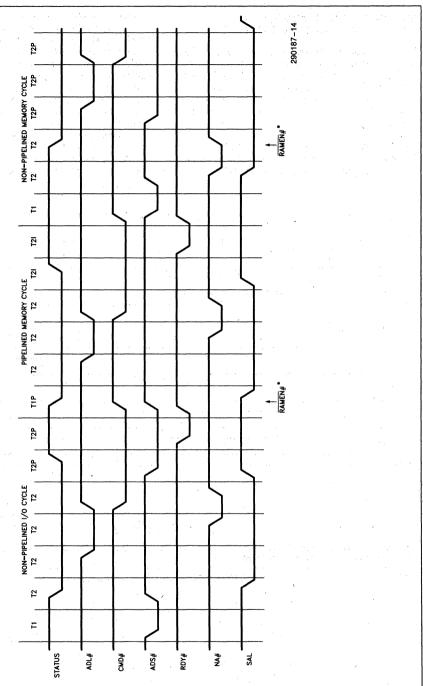

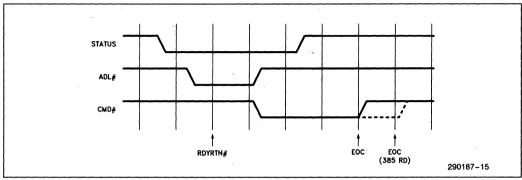

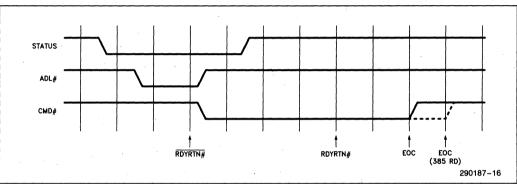

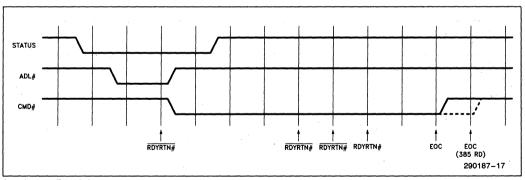

The Micro Channel has four modes of Memory and I/O Bus cycles. These are Default cycle, Synchronous Extended cycle, Asynchronous Extended cycle and Matched Memory cycle. Each of these bus cycles is supported by the Intel Peripheral chip set.

#### COMPATIBILITY METRICS

The Intel chip set provides full compatibility with the IBM Micro Channel solution. All Bus cycles comply with the Micro Channel timings. Selection of buffers for drive level with minimum delays to meet Micro Channel timings are specified in the Intel Designers Guide for Micro Channel Compatible Implementation.

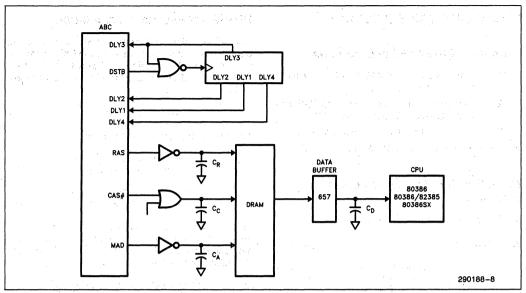

#### **MEMORY PERFORMANCE**

With the Intel chip set, Micro Channel compatible motherboards can be designed to provide zero-wait performance. Performance is predicated on memory design and DRAM speed selection. The Intel chip set offers flexible memory design support to meet various cost/performance goals.

#### SYSTEM CONSIDERATIONS

#### **System Components**

| 82306 | Local Channel Support Chip   |

|-------|------------------------------|

| 82307 | DMA/CACP Controller          |

| 82308 | Micro Channel Bus Controller |

| 82309 | Address Bus Controller       |

| 82706 | VGA Graphics Controller      |

Note that the above part names/numbers are frequency independent; i.e., they refer to a generic functional VLSI device. To actually implement for example, a 20 MHz system, however requires an 82310-20 Chip Set as opposed to an 82310-16 Chip Set. The 25 MHz version of the 82308 (dubbed the 82308HS-25) cannot be used at 16 MHz or 20 MHz.

To implement a minimum configuration Micro Channel compatible motherboard, each of the five system components listed above are required in addition to the following components:

- 80386 or 80386SX Microprocessor

- TTL/CMOS Buffers for Various Buses in the System

- 8742 Keyboard Controller with Firmware for 101 and 102 Keyboard Interface

- 8272A or 82072 for Floppy Disk Controller

- 8272A Required to Maintain IBM Look-Alike Motherboard with 31/2" Drive Support

- 82072 for PS/2 Compatible 31/2" and AT Compatible 51/4" Disk Drive Interface

- Battery-Backed Real Time Clock with CMOS RAM

- Serial Port

- Parallel Port

- Programmable Interrupt Controllers (Two 8259s)

- Memory

- ROM BIOS

- DRAMs for Main Memory

- DRAMs for VGA

- System Clock Sources

- Mechanical Connectors/Components

The Intel solution is supported by a fully compatible BIOS firmware from a third-party vendor.

# 82310 CHIP SET SYSTEM CLOCK REQUIREMENTS

- Introduction

- Clock Definitions

- Clock Requirements

#### INTRODUCTION

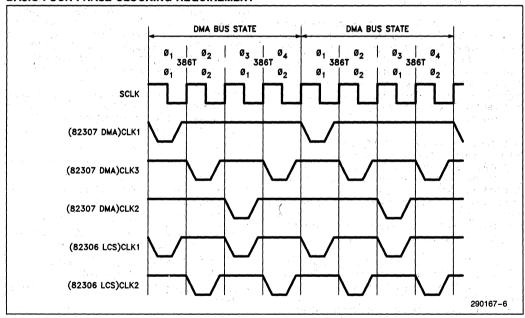

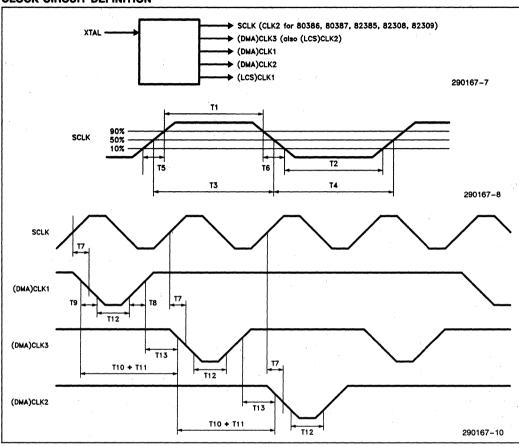

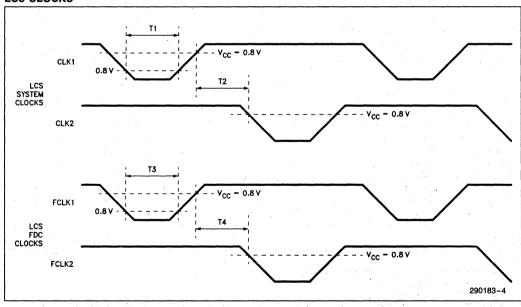

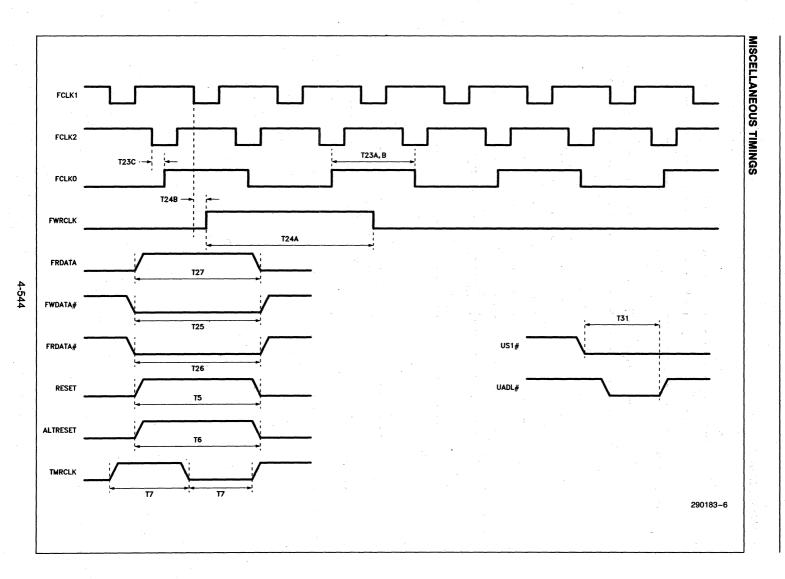

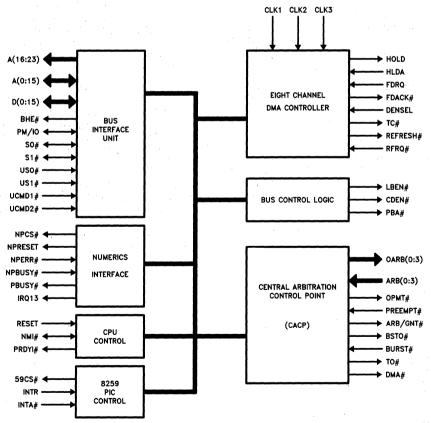

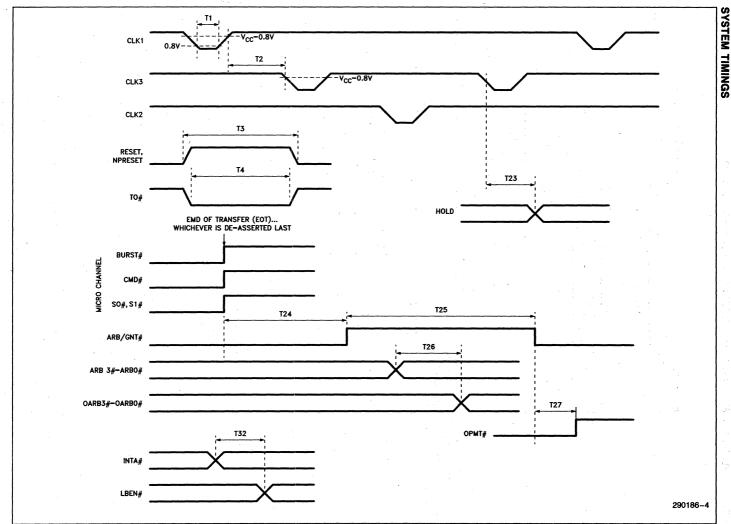

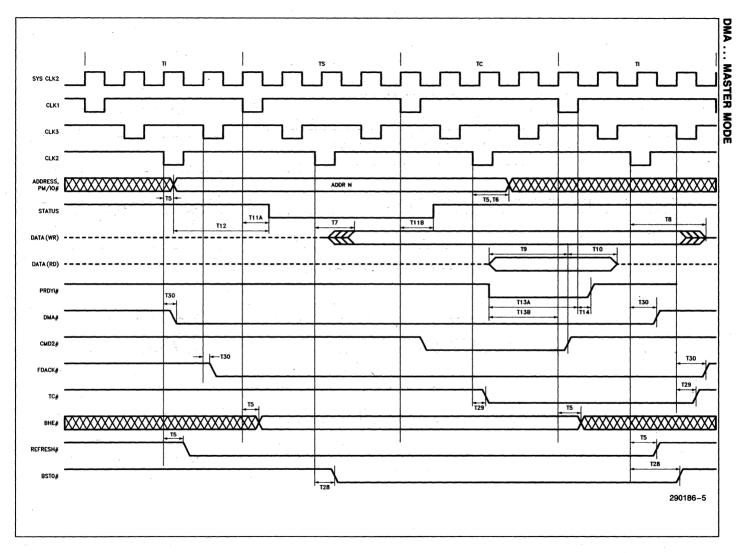

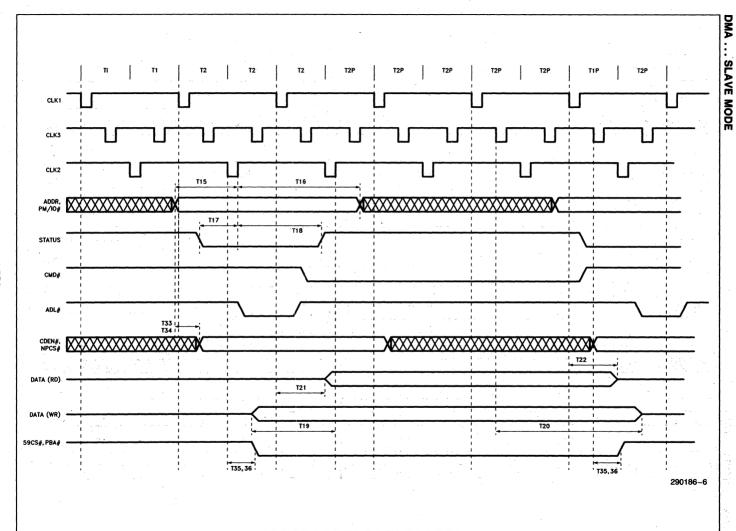

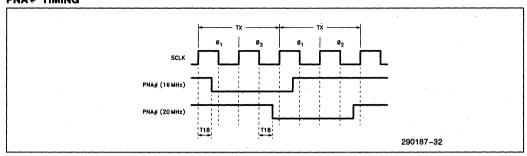

This section describes the basic clocking scheme of the host CPU (80386 or 80386SX), LCS (82306), DMA (82307), BC (82308) and ABC (82309). Although each component spec individually describes its own clock requirements, this section describes the synchronous relationship that exists between them. (Note that several other clocks exist in a Micro Channel system. However, this section describes only those clocks that are synchronously related to the CPU clock.)

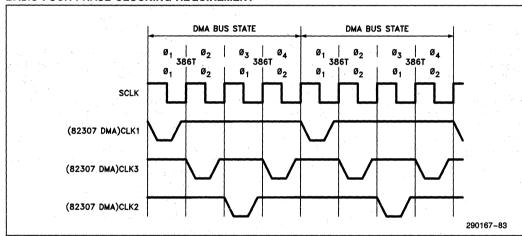

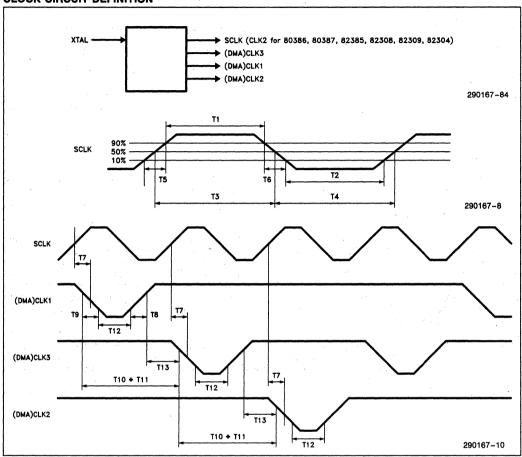

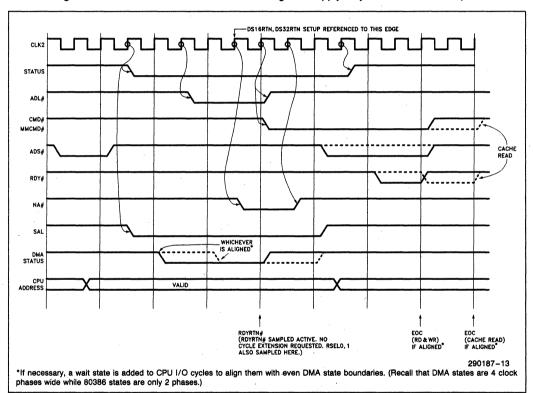

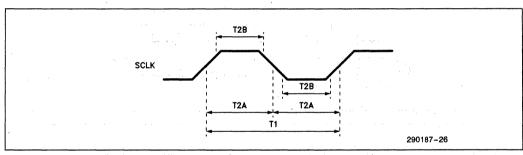

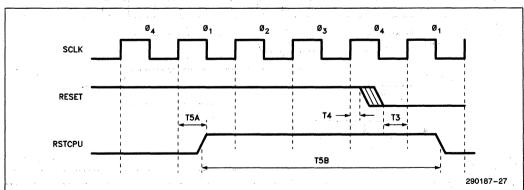

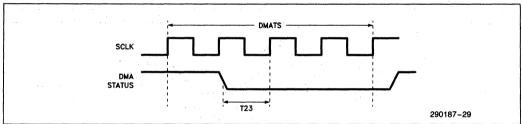

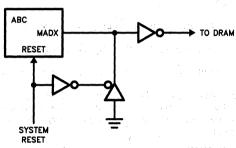

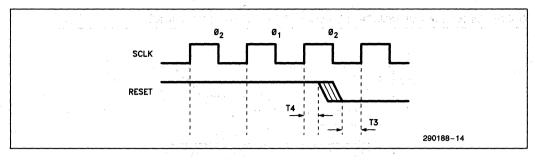

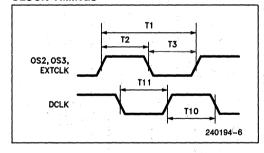

The clocking scheme essentially divides the DMA bus state into four phases as depicted in the figure. Note that there is a direct 2-to-1 mapping of 80386 state to DMA state. The DMA (82307) and LCS (82306) comprehend phases by inputting distinct, active low, non-overlapping clock phases. The Address Bus Controller and Bus Controller learn the system phase by synchronously sampling the falling edge of RESET, as described in the component specifications.

#### BASIC FOUR-PHASE CLOCKING REQUIREMENT

#### **CLOCK CIRCUIT DEFINITION**

#### SYSTEM CLOCK REQUIREMENTS

| Symbol | Parameter               | Kit 16 MHz |     | Kit 20 MHz |     | Kit 25 MHz |     | Notes  |

|--------|-------------------------|------------|-----|------------|-----|------------|-----|--------|

| Cymbol |                         | Min        | Max | Min        | Max | Min        | Max | 110100 |

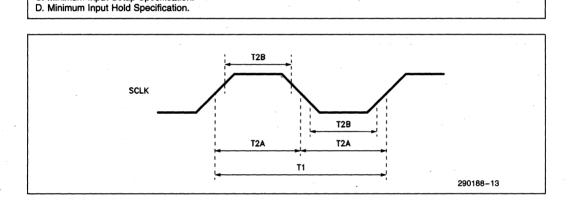

| T1     | SCLK High Time (90%)    | 8          |     | 6.5        |     | 5.5        |     |        |

| T2     | SCLK Low Time (10%)     | 8          | 1 1 | 6.5        |     | 5.5        |     |        |

| T3     | SCLK High Time (50%)    | 12         |     | 10         |     | 9.         |     | 1      |

| T4     | SCLK Low Time (50%)     | 12         |     | 10         |     | 9          |     | 1      |

| T5     | SCLK Rise Time          | ł          | 3.5 | 1          | 3.5 |            | 3.5 |        |

| T6     | SCLK Fall Time          | İ          | 3.5 |            | 3.5 |            | 3.5 |        |

| T7     | SCLK-To-DMACLK(N) Skew  | -2         | 3   | -2         | 3   | -2         | 3   | 2      |

| T8     | DMACLK(N) Rise Time     | }          | 2   | 1          | 2   |            | 2   |        |

| T9     | DMACLK(N) Fall Time     | ł          | - 2 |            | 2   |            | 2   |        |

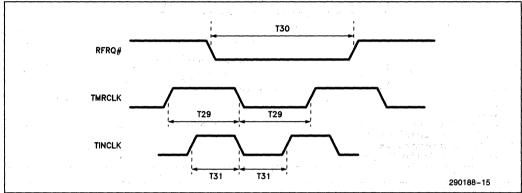

| T10    | SCLK Period             | ļ          |     | 1          |     |            |     |        |

| T11    | DMACLK-To-DMACLK Skew   | -2         | 2   | -2         | 2   | -2         | 2   | 2      |

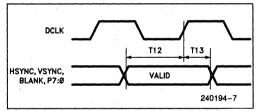

| T12    | DMACLK Low Time         | 15         |     | 15         | 1   | 12         |     |        |

| T13    | DMACLK Non-Overlap Time | 4          |     | 4          |     | 2          |     |        |

#### NOTES:

- 1. Needed to enforce a duty cycle between 40% and 60%. (45% and 55% at 25 MHz.)

- 2. Limiting skew to this level is recommended.

# 82311 HIGH INTEGRATION Micro Channel COMPATIBLE PERIPHERAL CHIP SET

- High Integration VLSI Components to Implement Micro Channel™ Compatible Motherboard

- Single Architectural Solution for 80386

16 MHz, 20 MHz and 25 MHz Systems

and 80386SX 16 MHz Systems

- Full Compatibility with IBM Micro Channel Architecture

- **■** Zero-Wait State Performance

- Cache Interface (82385) for Highest Performance Compatible System Implementation with 80386

- Supports up to 16 MB of Memory on Motherboard

- Extended Memory for OS/2 Support

- 100% IBM Compatible VGA Graphics

- Flexible Memory Architecture Support

Up to 4 Banks of Interleaved Page

Memory

- 256K, 1M, 4M DRAM Support

- Supports the 82077 Single Chip Floppy Disk Controller, Which Supports 3½" and 5½" Disk Drives

- Keyboard and BIOS Support from 3rd Party

- Numeric Coprocessor(s) Interface (80387, 80387SX)

- Surface Mount Packaging for Small Footprint Design (0.025" Pitch)

- Low Power CHMOS Technology

- Available in 100 & 132-Pin Plastic Quad Flat Pack Packages.

(See Packaging Spec. # 231369)

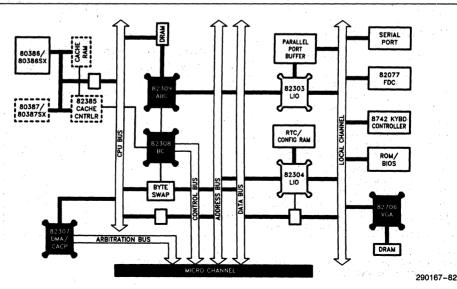

Intel's peripheral chip family is designed to support the new generation of Micro Channel compatible systems. Intel's Micro Channel compatible peripheral solution consists of highly integrated VLSI components designed to support 80386 systems up to 25 MHz, as well as 16 MHz 80386SX systems.

The Intel solution is based on the high performance IBM Model 80 register model but it is highly integrated to provide full compatibility across all models. The specifications for 82311 VLSI components conform to architectural specifications defined for the Micro Channel Bus Architecture. The VLSI components are implemented in 1.5 micron CHMOS technology and packaged in space saving surface mount JEDEC flat pack packages.

#### INTRODUCTION

The new generation of Personal Computer systems from IBM offers significant technological advantages over the PC/AT and XT systems. The most significant advancement is in the *Architectural* definition of the bus—Micro Channel Bus. Unlike the AT bus, the Micro Channel is well defined in terms of bus protocol timings. To create a compatible Micro Channel system requires adherence to the Micro Channel timings and electrical drive characteristics.

All IBM Micro Channel models have increased system functionality included on the motherboard. In the older PC/AT architecture, such functionality required the addition of peripheral cards. Specific features added to the motherboard include the Serial Port, Bi-directional Parallel Port and Video Graphics Control.

#### Micro Channel ARCHITECTURE

The Micro Channel Bus is defined to support an open architecture providing Multi-Master capability, Multi-Device arbitration with fairness, arbitration capability and easy configurability of the total system (Programmable Option Select-POS). Providing full details about the Micro Channel Bus Architecture is beyond the scope of this document. Please refer to IBM Technical Reference Manuals on Micro Channel systems.

To provide Multi-Master capability as defined in the Micro Channel Architecture, each Master device is responsible for driving the Address, Data, arbitration and control signals. For operation reliability and compatibility there are significant constraints in terms of timing and drive levels. These constraints are well documented in IBM's Technical Reference Manual for Micro Channel systems. Intel's chip set is designed to meet the Micro Channel timings.

The Micro Channel has four modes of Memory and I/O Bus cycles. These are Default cycle, Synchronous Extended cycle, Asynchronous Extended cycle and Matched Memory cycle. Each of these bus cycles is supported by the Intel Peripheral chip set.

#### **COMPATIBILITY METRICS**

The Intel chip set provides full compatibility with the IBM Micro Channel solution. All Bus cycles comply with the Micro Channel timings. Selection of buffers for drive level with minimum delays to meet Micro Channel timings are specified in the Intel Designers Guide for Micro Channel Compatible Implementation.

#### **MEMORY PERFORMANCE**

With the Intel chip set, Micro Channel compatible motherboards can be designed to provide zero-wait performance. Performance is predicated on memory design and DRAM speed selection. The Intel chip set offers flexible memory design support to meet various cost/performance goals.

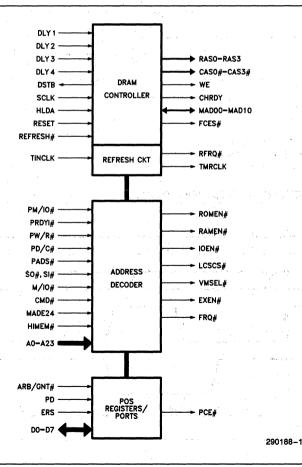

#### SYSTEM CONSIDERATIONS

#### **System Components**

82303 Local I/O Support Chip 82304 Local I/O Support Chip 82307 DMA/CACP Controller 82308 Micro Channel Bus Controller 82309 Address Bus Controller 82706 VGA Graphics Controller 82077 Floppy Disk Controller

Note that the above names/numbers are frequency independent; i.e., they refer to a generic functional VLSI device. To actually implement for example, a 20 MHz system, however, requires an 82311-20 Chip Set as opposed to an 82311-16 Chip Set. The 25 MHz version of the 82308 (dubbed the 82308HS-25) cannot be used at 16 MHz or 20 MHz.

To implement a minimum configuration Micro Channel compatible motherboard, each of the seven system components listed above are required in addition to the following components:

- 80386 or 80386SX Microprocessor

- TTL Buffers for Various Buses in the System

- 8742 Keyboard Controller with Firmware for 101 and 102 Keyboard Interface

- Battery-Backed Real Time Clock with CMOS RAM

- Serial Port

- Memory

- ROM BIOS

- DRAMs for Main Memory

- DRAMs for VGA

- System Clock Sources

- Mechanical Connectors/Components

The Intel solution is supported by a fully compatible BIOS firmware from a third-party vendor.

# 82311 CHIP SET SYSTEM CLOCK REQUIREMENTS

- Introduction

- Clock Definitions

- **■** Clock Requirements

#### INTRODUCTION

This section describes the basic clocking scheme of the host CPU (80386 or 80386SX), LIO (82304), DMA (82307), BC (82308) and ABC (82309). Although each component spec individually describes its own clock requirements, this section describes the synchronous relationship that exists between them. (Note that several other clocks exist in a Micro Channel system. However, this section describes only those clocks that are synchronously related to the CPU clock.)

The clocking scheme essentially divides the DMA bus state into four phases as depicted in the figure. Note that there is a direct 2-to-1 mapping of 80386 state to DMA state. The DMA (82307) comprehends phases by inputting distinct, active low, non-overlapping clock phases. The Address Bus Controller, Bus Controller and LIO device learn the system phase by synchronously sampling the falling edge of RESET, as described in the component specifications.

#### BASIC FOUR-PHASE CLOCKING REQUIREMENT

#### **CLOCK CIRCUIT DEFINITION**

#### SYSTEM CLOCK REQUIREMENTS

| Symbol | Parameter               | Kit 16 MHz |     | Kit 20 MHz |     | Kit 25 MHz |     | Notes  |

|--------|-------------------------|------------|-----|------------|-----|------------|-----|--------|

| Symbol | raramotor               | Min        | Max | Min        | Max | Min        | Max | .,0.00 |

| T1     | SCLK High Time (90%)    | 8          |     | 6.5        |     | 5.5        |     |        |

| T2     | SCLK Low Time (10%)     | 8          |     | 6.5        |     | 5.5        |     |        |

| T3     | SCLK High Time (50%)    | 12         |     | 10         |     | 9          |     | 1      |

| T4     | SCLK Low Time (50%)     | 12         |     | 10         |     | 9          |     | 1      |

| T5     | SCLK Rise Time          |            | 3.5 | l          | 3.5 |            | 3.5 |        |

| T6     | SCLK Fall Time          | 1          | 3.5 |            | 3.5 | 1          | 3.5 |        |

| T7     | SCLK-To-DMACLK(N) Skew  | -2         | 3   | -2         | 3   | -2         | 3   | 2      |

| T8     | DMACLK(N) Rise Time     |            | 2   |            | 2   |            | 2   |        |

| T9     | DMACLK(N) Fall Time     |            | 2   | 1          | - 2 |            | 2   |        |

| T10    | SCLK Period             |            |     | 1          |     |            |     |        |

| T11    | DMACLK-To-DMACLK Skew   | -2         | 2   | -2         | 2   | -2         | 2   | 2      |

| T12    | DMACLK Low Time         | 15         |     | 15         | -   | 12         |     |        |

| T13    | DMACLK Non-Overlap Time | 4          |     | 4          | ĺ   | 2          |     |        |

#### **NOTES:**

<sup>1.</sup> Needed to enforce a duty cycle between 40% and 60% (45% and 55% at 25 MHz).

<sup>2.</sup> Limiting skew to this level is recommended.

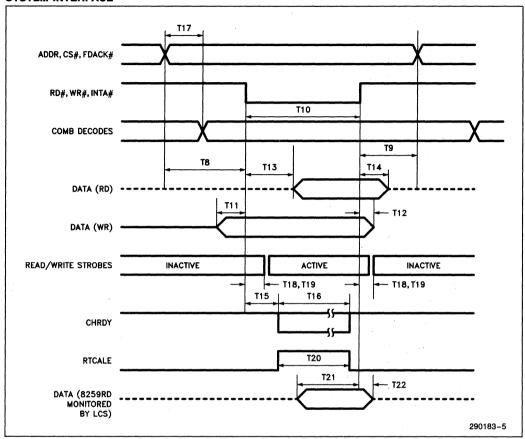

# Micro Channel INTERFACE AND SPECIFICATIONS

- Introduction

- Micro Channel Specifications

- Micro Channel Interface Logic Requirements

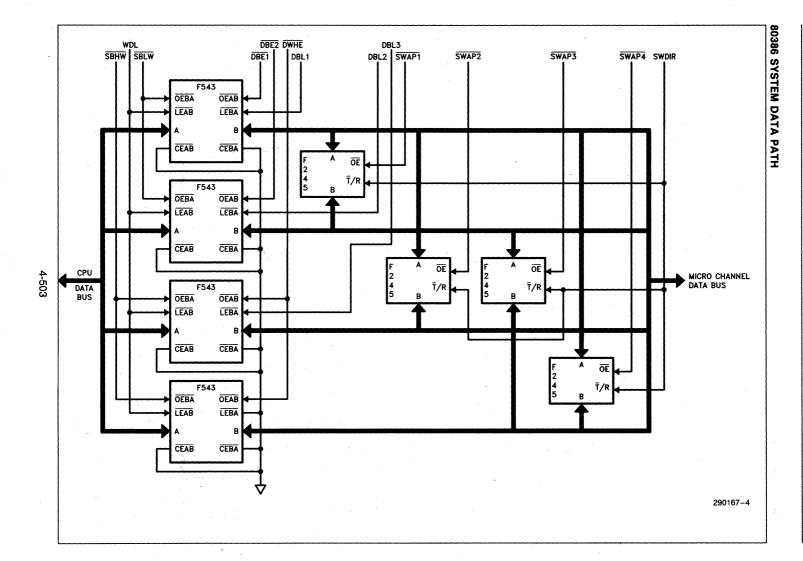

- 80386 System Data Path

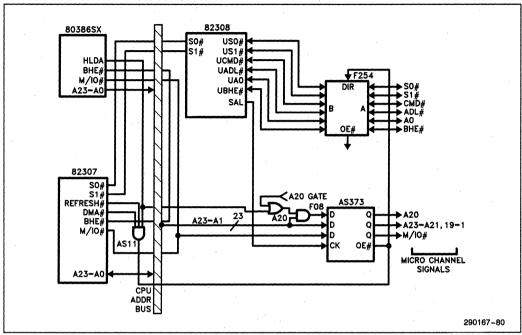

- 80386 System Address/Command Path

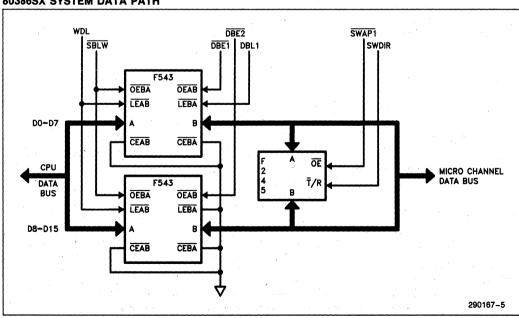

- 80386SX System Data Path

- 80386SX System Address Command Path

#### INTRODUCTION

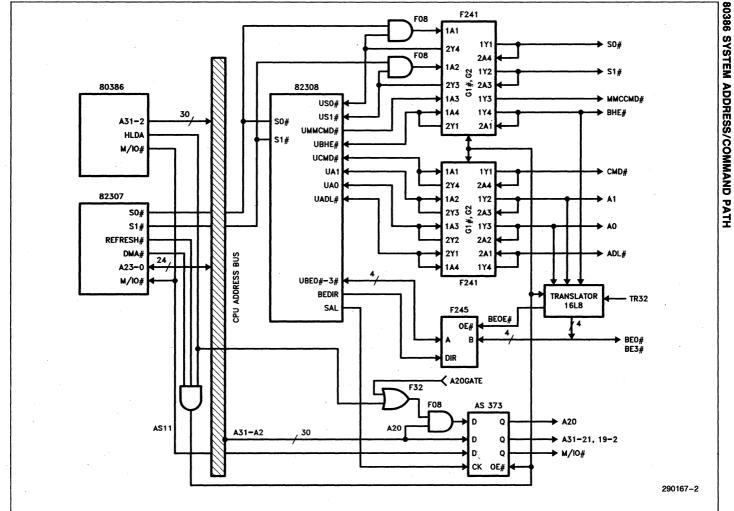

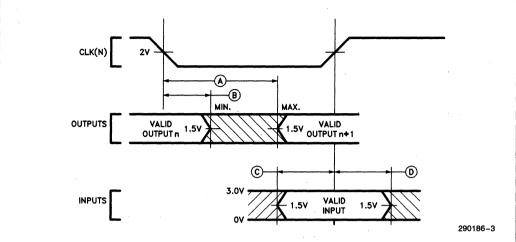

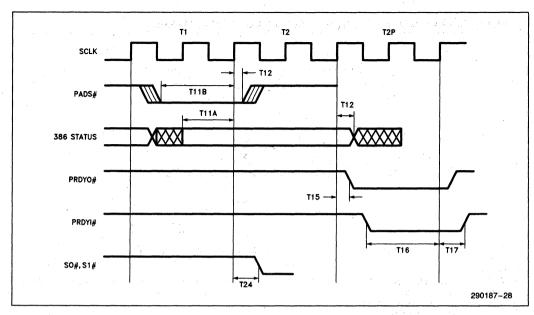

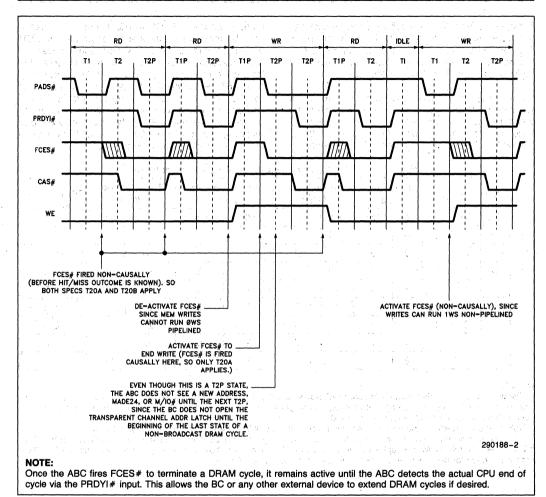

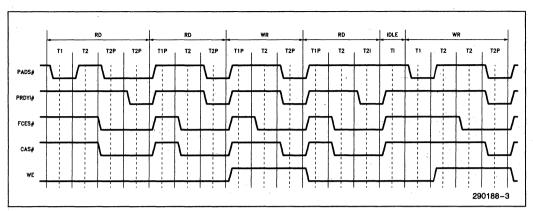

This section describes the interface between the host CPU (80386, 80386SX), DMA (82307), Bus Controller (82308) and Micro Channel Bus. This interface provides 100% compliance to published Micro Channel timings, driver type requirements, drive levels, and drive current capability. Timings meet the full capacitive load allowed on the Micro Channel.

The Micro Channel Specifications included in this section assume the specific TTL Data, Address, and Command Path interfaces depicted in the accompanying figures. Timing analysis was based on the Bus Controller AC specifications included in the 82308 Bus Controller section. Worst case TTL analysis was used, except when two related signals share a path through the same physical chip. (For example, since MMCCMD#, S0#, and S1# propagate through the same 74F241 package in an 80386 system, one signal will not experience a worst case delay while the other sees a best case. Rather, it is assumed that the signals will track within 2 ns of each other.) For this reason, it is important to follow the recommendations detailed at the end of this section in the Interface Logic Notes.

The F and AS TTL logic is typically specified into a 50 pF load, worst case delays were derated at 1 ns per 50 pF for loads greater than 50 pF. As an example, the 74F241 published maximum delay is specified as 7 ns. To meet Micro Channel bus loading of 250 pF, a 4 ns derating factor was added, resulting in an effective worst case delay of 11 ns.

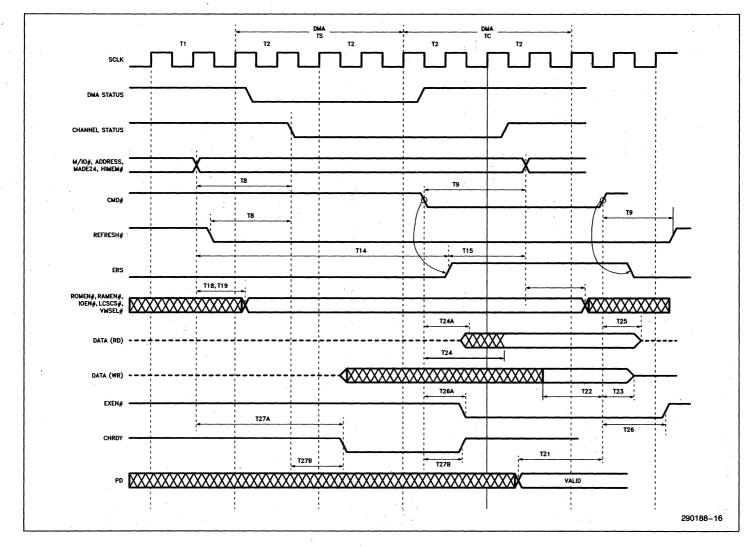

# **DEFAULT CYCLE SPECIFICATIONS**

# **ALL KITS**

| Symbol | Parameter                                        | Min | Max      |

|--------|--------------------------------------------------|-----|----------|

| T1     | Status active from ADDR,M/IO#,REFRESH#           | 10  |          |

| T2     | CMD# active from Status active                   | 55  | j        |

| T3     | ADL# active from ADDR,M/IO#,REFRESH#             | 45  | •        |

| T4     | ADL# active to CMD# active                       | 40  |          |

| T5     | ADL# active from Status active                   | 12  | ĺ        |

| T6     | ADL# pulse width                                 | 40  | <b>!</b> |

| T7     | Status hold from ADL# inactive                   | 25  |          |

| T8     | ADDR,M/IO#,REFRESH#,SBHE# hold frm ADL# INACTIVE | 25  |          |

| T9     | ADDR,M/IO#,REFRESH#,SBHE# hold frm CMD# ACTIVE   | 30  | 1        |

| T10    | Status hold from CMD# active                     | 30  |          |

| T11    | SBHE# setup to ADL# inactive                     | 40  | 1        |

| T12    | SBHE# setup to CMD# active                       | 40  |          |

| T13    | CDDS16/32 active from ADDR,M/IO#,REFRESH#        |     | 55       |

| T14    | CDSFDBK# active from ADDR,M/IO#,REFRESH#         |     | 60       |

| T15    | CMD# active from ADDRESS valid                   | 85  | i        |

| T16    | CMD# pulse width                                 | 90  |          |

| T17    | Write data setup to CMD# active                  | 0   |          |

| T18    | Write data hold from CMD# inactive               | 30  |          |

| T19    | Status to Read Data valid (Access Time)          |     | 125      |

| T20    | Read Data valid from CMD# active                 |     | 60       |

| T21    | Read Data hold from CMD# inactive                | 0   |          |

| T22    | Read Data bus tri-state from CMD# INACTIVE       |     | 40       |

| T23    | CMD# active to next CMD# active                  | 190 | }        |

| T23A   | CMD# inactive to next CMD# active                | 80  |          |

| T23B   | CMD# inactive to next ADL# active                | 40  |          |

| T24    | Next Status active from Status Inactive          | 30  |          |

| T25    | Next Status active to CMD# Inactive              |     | 20       |

| T26    | CHRDY INACTIVE FROM ADDR VALID                   |     | 60       |

| T27    | CHRDY INACTIVE FROM STATUS ACTIVE                |     | 30       |

| T28    | CHRDY RELEASE FROM CMD# ACTIVE                   |     | 30       |

| T28D   | READ DATA VALID FROM CMD# ACTIVE                 |     | 160      |

| T29S   | READ DATA VALID FROM CHRDY RELEASE               |     | 60       |

| T31    | BE#(0-3) from Addr valid (32-Bit Masters Only)   |     | 40       |

| T32    | BE#(0-3) active from SBHE#,A0,A1 active          |     | 30       |

| T33    | BE#(0-3) active to CMD# active                   | 10  |          |

# MATCHED MEMORY CYCLE SPECIFICATIONS

#### ALL KITS

| Symbol | Parameter                                     | Min            | Max |

|--------|-----------------------------------------------|----------------|-----|

| T1 .   | ADDR VALID TO STATUS ACTIVE                   | 10             |     |

| T2     | Status valid to MMCCMD# active                | 82             | 1   |

| T3     | ADDR hold from MMCCMD# active                 | 20             |     |

| T4 .   | Status hold from MMCCMD# active               | 25             | 1   |

| T5     | CDDS16/32 active from ADDR valid              |                | 55  |

| T6     | MMCR# active from ADDR valid                  | * *            | 55  |

| T7     | CDSFDBK# active from ADDR valid               | e para e       | 60  |

| T8     | ADDR valid to MMCCMD# active                  | 100            |     |

| T9     | MMCCMD# pulse width                           | 85             |     |

| T10    | Write Data valid to MMCCMD# active            | 0              | 1   |

| T11    | Write Data hold from MMCCMD# inactive         | 30             |     |

| T12A   | Read Data valid from Status active            |                | 145 |

| T12B   | for non-aligned xfers (16b $<$ = $=$ $>$ 32b) |                | 145 |

| T13A   | Read Data valid from MMCCMD# active           |                | 60  |

| T13B   | for non-aligned xfers (16b <= = > 32b)        | and the second | 60  |

| T14    | Read Data hold from MMCCMD# inactive          | 0              |     |

| T15    | Read Data off dly from MMCCMD# inactive       |                | 40  |

| T16    | MMCCMD# active to next MMCCMD# active         | 180            | 1   |

| _T17   | CDCHRDY valid from ADDR valid                 | 200            | 70  |

| T18    | CDCHRDY valid from Status active              | - 1            | 30  |

| T23    | Status inactive pulse width                   | 30             | • . |

| T24    | MMCCMD# inactive to Status active             | 5              | 1   |

| T25    | MMCCMD# inactive pulse width                  | 85             | ,   |

| T26    | MMCCMD# ACTIVE TO NEXT STATUS ACTIVE          | 90             |     |

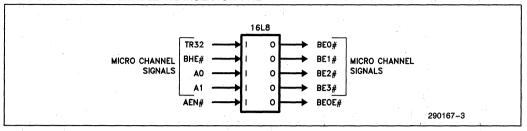

#### 80386 SYSTEM BYTE ENABLE TRANSLATOR PAL

| TR32 | AEN# | BHE# | A1 | A0 | BE3# | BE2#  | BE1# | BE0# | BEOE# |

|------|------|------|----|----|------|-------|------|------|-------|

| 1    | 1    | 0    | 0  | 0  | 1    | 1     | 0 -  | 0    | 1     |

| - 1  | 1    | 0    | 0  | 1  | 1    | 1 ;   | 0    | 1    | 1     |

| 1    | 1    | 0    | 1  | 0  | 0    | 0     | - 1  | 1    | 1     |

| . 1  | 1    | 0    | 1  | 1  | 0    | . 1   | . 1  | 1    | 1     |

| . 1  | 1    | 1    | 0  | 0  | 1    | 1     | 1    | 0    | 1     |

| 1    | 1    | 1    | 0  | .1 | 1    | 1     | 0    | 1    | 1     |

| 1    | 1    | 1    | 1  | 0  | 1    | 0     | 1    | 1 ;  | 1     |

| 1    | 1    | . 1  | 1  | 1  | 0    | : 1 - | 1    | 1    | 1     |

| , 0  | Х    | X /  | Х  | Х  | TS   | TS    | TS   | TS   | 0     |

| X.   | 0 -  | · X  | Х  | Х  | TS   | TS    | TS   | TS   | . 0   |

TS = TRISTATE

#### 80386SX SYSTEM ADDRESS/COMMAND PATH

#### 80386SX SYSTEM DATA PATH

#### **Micro Channel Interface Logic Notes**

#### 80386 SYSTEM

- The F08 gates in the S0#, S1# path are required at 20 MHz and at 25 MHz. They should not be used at 16 MHz.

- In an 82385 system, the A20 gate logic is on the 80386 local bus, and is thus not required on the 82385 local bus as shown in the diagram.

- The F08 gates in the S0#, S1# path and the F08 in the A20 path should all be from the same TTL package.

- 4. It is important that S0#, S1#, BHE#, and MMCCMD# go through the same F241 package, and that CMD#, ADL#, A0, and A1 go through the same package.

#### 80386SX SYSTEM

1. The F08 gates in the S0#, S1# path and in the A20 path should all be from the same package.

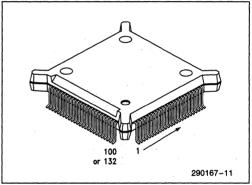

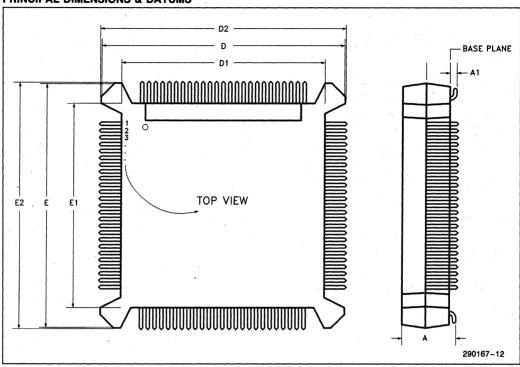

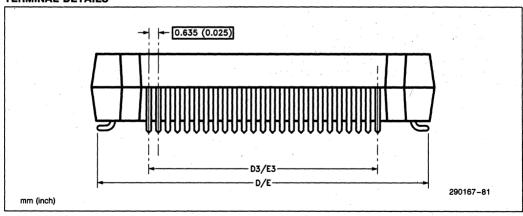

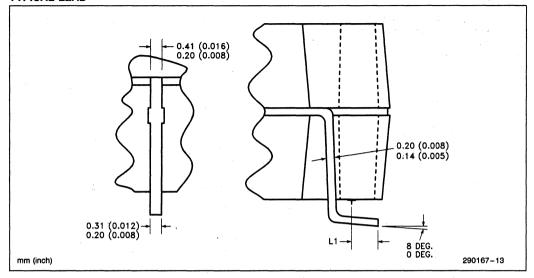

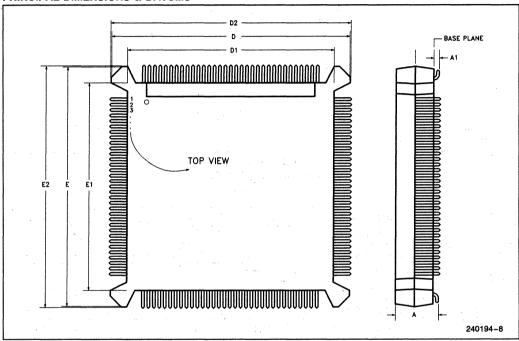

#### PLASTIC PACKAGING INFORMATION

(See Packaging Spec. Order # 231369)

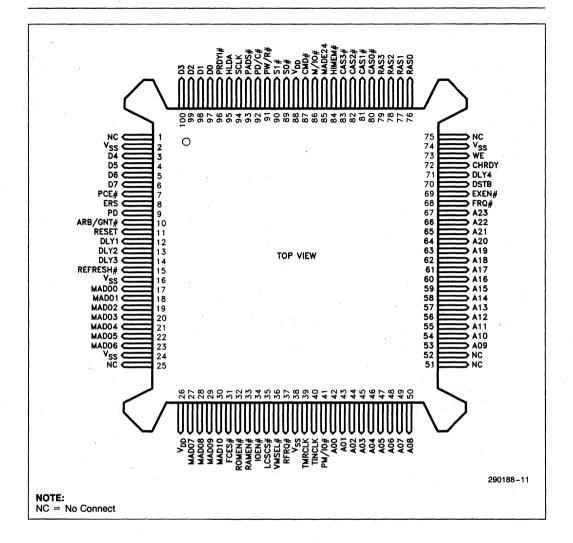

#### Introduction

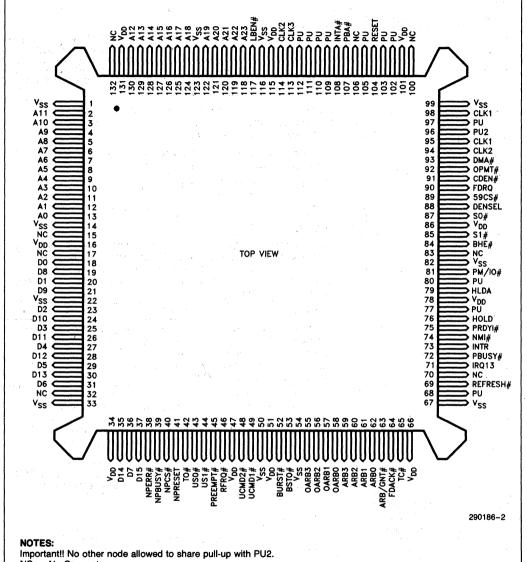

The individual components of Intel's Micro Channel Compatible Peripheral Chip Sets come in JEDEC standard Gull Wing packages (25 MIL pitch), with "bumpers" on the corners for ease of handling. Please refer to the accompanying table for the package associated with each device, and to the individual component specifications for pinouts. (Note that the individual pinouts are numbered consistently with the numbering scheme depicted in the accompanying figures.)

# MICRO CHANNEL COMPATIBLE PERIPHERAL FAMILY COMPONENT PACKAGES

| Component | Package                                  |

|-----------|------------------------------------------|

| 82303     | 100 Pin PQFP                             |

| 82304     | 132 Pin PQFP                             |

| 82306     | 100 Pin PQFP                             |

| 82307     | 132 Pin PQFP                             |

| 82308     | 100 Pin PQFP                             |

| 82309     | 100 Pin PQFP                             |

| 82706     | 132 Pin PQFP                             |

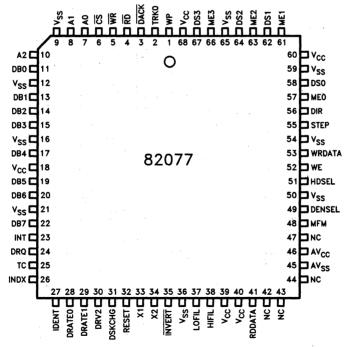

| 82077     | 68-Pin PLCC,<br>See Component Data Sheet |

#### PLASTIC QUAD FLAT PACK (PQFP)

#### PRINCIPAL DIMENSIONS & DATUMS

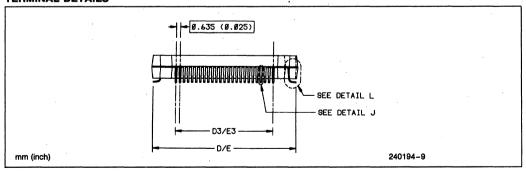

#### **TERMINAL DETAILS**

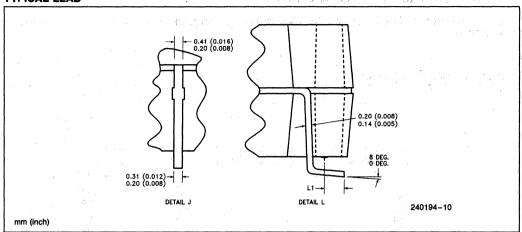

#### **TYPICAL LEAD**

# Case Outline Drawings Plastic Fine Pitch Chip Carrier 0.025 inch Pitch

#### 0.84 mm Pitch

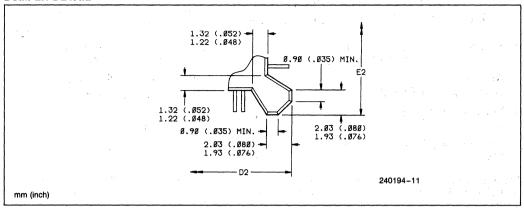

| Symbol | Description        | Min       | Max   | Min       | Max   | Min       | Max   | Min       | Max   |

|--------|--------------------|-----------|-------|-----------|-------|-----------|-------|-----------|-------|

| N      | Lead Count         | 10        | 00    | 132       |       | 100       |       | 132       |       |

| Α      | Package Height     | 0.160     | 0.170 | 0.160     | 0.170 | 4.06      | 4.32  | 4.06      | 4.32  |

| A1 .   | Standoff           | 0.020     | 0.030 | 0.020     | 0.030 | 0.51      | 0.76  | 0.51      | 0.76  |

| D, E   | Terminal Dimension | 0.875     | 0.885 | 1.075     | 1.085 | 22.23     | 22.48 | 27.31     | 27.56 |

| D1, E1 | Package Body       | 0.747     | 0.753 | 0.947     | 0.953 | 18.97     | 19.13 | 24.05     | 24.21 |

| D2, E2 | Bumper Distance    | 0.897     | 0.903 | 1.097     | 1.103 | 22.78     | 22.94 | 27.86     | 28.02 |

| D3, E3 | Lead Dimension     | 0.600 Ref |       | 0.800 Ref |       | 15.24 Ref |       | 20.32 Ref |       |

| L1     | Foot Length        | 0.020     | 0.030 | 0.020     | 0.030 | 0.51      | 0.76  | 0.51      | 0.76  |

Inch

mm

#### **REVISION HISTORY**

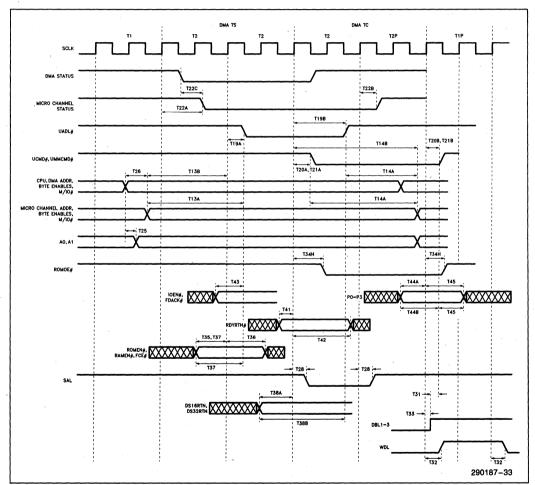

The A.C. Specifications of the 82306, 82307, 82308 and 82309 chips have been modified with respect to the 82310 Data Sheet Order Number 290167-001. These modifications apply to the 16 MHz and 20 MHz kits only.

#### 82306 Spec Revisions

- T1 changed from 14 ns to 15 ns at 16 MHz . . . from 12 ns to 15 ns at 20 MHz

- T2 changed from 10 ns to 4 ns at 16 MHz . . . from 7 ns to 4 ns at 20 MHz

- T16 changed from 180 ns to 230 ns at 16 MHz and 20 MHz

- T20 changed from 200 ns to 120 ns at 16 MHz and 20 MHz

#### 82307 Spec Revisions

- T1 changed from 14 ns to 15 ns at 16 MHz . . . from 12 ns to 15 ns at 20 MHz

- T2 changed from 10 ns to 4 ns at 16 MHz ... from 7 ns to 4 ns at 20 MHz

- T33 cap load C(L) changed from 50 pF to 25 pF

#### 82308 Spec Revisions

- T5A changed from 37 ns to 30 ns at 16 MHz and 20 MHz

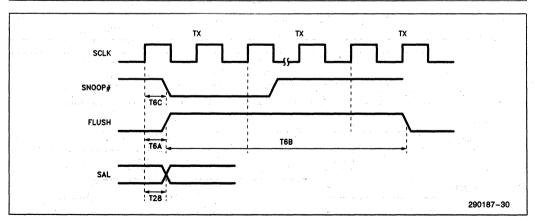

- T6A broken into two specs ... T6A for FLUSH, and T6C for SNOOP#

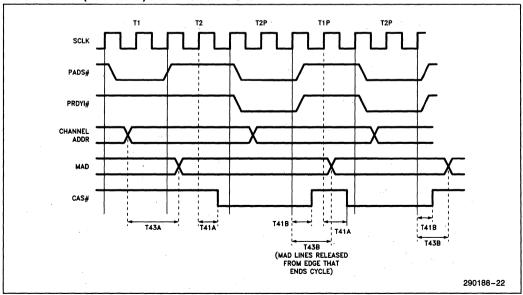

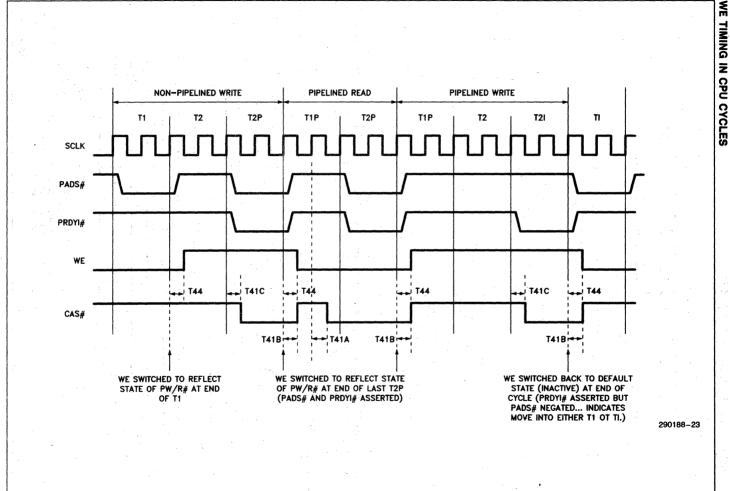

- T44 broken into two specs . . . T44A for Setup to SCLK and T44B for Setup to UCMD# . . . T44A left at 0 ns, but T44B changed to 3 ns

- T47C changed from 35 ns to 40 ns

#### 82309 Spec Revisions

- T18A changed from 45 ns to 30 ns at 16 MHz

- T18B changed from 50 ns to 38 ns at 16 MHz

- T18C changed from 50 ns to 35 ns at 16 MHz

- T27B changed from 30 ns to 33 ns

- T32B changed from 50 ns to 55 ns

- T32E (Min) changed from 8 ns to 4 ns

- T32E (Max) changed from 30 ns to 27 ns

- T32G (Min) changed from 6 ns to 4 ns

- T32I changed from 50 ns to 40 ns

- T33 (Min) changed from 8 ns to 5 ns

- T34 (Min) changed from 6 ns to 3 ns

- T34 (Max) changed from 26 ns to 27 ns

- T35 changed to 115 ns to 100 ns at 16 MHz and from 90 ns at 20 MHz

- T45 changed from 26 ns to 32 ns

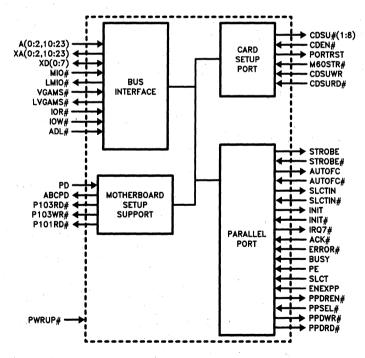

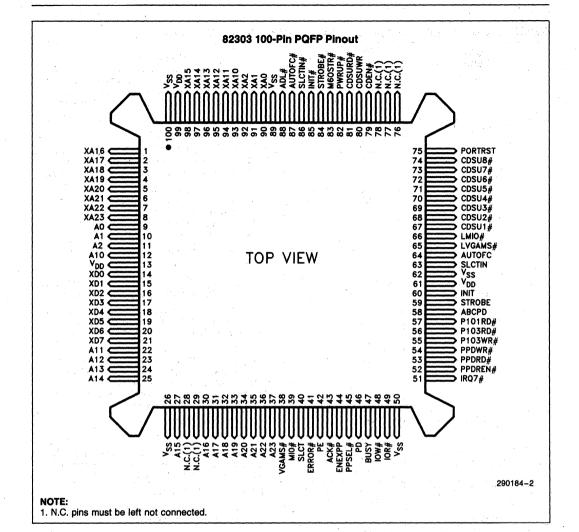

## 82303 LOCAL I/O SUPPORT CHIP

- High Integration—The 82304, 82303 and 82077 Floppy Disk Controller Replace 50 IC's in IBM Design

- Integrated Parallel Port

- Integrated Card Setup Port (96H)

- **■** Supports System Board Setup

- Integrated Peripheral Bus Address Latches

- **Low Power CHMOS Technology**

- 100-Pin Plastic Quad Flat Package

The 82303 Local Channel Support Chip, along with its companion chip (the 82304) and the 82077 Floppy Disk Controller, significantly reduce system cost, design effort, and form factor constraints by replacing 50 IC devices in an equivalent IBM system.

The 82303 integrates most all logic required to implement a parallel port. This port operates either as a standard parallel port or as a Microchannel architecture compatible "extended mode" (bi-directional) port. The 82303 also integrates the Card Setup Port (96H) and several peripheral bus address latches, and provides signals in support of system setup functions.

290184-1

#### Introduction

The 82303 is a high integration device intended for Microchannel compatible system designs. It integrates the Microchannel Card Setup Port, a parallel port, several peripheral bus address latches, and a variety of system board setup functions. The 82303, in conjunction with its sister chip the 82304 and the 82077 Floppy Disk Controller, replaces approximately 50 IC devices in an equivalent IBM system. Included as an appendix to this data sheet is a functional logic diagram of the 82303 that will facilitate understanding of the part. Note that the 82304 and 82303 integrate a variety of system ports. For programming and register level details, please refer to the IBM Technical Reference Manual.

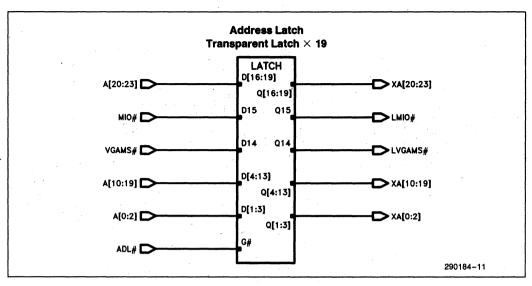

#### **Bus Interface**

The Bus Interface unit interfaces the 82303 to the Microchannel and peripheral busses. It inputs the unlatched Microchannel address, latches it for internal use, and makes the latched version available externally for other peripheral bus resources. It also provides additional latches for decodes generated from the Microchannel address.

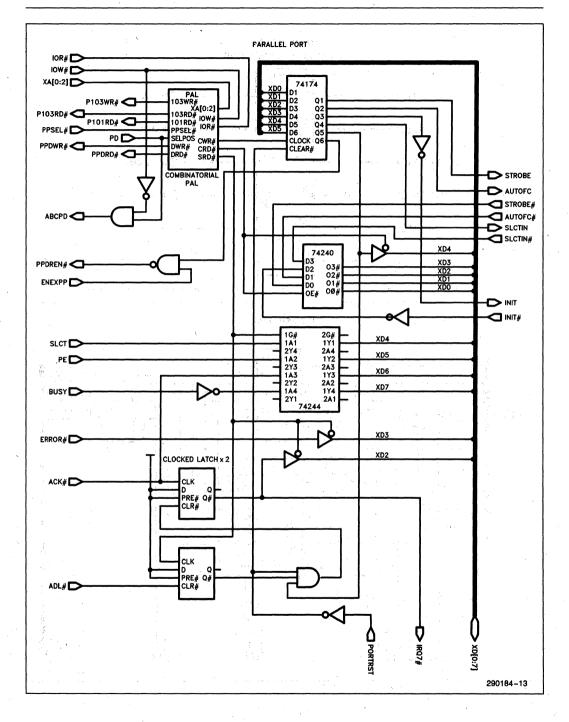

#### **Parallel Port**

The 82303 integrates most all logic required to implement a standard or "extended-mode" parallel

port. The only logic not integrated is that which directly drives the physical parallel port connector, specifically one '05 (open collector) inverter package and one '652 data buffer. (This allows the system design to stay clear of directly exposing a VLSI component to an external connector.) The parallel port can serve as LPT1, LPT2, or LPT3, as dictated by the decode received via the input parallel port decode PPSEL#.

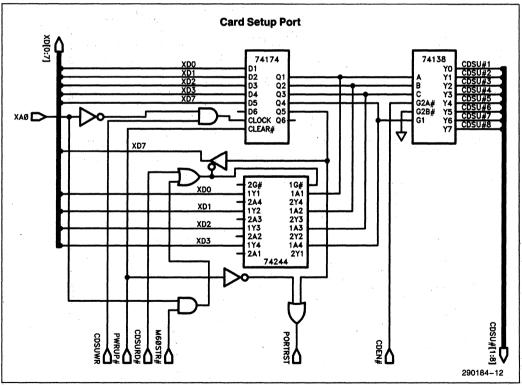

#### **Card Setup Port**

The 82303 integrates the Card Setup Port (96H), which generates the card setup lines to the individual Microchannel connectors. This port also features a software generated reset capability that resets the Microchannel, serial port, and parallel port independently of the rest of the system.

#### **Motherboard Setup Support**

The 82303 generates decoded read/write strobes for system board setup port 103H, and a read strobe for setup port 101H. It also generates a version of the system board POS decode (ABCPD) that is then forwarded to the 82309 Address Bus Controller. Note that other system board setup ports can be easily implemented externally using the same PD (POS Decode) that the 82303 uses.

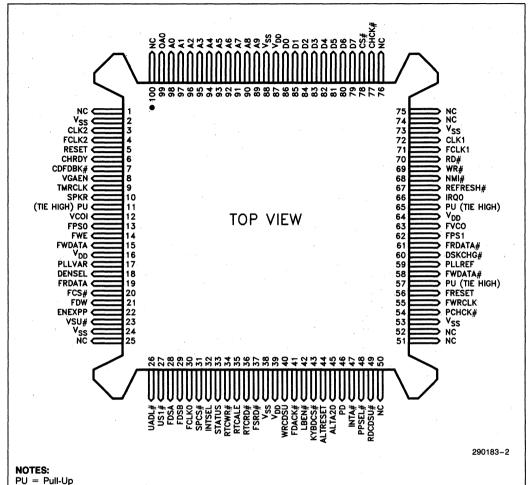

### 82303 Local Channel Support Chip Pin Definitions

| Signal<br>Name | Pin<br>Number             | 1/0      | Description                                                                                                                                                                                                                              |  |  |

|----------------|---------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PWRUP#         | 82                        | 1        | Power-up reset input. Brings 82303 to initial known state.                                                                                                                                                                               |  |  |

| A[0:2, 10:23]  | 9–12, 22–25,<br>27, 30–37 | <b>.</b> | Microchannel address inputs. These signals an internally latched. (Note that in systems in which a full 24-bit peripheral address is not required, the upper significant address latches may be used as general purpose decode latches.) |  |  |

| XA[0:2, 10:23] | 90-98, 1-8                | 0        | Peripheral Bus Address. These outputs are latched versions of the Microchannel address inputs.                                                                                                                                           |  |  |

| XD[0:7]        | 14-21                     | 1/0      | Bi-directional peripheral data bus.                                                                                                                                                                                                      |  |  |

| MIO#           | 39                        | 1        | Microchannel MIO# indicator.                                                                                                                                                                                                             |  |  |

| LMIO#          | 66                        | 0        | Latched Microchannel MIO# indicator. The MIO#/LMIO# pin combination may be used as a general purpose latch if LMIO# is not required.                                                                                                     |  |  |

| VGAMS#         | 38                        | 1        | VGA memory buffer decode.                                                                                                                                                                                                                |  |  |

# 82303 Local Channel Support Chip Pin Definitions (Continued)

| Signal<br>Name                      | Pin<br>Number          | 1/0 | Description                                                                                                                                                                                                                          |

|-------------------------------------|------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LVGAMS#                             | 65                     | 0   | Latched VGA memory buffer decode. The VGAMS#/LVGAMS# pin combination may be used as a general purpose latch if LVGAMS# is not required.                                                                                              |

| IOR#, IOW#                          | 49, 48                 | 1   | 82303 read/write strobes.                                                                                                                                                                                                            |

| ADL#                                | 88                     | I   | Microchannel ADL# input.                                                                                                                                                                                                             |

| PD                                  | 46                     | 1   | POS decode. Decode driven in response to accesses to system board setup Ports 100, 101, 103–107H.                                                                                                                                    |

| ABCPD                               | 58                     | 0   | Address Bus Controller (82309) POS decode. This is simply the PD input gated by an active IOW# signal, and insures that the 82309 does not see a decoding glitch.                                                                    |

| P101RD#, P103RD#,<br>P103WR#        | 57, 56,<br>55          | 0   | Various system board setup port read/write strobes.                                                                                                                                                                                  |

| CDSU#[1:8]                          | 67-74                  | 0   | Card setup signals to the Microchannel slots.                                                                                                                                                                                        |

| CDEN#                               | 79                     | ı   | Port 100-107H decode used as qualifier for card setup signals.                                                                                                                                                                       |

| PORTRST                             | 75                     | Ο,  | Microchannel reset signal. The "OR" of the power-up reset and the reset function built into Port 96H.                                                                                                                                |

| M60STR#                             | 83                     | l   | Model 60 strap. When low, the 82303 will drive<br>Port 96H data in either a Port 96 or 97H read.<br>(This is in keeping with the Model 50/60<br>definition.) When high, the 82303 will remain tri-<br>stated during a Port 97H read. |

| CDSUWR                              | 80                     | 1   | Port 96-97H write strobe.                                                                                                                                                                                                            |

| CDSURD#                             | 81                     | 1   | Port 96-97H read strobe.                                                                                                                                                                                                             |

| STROBE, AUTOFC,<br>SLCTIN, INIT     | 59, 64,<br>63, 60      | 0   | Parallel port control outputs. These signals are externally buffered with open collector inverters before driving the parallel port connector.                                                                                       |

| STROBE#, AUTOFC#,<br>SLCTIN#, INIT# | 84, 87,<br>86, 85      | ı   | Parallel port control inputs.                                                                                                                                                                                                        |

| IRQ7#                               | 51                     | 0   | Parallel port interrupt request.                                                                                                                                                                                                     |

| ACK#, ERROR#, BUSY,<br>PE, SLCT     | 43, 41, 47,<br>42, 40  | I   | Parallel port status inputs.                                                                                                                                                                                                         |

| ENEXPP                              | . 44                   | 1   | Enable parallel port extended mode. Allows parallel port to operate bi-directionally.                                                                                                                                                |

| PPSEL#                              | 45                     | ı   | Parallel port chip select.                                                                                                                                                                                                           |

| PPDREN#                             | 52                     | 0   | Enables the external '652 parallel port data buffer to be used bi-directionally. This signal is a function of the Control port direction bit (bit 5) and the ENEXPP input.                                                           |

| PPDWR#, PPRD#                       | 54, 53                 | 0   | Parallel port data buffer write/read strobes.                                                                                                                                                                                        |

| V <sub>DD</sub>                     | 13, 61, 99             |     | Power.                                                                                                                                                                                                                               |

| V <sub>SS</sub>                     | 26, 50, 62,<br>89, 100 |     | Ground.                                                                                                                                                                                                                              |

| N.C.                                | 28, 29, 76,<br>77, 78  |     | No Connect.                                                                                                                                                                                                                          |

#### 82303 PARAMETRICS ABSOLUTE MAXIMUM RATINGS\*

Case Temperature Under Bias . . . . - 40°C to +85°C Storage Temperature .....-65°C to +150°C Voltage to any Pin with Respect to Ground -0.3V to  $+(V_{CC} + 0.3)V$ DC Supply Voltage ( $V_{CC}$ ) ..... -0.3V to +7.0V

\*Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **D.C. CHARACTERISTICS** $T_C = 0^{\circ}C$ to $+70^{\circ}C$ , $V_{CC} = 5V \pm 10\%$

| Symbol          | Parameter                        | Min   | Max | Units  | Notes                                                |

|-----------------|----------------------------------|-------|-----|--------|------------------------------------------------------|

|                 |                                  | MILLI | Wax | Ullits | Notes                                                |

| VIL             | Input Low Voltage                |       | 0.8 | V      |                                                      |

| V <sub>IH</sub> | Input High Voltage               | 2.0   |     | ·V     |                                                      |

| V <sub>OL</sub> | Output Low Voltage               |       | 0.4 | ٧      | I <sub>OL</sub> = 4 mA (Note 1)                      |

| V <sub>OH</sub> | Output High Voltage              | 2.4   |     | ٧.     | I <sub>OH</sub> = 4 mA (Note 1)                      |

| V <sub>OL</sub> | Output Low Voltage               |       | 0.4 | V      | $I_{OL} = 2 \text{ mA (Note 2)}$                     |

| V <sub>OH</sub> | Output High Voltage              | 2.4   |     | ٧      | $I_{OH} = 2 \text{ mA (Note 2)}$                     |

| Icc             | Power Supply Current             |       | 180 | mA     | No DC Loads                                          |

| ILI             | Input Leakage Current            |       | ±10 | μΑ     | V <sub>SS</sub> < V <sub>IN</sub> < V <sub>CC</sub>  |

| loz             | TRI-STATE Output Leakage Current |       | ±10 | μΑ     | V <sub>SS</sub> < V <sub>OUT</sub> < V <sub>CC</sub> |

- 1. CDSU# [1:8], XA [0:2, 10:23], XD[0:7].

- 2. All outputs other than those listed in Note 1.

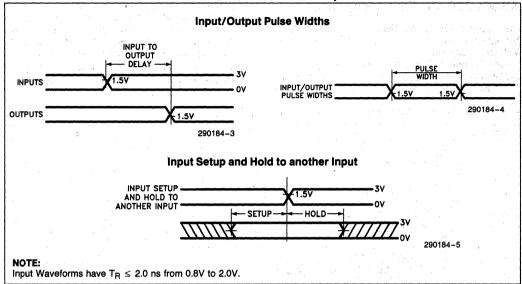

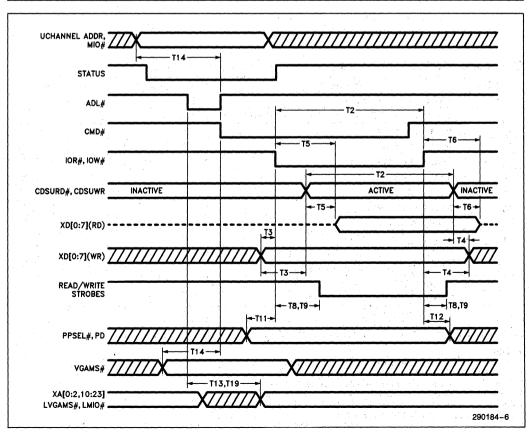

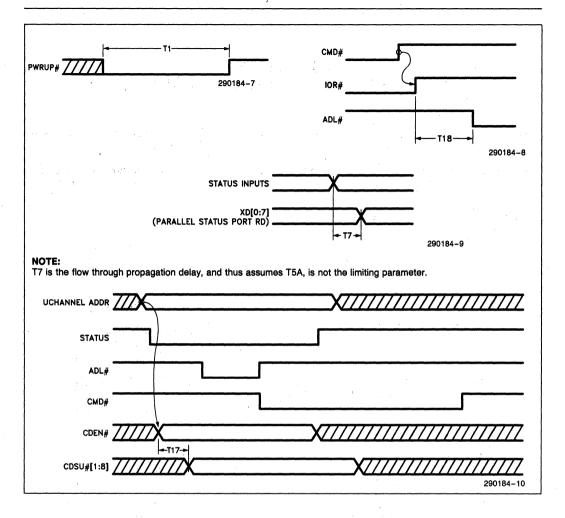

#### 82303 A.C. SPECIFICATIONS $T_C = 0^{\circ}C$ to $+70^{\circ}C$ , $V_{CC} = 5V \pm 10^{\circ}$

| Symbol          | Parameter                                   | Min   | Max | C <sub>L</sub> (pF) | Notes    |

|-----------------|---------------------------------------------|-------|-----|---------------------|----------|

| T <sub>1</sub>  | PWRUP#, Pulse Width                         | 500   |     |                     |          |

| T <sub>2</sub>  | IOR#, IOW#, CDSURD#, CDSUWR Pulse Width     | 170   |     |                     |          |

| Тз              | Write Data Setup                            | 25    |     |                     | (Note 1) |

| T <sub>4</sub>  | Write Data Hold                             | .10   |     | ·                   | (Note 2) |

| T <sub>5</sub>  | Read Data Valid Delay                       |       | 60  | 100                 | (Note 3) |

| T <sub>6</sub>  | Read Data Float Delay                       |       | 40  | 100                 | (Note 5) |

| T <sub>7</sub>  | Status Inputs to XD[0:7]                    |       | 35  | 100                 | (Note 6) |

| T <sub>8</sub>  | Write Strobe Delays                         |       | 35  | 50                  | (Note 7) |

| T <sub>9</sub>  | Read Strobe Delays                          |       | 40  | 50                  | (Note 8) |

| T <sub>11</sub> | PPSEL#, PD Setup to IOR#, IOW#↓             | 20    |     |                     |          |

| T <sub>12</sub> | PPSEL#, PD Hold from IOR#, IOW#↑            | 5.    |     |                     |          |

| T <sub>13</sub> | XA[0:2, 10:23] DLY from ADL# ↓              |       | 35  | 100                 |          |

| T <sub>14</sub> | A[0:2, 10:23], VGAMS#, MIO# Setup to ADL# ↑ | 30    | ,   |                     |          |

| T <sub>17</sub> | CDSU# [1:8] Delay from CDEN#                |       | 28  | 75                  |          |

| T <sub>18</sub> | IOR#↑ to ADL#↓                              | 30    |     |                     |          |

| T <sub>19</sub> | LVGAMS#, LMIO# Delay from ADL# \$\square\$  | 5 2 5 | 35  | 50                  |          |

- 1. To IOW# or CDSUWR active, whichever is appropriate.

- 2. From IOW# or CDSUWR inactive, whichever is appropriate.

- 3. From IOR# or CDSURD# active, whichever is appropriate.

- 5. From IOR# or CDSURD# inactive, whichever is appropriate.

- 6. Parallel port status inputs include SLCT, PE, BUSY, ERROR#, and ACK#.

- 7. Write strobes include P103WR# and PPDWR#.

- 8. Read strobes include P103RD#, P101RD#, and PPDRD#.

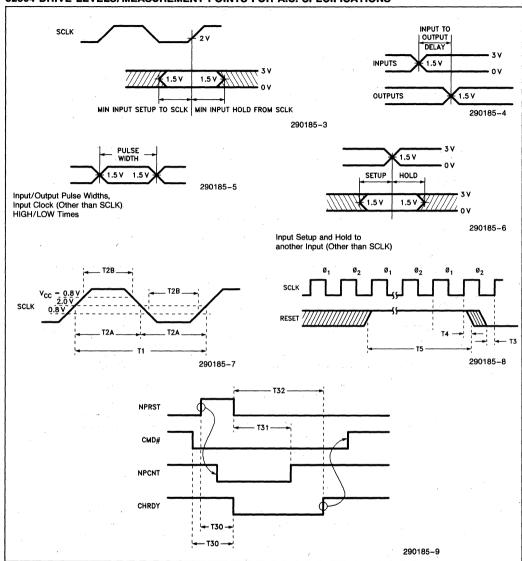

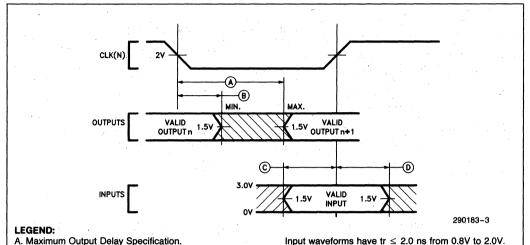

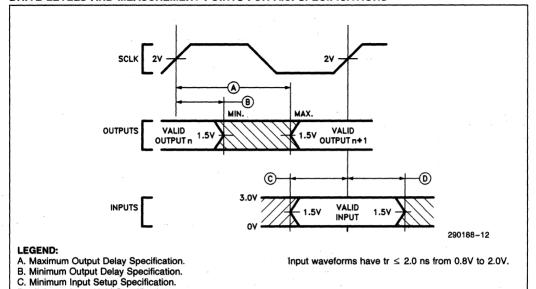

### 82303 Drive Levels/Measurement Points for A.C. Specifications

# APPENDIX 82303 INTERNAL LOGIC DIAGRAMS

These logic diagrams are provided to aid in understanding the basic functionality of the 82303, and should not be used to estimate signal loading, propagation delays, or any other timing behavior.

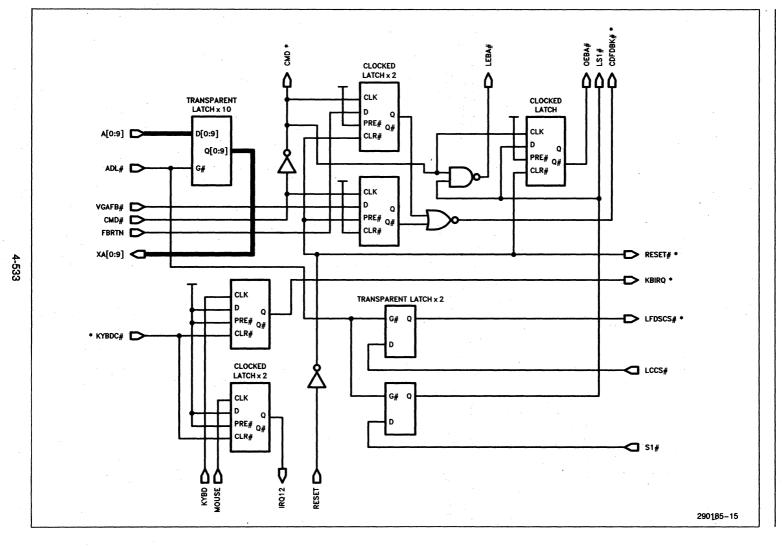

The clocked latches in the diagrams are functionally equivalent to 7474 type TTL latches. The transparent latches are equivalent to 74373 type TTL latches except that the gate input is active low rather than active high.

The truth table for the combinatorial PAL is as follows:

|   |    |    | RD |   |   |   |   |

|---|----|----|----|---|---|---|---|

| Р |    |    |    | Ρ | Р | Р |   |

| Р |    |    |    | P | P | Р | ĺ |

| S | ı  |    |    | D | С | s |   |

| E | 0  | X  | X  | R | R | R | ŀ |

| L | ·R | Α. | Α  | D | D | D | l |

| # | #  | 0  | 1  | # | # | # |   |

| 0 | 0  | 0  | 0  | 0 | 1 | 1 |   |

| 0 | 0  | 0  | 1  | 1 | 0 | 1 | l |

| 0 | 0  | 1  | 0  | 1 | 1 | Ó |   |

| SE |             |             |        |             | P O S 1     | P O S 1     |

|----|-------------|-------------|--------|-------------|-------------|-------------|

| LP | Ţ           | v           | v      |             | 0<br>1<br>R | 0<br>3<br>R |

| OS | O<br>R<br># | Х<br>А<br>2 | X<br>A | X<br>A<br>O | D<br>#      | D<br>#      |

| 1  | 0           | 0           | 0      | 1           | 0           | 1           |

| 1  | 0           | 0           | 1      | 1           | 1           | 0           |

|   |     | W | /R | , |   |

|---|-----|---|----|---|---|

| P |     |   |    | Р | Р |

| P |     |   |    | P | P |

| S | - 1 |   |    | D | C |

| Ε | 0   | X | X  | W | w |

| L | W   | Α | Α  | R | R |

| # | #   | 0 | 1  | # | # |

| 0 | 0   | 0 | 0  | 0 | 1 |

| 0 | 0   | 0 | 1  | 1 | 0 |

|    |   |   |   | · | PO |

|----|---|---|---|---|----|

| _  |   |   |   |   | S  |

| S  |   |   | , |   | 1  |

| E  | 7 |   |   |   | 0  |

| L. | 1 |   |   |   | 3  |

| P  | 0 | X | Х | X | W  |

| 0  | W | Α | Α | Α | R  |

| S  | # | 2 | 1 | 0 | #  |

| 1  | 0 | 0 | 1 | 1 | 0  |

L. YE

## 82304 LOCAL I/O SUPPORT CHIP

- High-Integration—The 82304, 82303 and 82077 Floppy Disk Controller Replace 50 IC's in IBM Design

- Supports I/O Peripherals ... Keyboard/ Mouse Controller, Serial/Parallel Ports, Configuration RAM, and Real Time Clock

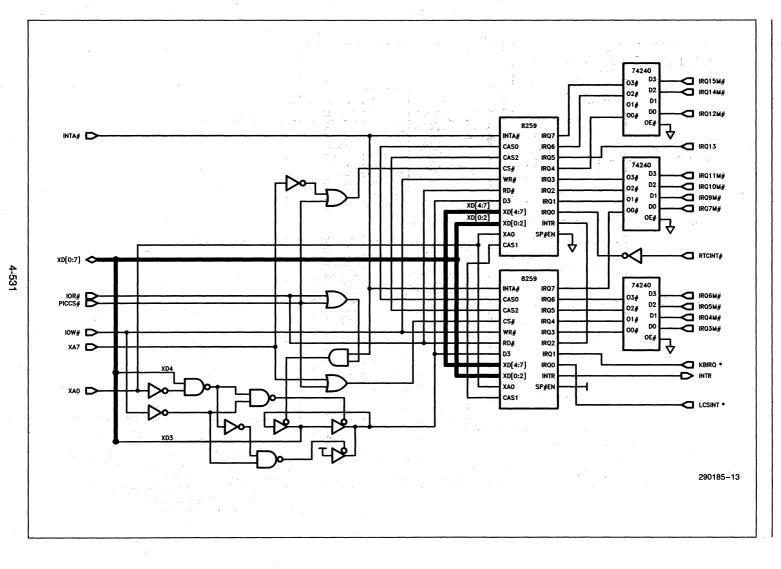

- Integrates Two 8259 PIC's and All Associated Logic

- Integrates Programmable Timer Counters 0, 2 and 3

- Supports VGA Controller on the Local Channel

- Integrates the OS/2 Optimized HOT A20 and HOT RESET Functions

- Integrates Variety of System Status/ Control Ports and Functions

- Low Power CHMOS Technology/132-Pin PQFP Package

The 82304 Local Channel Support Chip, along with its companion chip (the 82303) and the 82077 Floppy Disk Controller, significantly reduce system cost, design effort, and form factor constraints by replacing 50 IC devices in an equivalent IBM system.

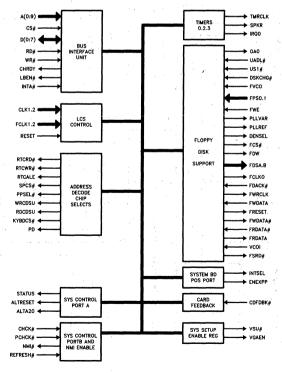

The 82304 integrates logic to support local bus I/O peripherals and the VGA Controller. Also integrated are three programmable timer/counters, two "8259-like" programmable interrupt controllers, and a variety of system status/control ports and functions. Integrated along with the 8259 PIC's is all logic required to make the PIC's Microchannel architecture compatible.

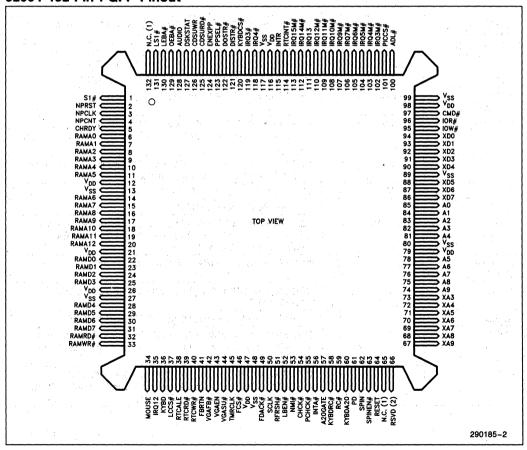

290185-1

#### INTRODUCTION

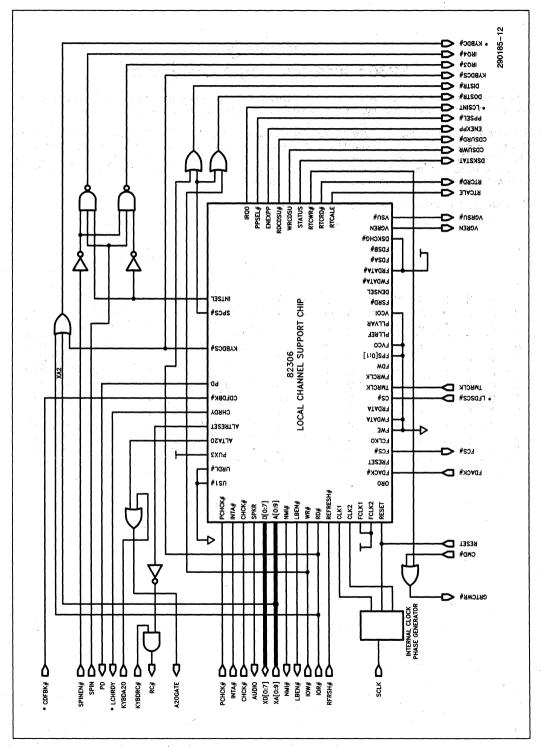

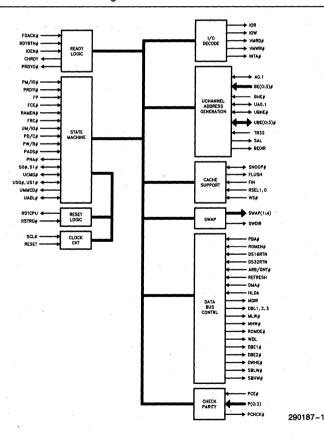

The 82304 is a high integration device intended for Microchannel compatible system designs. It essentially integrates the 82306 Local Channel Support chip, two 8259 Programmable Interrupt Controllers, and a wide assortment of TTL circuitry. The 82304, in conjunction with its sister chip the 82303 and the 82077 Floppy Disk Controller, replaces approximately 50 IC devices in an equivalent IBM system. Included as an appendix to this data sheet is a functional logic diagram of the 82304 that should facilitate understanding of the part. Note that the 82304, 82303 and 82077 integrate a variety of system ports. For programming and register level details, please refer to the IBM Technical Reference Manual, 82077 data sheet, and 8259A data sheet.

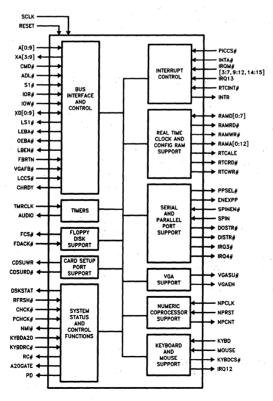

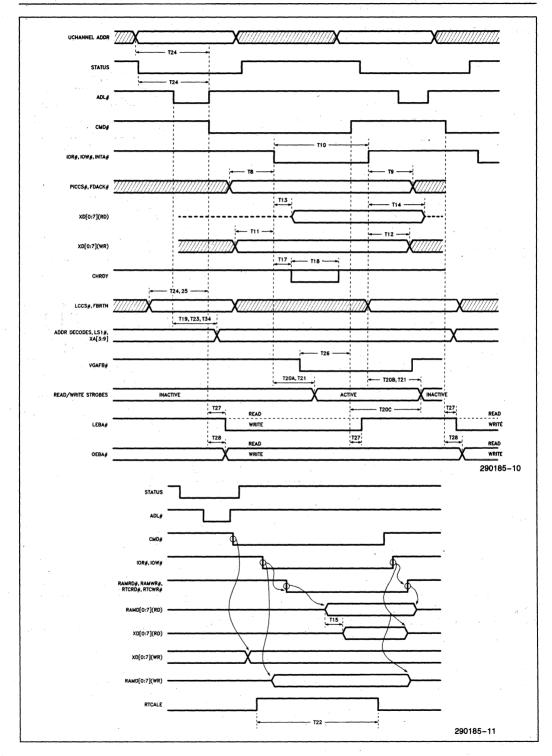

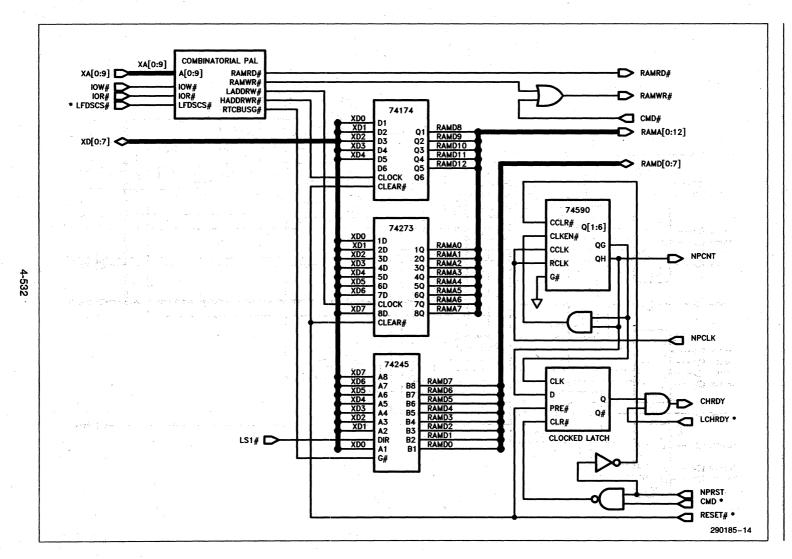

#### **BUS INTERFACE AND CONTROL**

The Bus Interface and Control unit interfaces the 82304 to the Microchannel and peripheral busses. It inputs the unlatched Microchannel address, latches it for internal use, and makes the latched version available externally for other peripheral bus resources. It also provides signals to control an external 74F543 latching data transceiver that sits between the Microchannel and peripheral data busses. The bus interface unit also provides functions such as cycle extension on behalf of slower peripherals, and support of the Microchannel architecture's system feedback function.

#### SYSTEM TIMERS

The 82304 integrates the timers required for multi-task time slice interrupt (timer 0), audio tone generation (timer 2), and "watch-dog" function (timer 3). These timers are accessed via ports 40, 42, 43, 44, and 47H.

#### FLOPPY DISK SUPPORT

The 82304 provides the decode signal required by the 82077 Floppy Disk Controller. The decode addresses ports 3F0–3F7H. The 82304 also inputs the 82077's DMA acknowledge in support of the system feedback function.

#### **VGA SUPPORT**

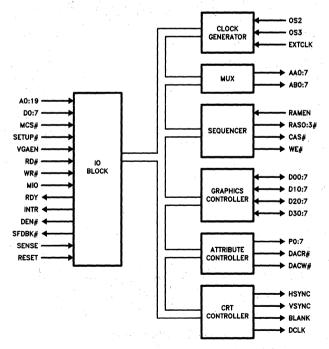

The 82304 supports the VGA setup and enable/disable functions. Specifically, bit 5 of integrated port

94H is used to put the VGA into setup mode, and this mode is reflected to the VGA on the 82304's VGASU# pin. Also, the 82304 integrates bit 0 of port 3C3H, which is used to enable/disable the system board VGA subsystem as indicated by the 82304's VGAEN output.

#### **CARD SETUP PORT SUPPORT**

The 82304 provides decoded read/write strobes for ports 96–97H. Port 96H is the card setup port, which is integrated on the 82303 chip. Port 97H is currently reserved by IBM.

#### INTERRUPT CONTROL

The 82304 integrates two 8259 Programmable Interrupt Controllers, and all additional logic required to make these interrupt controllers Microchannel architecture compatible. Specifically, the Microchannel definition requires that interrupts be active low and level sensitive. This allows a wire-OR system implementation. Integrated logic includes inverters for incoming interrupts, as the 8259 treats level sensitive interrupts as active high. Additionally, logic to inhibit the 8259's from being programmed in edge-triggered mode is integrated.

# REAL TIME CLOCK AND CONFIGURATION RAM SUPPORT

The 82304 integrates all logic required to support an external battery backed up real time clock chip and static RAM. Note that while the IBM implementation supports a 2K RAM, the 82304 makes provision to support either a 2K or 8K RAM. The real time clock is accessed via ports 70-71H, while the RAM is accessed via ports 74-76H. (RAM data is accessed via port 76H, while ports 74H and 75H serve as an indirect address latch for the RAM.) The 82304 also integrates the logic required to enforce the Microchannel architecture's password security function. Specifically, writes to port 70H are monitored. If a write to 70H is attempting to access offsets 38-3FH in the real time clock chip's onboard RAM, and if the security bit in 92H indicates that these offsets are off limits, then no address latch signal is generated to the real time clock chip.

# SERIAL AND PARALLEL PORT SUPPORT

The 82304 provides various functions in support of an external serial port chip (the 16550A), and a par-

allel port (integrated on the 82303 chip). The 82304 provides decoded read/writes strobes for the serial port chip, as well as converting a serial port interrupt into either IRQ3# or IRQ4#, depending on whether the serial port is configured as COMM1 or COMM2. When configured as COMM1, the serial port is decoded at ports 3F8-3FFH. As COMM2, the port is decoded from 2F8-2FFH. Configuration is done via the integrated system setup port 102H.

The 82304 generates a parallel port chip select that maps to LPT1, LPT2, or LPT3, depending on how system setup port 102H is programmed. As LPT1, the parallel port is decoded at ports 3BC, 3BD, 3BE, and 3BFH. LPT2 maps to ports 378, 379, 37A, and 37BH. LPT3 maps to 278, 279, 27A, and 27BH. The 82304 also generates a signal that indicates whether the parallel port is to operate in its normal output-only mode, or its "extended" bi-directional mode. The mode is selected via system setup port 102H.

#### NUMERIC COPROCESSOR SUPPORT

The 82307 DMA Controller, in response to a software command, issues a pulse to reset the 80387 or 803875X Numeric Coprocessor. The 82304 inputs this pulse and effectively stretches it out to insure that the 80387 reset input pulse is long enough to meet its internal reset requirements. (Note that the 80387 reset pulse out of the 82304 must be externally synchronized to the 80387 clock so as to convey the system phase to the 80387.) The 82304 also

manipulates CHRDY to extend the bus cycle that initiates the reset so as to tie up the CPU until the 80387's reset and initialization requirements are met.

#### **KEYBOARD AND MOUSE SUPPORT**

The 82304 provides a chip select for the 8742 Keyboard Controller. This decode maps to ports 60 and 64H. The 82304 also integrates the logic required to both latch and subsequently clear keyboard and mouse interrupts.

# SYSTEM STATUS AND CONTROL FUNCTIONS

The 82304 integrates a variety of system status and control functions and ports. Integrated ports include:

Port 61H System Control Port B

Port 92H System Control Port A

Port 91H Card Selected Feedback Register

Port 94H System Board Setup Port

Port 102H System Board POS Port

Port 70H NMI Enable (Write Only)

The functions and register level details of these ports are documented in the IBM Technical Reference.

#### 82304 LOCAL CHANNEL SUPPORT CHIP PIN DEFINITIONS

| Symbol          | Pin<br>No.      | Туре     | Description                                                                                                                                                                                                   |

|-----------------|-----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK            | 50              | 1.1      | INPUT CLOCK: Tied to same clock as host CPU.                                                                                                                                                                  |

| RESET           | 64              | · 1      | SYNCHRONIZED POWER-UP RESET: Resets 82304 and synchronizes internal clock to system phase.                                                                                                                    |

| A[0:9]          | 85-81,<br>78-74 | ' · I    | MICROCHANNEL ADDRESS: Address Lines are internally latched.                                                                                                                                                   |

| XA[3:9]         | 73–67           | 0        | PERIPHERAL BUS ADDRESS: These are latched versions of the Microchannel address.                                                                                                                               |

| CMD#            | 97              | <b>-</b> | MICROCHANNEL CMD# INPUT                                                                                                                                                                                       |

| ADL#            | 100             | ı        | MICROCHANNEL ADL# INPUT                                                                                                                                                                                       |

| S1#             | 1               | 1        | MICROCHANNEL S1# INPUT                                                                                                                                                                                        |

| IOR#, IOW#      | 96, 95          | 1        | 82304 READ AND WRITE STROBES                                                                                                                                                                                  |

| XD[0:7]         | 94-90,<br>88-86 | 1/0      | BI-DIRECTIONAL DATA BUS                                                                                                                                                                                       |

| LS1#            | 131             | 0        | LATCHED VERSION OF MICROCHANNEL S1# INPUT                                                                                                                                                                     |

| LEBA#,<br>OEBA# | 130,<br>129     | 0        | EXTERNAL 74543 DATA BUFFER CONTROL SIGNALS: These signals control data timing on the peripheral data bus.                                                                                                     |

| LBEN#           | 52              | 0        | LOCAL (PERIPHERAL) BUS ENABLE: The 82304 generates this in response to address decodes of peripheral bus ports. It is typically "OR"ed with other system qualifiers to enable the peripheral bus data buffer. |

# 82304 LOCAL CHANNEL SUPPORT CHIP PIN DEFINITIONS (Continued)

| Signal Name | Pin<br>No. | 1/0                  | Description                                                                                                                                                                                                                                      |

|-------------|------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *FBRTN      | 41         | e s <sup>e</sup> voi | SYSTEM FEEDBACK: This input receives the OR of the system feedback signals of the Microchannel slots. It is internally latched and "OR"ed with other feedback sources, and the result made available via a Port 91H read (Bit 0).                |

| VGAFB#      | 42         | ı                    | VGA FEEDBACK.                                                                                                                                                                                                                                    |

| LCCS#       | 37         |                      | LOCAL CHANNEL CHIP SELECT: Activated for the I/O address range 0-3FFH (CPU or DMA master) or 100-3FFH (Microchannel Master). LCCS# is internally latched.                                                                                        |

| CHRDY       | 5          | 0                    | CHANNEL READY: The 82304 deasserts CHRDY to extend accesses to certain peripheral bus resources, specifically the keyboard controller, real time clock and serial port. Also, CHRDY is used to tie up the CPU during numeric coprocessor resets. |

| TMRCLK      | 45         | 1                    | 1.193 MHz CLOCK INPUT: Drives clock inputs of system timers 0 and 2.                                                                                                                                                                             |

| AUDIO       | 128        | 0                    | OUTPUT OF SYSTEM TIMER 2 GATED BY BIT 1 OF PORT 61H: It drives the Microchannel audio sum node.                                                                                                                                                  |

| FCS#        | 46         | 0                    | FLOPPY DISK CONTROLLER (82077) CHIP SELECT: Responds to I/O range 3F0-3F7H.                                                                                                                                                                      |

| FDACK#      | 49         | ı                    | FLOPPY DISK CONTROL DMA ACKNOWLEDGE: Internally latched and "OR"ed with other system feedback sources.                                                                                                                                           |

| VGASU#      | 44         | 0                    | VGA SETUP: Puts the VGA into setup mode when active, according to Bit 5 of Port 94H.                                                                                                                                                             |

| VGAEN       | 43         | 0                    | VGA ENABLE: Enables/Disables motherboard VGA according to Bit 0 of Port 3C3H.                                                                                                                                                                    |

| CDSUWR      | 126        | 0                    | CARD SETUP WRITE STROBE: Active High command generated during writes to Port 96–97H.                                                                                                                                                             |

| CDSURD#     | 125        | 0                    | CARD SETUP READ STROBE: Active low command generated during reads from Port 96–97H.                                                                                                                                                              |

| DSKSTAT     | 127        | 0                    | FIXED DISK STATUS: Controls the fixed disk activity light. It is active when either Bit 6 or Bit 7 of Port 92H is set.                                                                                                                           |

| RFRSH#      | 51         | <b>l</b>             | REFRESH CYCLE INDICATOR: Diagnostics can monitor refresh activity via Bit 4 of Port 61H.                                                                                                                                                         |

| CHCK#       | 54         | . i. j.              | MICROCHANNEL CHECK INDICATOR: Used to report adapter errors.                                                                                                                                                                                     |

| PCHCK#      | 55         | ı                    | <b>DRAM PARITY ERROR:</b> Driven in response to motherboard memory parity errors.                                                                                                                                                                |

| NMI#        | 53         | 0                    | NON-MASKABLE INTERRUPT REQUEST TO CPU: This acts as an open drain output that allows for an external wire "OR" with other NMI sources.                                                                                                           |

| KYBDA20     | 60         | <br>                 | A20 GATE SIGNAL OUT OF THE KEYBOARD CONTROLLER:<br>Internally "OR"ed with the alternate A20 switch incorporated in Bit 1<br>of Port 92H.                                                                                                         |

| KYBDRC#     | 58         | . <b>I</b>           | CPU RESET SIGNAL OUT OF THE KEYBOARD CONTROLLER: It is internally "OR"ed with the alternate reset function of Bit 0 of Port 92H.                                                                                                                 |

| RC#         | 59         | 0                    | RESET CPU: Resets CPU via Port 92H (Bit 0) or the KYBDRC# input.                                                                                                                                                                                 |

| A20GATE     | 57         | 0                    | A20 GATE SIGNAL: The "OR" of Bit 1 of Port 92H and the KYBDA20 input.                                                                                                                                                                            |

# 82304 LOCAL CHANNEL SUPPORT CHIP PIN DEFINITIONS (Continued)

| Signal<br>Name              | Pin<br>No.          | 1/0 | Description                                                                                                                              |

|-----------------------------|---------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| PD                          | 61                  | 0   | POS DECODE: An active high decode of system board setup ports 100, 101, 103–107H. (Port 102H is integrated on the 82304.)                |

| PICCS#                      | 101                 | 1   | CHIP SELECT FOR THE INTEGRATED 8259 PROGRAMMABLE INTERRUPT CONTROLLERS (PIC)                                                             |

| INTA#                       | 56                  | I   | INTERRUPT ACKNOWLEDGE: Generated by the bus controller during interrupt acknowledge cycles.                                              |

| IRQM#<br>[3:7, 9:12, 14:15] | 102-110,<br>112-113 | l   | MICROCHANNEL INTERRUPT INPUTS.                                                                                                           |

| IRQ13                       | 111                 | ı   | INTERRUPT INPUT USED TO REPORT NUMERIC COPROCESSOR ERRORS.                                                                               |

| RTCINT#                     | 114                 | l   | INTERRUPT INPUT FROM REAL TIME CLOCK.                                                                                                    |

| INTR                        | 115                 | 0   | MASKABLE INTERRUPT REQUEST TO CPU.                                                                                                       |

| RAMD[0:7]                   | 22-25,<br>28-31     | 1/0 | REAL TIME CLOCK AND CONFIGURATION RAM DATA BUS.                                                                                          |

| RAMRD#,<br>RAMWR#           | 32, 33              | 0   | READ/WRITE STROBES TO CONFIGURATION RAM: Generated during accesses to Port 76H.                                                          |

| RAMA[0:12]                  | 6-11,<br>14-20      | 0   | CONFIGURATION RAM ADDRESS BUS: Internal RAM address latches are written to via Ports 74-75H.                                             |

| RTCALE                      | 38                  | 0   | REAL TIME CLOCK ADDRESS LATCH ENABLE.                                                                                                    |

| RTCRD#,<br>RTCWR#           | 39, 40              | 0   | REAL TIME CLOCK READ/WRITE STROBES.                                                                                                      |

| PPSEL#                      | 123                 | 0   | PARALLEL PORT CHIP SELECT: Maps to LPT1, LPT2, or LPT3 as controlled by Bits 5 and 6 of system board setup Port 102H.                    |

| ENEXPP                      | 124                 | 0   | PARALLEL PORT EXTENDED MODE ENABLE: This mode is controlled via bit 7 of system board setup Port 102H.                                   |

| SPINEN#                     | 63                  | 1   | SERIAL PORT INTERRUPT ENABLE.                                                                                                            |

| SPIN                        | 62                  | ı   | SERIAL PORT INTERRUPT.                                                                                                                   |

| IRQ3#,<br>IRQ4#             | 119, 118            | 0   | SERIAL PORT INTERRUPT: Configured to either COMM1 (IRQ4#) or COMM2 (IRQ3#). Selection is done via Bit 3 of system board setup Port 102H. |

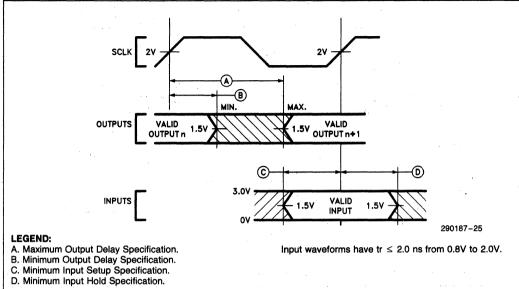

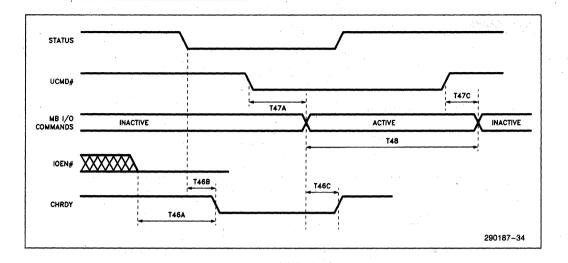

| DOSTR#,<br>DISTR#           | 122, 121            | 0   | WRITE/READ STROBES FOR SERIAL PORT.                                                                                                      |