# Implementation of Vector Control for PMSM Using the TMS320F240 DSP

Michel Platnic

Digital Signal Processor Solutions

#### **Abstract**

This document presents a solution for controlling a permanent magnet synchronous motor using the Texas Instruments (TI™) TMS320C24x digital signal processor (DSP). The new TMS320C24x family of DSPs offers a cost-effective design of intelligent controllers for brushless motors that can fulfill enhanced operations consisting of fewer system components, lower system cost, and increased performances. The control method presented relies on the field orientated control (FOC) together with a field-weakening operation. This algorithm maintains efficiency in a wide range of speeds, above nominal speed, and takes into consideration torque changes with transient phases by controlling the flux directly from the rotor coordinates. This report describes a practical solution and corresponding results.

#### **Contents**

| Introduction .         |                                                                                                         | 3  |

|------------------------|---------------------------------------------------------------------------------------------------------|----|

| Application D          | Description                                                                                             |    |

| Convention.            |                                                                                                         |    |

| FOC Softwa             | re Organization                                                                                         | 11 |

| Parameter A            | daptation                                                                                               | 15 |

| Field Weake            | ning                                                                                                    | 27 |

| Results                |                                                                                                         | 31 |

| User Interfac          | e                                                                                                       | 36 |

| Conclusion             |                                                                                                         | 36 |

| References.            |                                                                                                         | 37 |

| Appendix A.            | TMS320F240 FOC Software                                                                                 | 37 |

| Appendix B.            | Linker File                                                                                             | 64 |

| Appendix C.            | Sinewave Table                                                                                          | 65 |

| Appendix D.            | Qbasic User Interface                                                                                   | 67 |

|                        | Figures                                                                                                 |    |

| Figure 1.<br>Figure 2. | Three-Phase Synchronous Motor with One Permanent Magnet Pair Pole Rotor Three BEMF Waveforms at 1000rpm |    |

| Figure 3.              | Inverter Topology                                                                                       |    |

| Figure 4.              | Top View of TMS320F240 EVM Board                                                                        | 6  |

| Figure 5.              | ACPM750E with a MCK240                                                                                  |    |

| Figure 6.     | Stator Current and Magnet Flux Space Vectors in the d,q Rotating Reference Frame and its |  |

|---------------|------------------------------------------------------------------------------------------|--|

|               | Relationship with the a, b, c Stationary Reference Frame8                                |  |

| Figure 7.     | PMSM Control with Field Orientation8                                                     |  |

| Figure 8.     | Format Correspondence Diagram                                                            |  |

| Figure 9.     | FOC Software Initialization and Operating System11                                       |  |

| Figure 10.    | General Software Flowchart                                                               |  |

| Figure 11.    | Control Algorithm Timing                                                                 |  |

| Figure 12.    | Waiting Loop/User Interface                                                              |  |

| Figure 13.    | Control Routine Block Diagram14                                                          |  |

| Figure 14.    | Block Diagram of the FOC Including Closed Loop Field Weakening Control15                 |  |

| Figure 15.    | Current Measurement Chain                                                                |  |

| Figure 16.    | Current Sensing Interface Block Diagram17                                                |  |

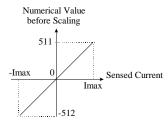

| Figure 17.    | Sensed Current Values before Scaling18                                                   |  |

| Figure 18.    | Sinθ Calculation Using the Sine Look-Up Table23                                          |  |

| Figure 19.    | SVPWM, Vectors and Sectors                                                               |  |

| Figure 20 As: | signing the Right Duty Cycle to the Right Motor Phase27                                  |  |

| Figure 21.    | Field Weakening Real Operation                                                           |  |

| Figure 22.    | Maximum and Nominal Torque vs Speed28                                                    |  |

| Figure 23.    | Field Weakening Voltage Constraints29                                                    |  |

| Figure 24.    | Control Range of a PMSM in Steady State29                                                |  |

| Figure 25.    | Field Weakening Function Structure30                                                     |  |

| Figure 26. Sp | peed Transient from 0 rpm to 1000 rpm32                                                  |  |

| Figure 27.    | Speed Transient from 0 rpm to 3000 rpm at Nominal Torque                                 |  |

| Figure 28.    | Speed Transient from -1000 rpm to 1000 rpm at Nominal Torque34                           |  |

| Figure 29.    | Speed Transient from 0 rpm to 3000 rpm Graph1 without Torque, Graph2 with 1.1Nm34        |  |

| Figure 30.    | Steady-State Speed at Nominal Speed and 33% Above at Maximal Torque35                    |  |

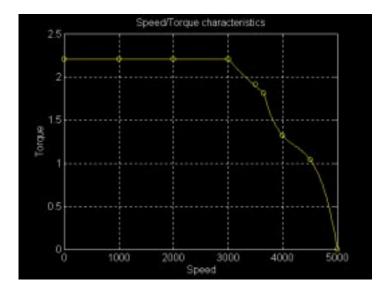

| Figure 31.    | Speed/Torque Plot35                                                                      |  |

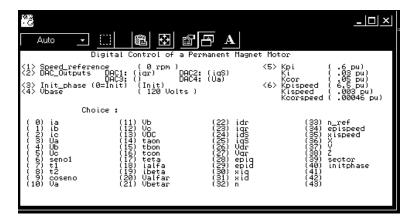

| Figure 32.    | User Screen                                                                              |  |

|               |                                                                                          |  |

#### Introduction

The Texas Instruments TMS320F240 DSP Controller is suitable for a wide range of motor drives. The TMS320F240 provides a single chip solution by integrating on-chip a high computational power along with all of the peripherals necessary for electrical motor control. The main effect of this combination is the possible implementation of advanced controls such as vector control. High range controls increase system performance, reliability, efficiency, and cost. This application report describes a speed control implemented on a TMS320F240 for a three-phase Permanent Magnet drive with sinewave currents.

## The AC Permanent Magnet Motor

There are mainly two kinds of three-phase synchronous motors (SM). One uses rotor windings fed from the stator. The other one uses permanent magnets.

A motor fitted out with rotor windings requires brushes to obtain its current supply and generate the rotor flux. The contacts are, in this case, made of rings and do not have any commutator segment. The lifetime of both the brushes and the motor may be similar. The drawbacks of this structure – maintenance needs and lower reliability – are then limited.

Replacing common rotor field windings and pole structure with permanent magnets put the motor into the category of brushless motors. It is possible to build brushless permanent magnet motors with any even number of magnet poles. The use of magnets enables an efficient use of the radial space and replaces the rotor windings, therefore suppressing the rotor copper losses. Advanced magnet materials permit a considerable reduction in motor dimensions while maintaining a very high power density.

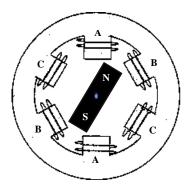

Figure 1. Three-Phase Synchronous Motor with One Permanent Magnet Pair Pole Rotor

The application studied in this report concerns the permanent magnet motor.

#### The Sinewave Currents

Two configurations of permanent magnet brushless motor drives are usually considered, depending on the back-electromagnetic force (BEMF) waveform:

Sinusoidal typeTrapezoidal type

Different control strategies (and control hardware) are implemented for each.

The trapezoidal BEMF motor is usually called the DC brushless motor (BLDC). Its appropriate control turns the stator phases on and off using a coarse rotor position. This control is described in the application report, *Implementation of a Speed Controlled Brushless DC Drive Using TMS320F240*, literature number BPRA064.

Sinewave stator currents drive the sinusoidal BEMF drive called the three-phase permanent magnet synchronous motor (PMSM). The stator magnetic field is set in accordance to the rotor field. This application report describes the TMS320F240 DSP Controller together with system considerations that allow high performance to be extracted from this category of motor drives, also called BLDC 3 phases-on.

# **Application Description**

#### **Motor Characteristics**

The synchronous machine with permanent magnets described in this application report is a three-phase (Y) connected motor. The motor includes the following characteristics:

|     | Stator phase line-to-line inductance: 4.8mH |

|-----|---------------------------------------------|

|     | Line-to-line resistance: $2.1\Omega$        |

|     | Pole pairs: 3                               |

|     | Nominal Torque Tn: 2.2Nm                    |

|     | Nominal speed: 3000rpm                      |

|     | Motor nominal power Pn: 690W                |

|     | Mechanical time constant: 1.5ms             |

|     | Electrical time constant: 2.3ms             |

|     | Thermal time constant: 30min                |

|     | Torque constant: 0.76Nm/A rms               |

|     | Voltage constant: 65Vpk/krpm                |

|     | Magnet material: NdFeB                      |

| The | e above values are given at 20°C.           |

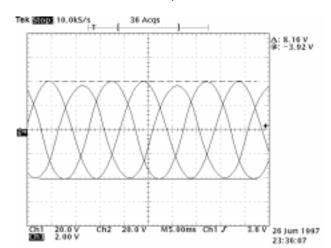

The back electromagnetic force has a sinusoidal shape and its stator phases are supplied with sinusoidal currents.

Figure 2. Three BEMF Waveforms at 1000rpm

#### The Power Electronics Hardware

The ACPM750E used in this application is built around the 750W POWIRTRAIN integrated power stage IRPT1056C from International Rectifier, which includes a rectifier bridge and a three-phase ultra-fast IGBT inverter.

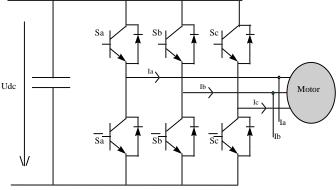

The converter topology supports either sinusoidal currents (three phases ON operation) or direct currents (two phases ON operation). The first control is implemented in this application report. Figure 3 shows the inverter topology used. All of the power device securities are wired (Shutdown, Fault, Clearfault, Itrip, reverse battery diode, varistor peak current protection). The current sensing is insured by 2 L.E.M. directly interfaced with the TMS320F240. The power board also supports the voltage supply of an incremental encoder.

Figure 3. Inverter Topology

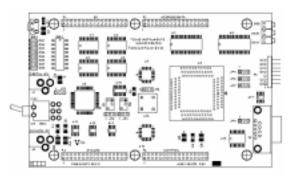

#### The DSP Control Board

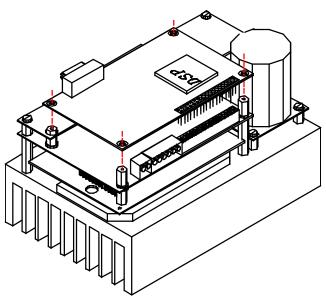

The control hardware is the Texas Instruments TMS320F240 Evaluation Module (EVM). It can be directly interfaced to the power electronics board. This evaluation board has a TMS320F240 DSP Controller with an oscillator, JTAG link, RS232 link, and the necessary output connectors. See Figure 4 depicting the EVM board.

Figure 4. Top View of TMS320F240 EVM Board

# **An Integrated Solution**

This part describes the features of the ACPM750E and provides an overview of the intelligent AC drive unit, which results when the ACPM750E is connected with Technosoft's Motion Control Kit MCK240 board.

The ACPM750E is a power module for three-phase AC motors, which can directly be controlled with the MCK240 board. Both devices use the universal motion control bus (MC-BUS). They can be connected by simply plugging the MCK240 on top of the ACPM750E.

The ACPM750E offers galvanic isolated feedback signals for two motor currents and the DC bus voltage. Motor speed provided by a tachometer can be measured through an adjustable-gain circuit. Motor position given by an incremental encoder and three Hall sensor signals can also be read through the MCK240.

When the ACPM750E is combined with the MCK240, it results in an intelligent AC drive unit. This unit represents an ideal development platform for design and implementation of high performance control algorithms for three-phase AC motors using the Texas Instruments TMS320F240 ('F240) DSP controller.

Figure 5. ACPM750E with a MCK240

# **Field Orientated Control Principle**

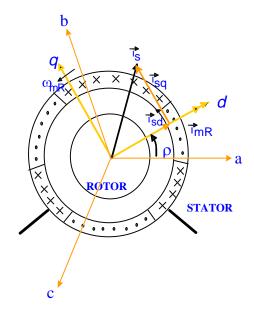

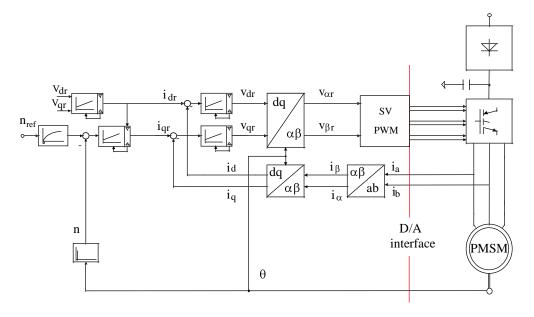

The vector control principle consists of controlling the angle and amplitude components of the stator field. For ease of motor equation representation, the components of the stator current are represented in a rotating reference frame d,q aligned with the rotor axis, i.e., with the magnet flux. The motor torque for a permanent magnet machine depends only on the quadrature (q) current component (torque component). In this case, the most convenient control strategy is to set to zero the direct (d) current component to minimize the torque vs. current ratio and then increase the motor (and converter) efficiency. The control of current components requires the knowledge of the instantaneous rotor position.

Figure 6. Stator Current and Magnet Flux Space Vectors in the d,q Rotating Reference Frame and its Relationship with the a, b, c Stationary Reference Frame

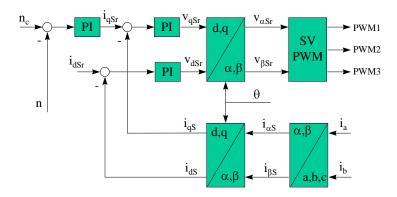

The control scheme proposed for the PM synchronous motor drive is shown in Figure 7. It is based on the vector control principle arranged in the d,q rotating frame introduced in the TI application report, DSP Solution for Permanent Magnet Asynchronous Motor, literature number BPRA044. Two of three motor phase currents are measured with current sensor, the Clarke transform is applied and then modifies a three-phase system into a two-phase orthogonal system. The output of this transformation is indicated as i<sub>aS</sub> and i<sub>8S</sub>. These two components of the stator current are the input of the Park transform that gives the stator current in the d,q rotating reference frame. Note that this second transformation needs the rotor flux position. The quadrature current component is regulated to the reference value given by the speed controller, while the direct current component is set to zero to minimize the current vs. torque ratio of the motor. The outputs of the current controllers, representing the voltage references, are then impressed to the motor using the Space Vector Modulation technique, once an inverse transformation from the rotating to the fixed stator reference is performed. An outer speed control loop completes the scheme. All of the controllers used are standard PI regulators. Figure 7 shows this basic scheme.

Figure 7. PMSM Control with Field Orientation

#### Convention

#### **Software Variables**

$i_a$ ,  $i_b$ ,  $i_c$  phase currents

$i_{S_{\alpha}}$ ,  $i_{S_{\beta}}$  stator current  $(\alpha,\beta)$  components  $i_d$  flux component of the stator current torque component of the stator current

$i_{dr}$ ,  $i_{qr}$  flux and torque command

$\theta$  rotor flux position

$v_d$ ,  $v_q$  (d,q) components of the stator voltage

$V_{S_{\alpha} Tef}$ ,  $V_{S_{\beta} Tef}$  ( $\alpha, \beta$ ) components of the stator voltage (input of the SVPWM)

*V<sub>DC</sub>* DC bus voltage

*VDCinvTc* constant using in the SVPWM

$v_a$ ,  $v_b$ ,  $v_c$  voltage reference used for sector determination in the SVPWM

sectorsector variable used in SVPWMt1, t2time vector application in SVPWM

t<sub>aon</sub>, t<sub>bon</sub>, t<sub>con</sub> PWM commutation instant

X, Y, Z SVPWM variables

n, n<sub>ref</sub> speed and speed referencel<sub>idrmin</sub>, l<sub>idrmax</sub> voltage regulator output limitation

*I<sub>smax</sub>* phase current limitation

$i_{qrmin}$ ,  $i_{qrmax}$  speed regulator output limitation  $V_{min}$ ,  $V_{max}$  d,q current regulator output limitation

$K_{i}$ ,  $K_{pi}$ ,  $K_{cor}$  current regulator parameters  $K_{ispeed}$ ,  $K_{pispeed}$ ,  $K_{corspeed}$  speed regulator parameters

Kiweak, Kpiweak, Kcorweak field weakening regulator parameters

SPEEDSTEPspeed loop periodspeedstepspeed loop counter

encincr, encoder pulses storing variablespeedtmp number of pulses in SPEEDSTEP

#### **Base Values**

Since the TMS320F240 is a fixed-point DSP, a per unit (p.u.) model is used for the motor variable representations. In this model all quantities are referred to base values. The advantage of this method is that it can be used for any motor (different parameters, power, user requirements, etc.) by simply changing the base values without changing any part of the software.

The base values are determined from the nominal values with the following equations:

$$I_{base} = \sqrt{2}I_n$$

$$V_{base} = \sqrt{2}BEMF$$

$$\omega_{base} = 2\pi f_n$$

Where I<sub>n</sub>, the BEMF are rms values. The BEMF is measured at nominal speed.

The base RMS values of the motor used in this synchronous drive are as follows:

$$\begin{split} I_{base} &= \sqrt{2}I_n = \sqrt{2} \cdot 2.9 = 4.1A \\ V_{base} &= 3*65 \cong 195V \\ \omega_{base} &= 2\pi f_n = 2\pi \cdot 50 = 314.15 \frac{rad}{\text{sec}} \end{split}$$

The quantities in p.u. are defined:

$$i = \frac{I}{I_{base}}$$

$$v = \frac{V}{V_{base}}$$

$$speed = \frac{synchronous\ speed\ (\omega)}{\omega_{base}}$$

#### **Numerical Consideration**

The p.u. model has been developed so that the software representation of speed, currents, and voltages are equal to one when the drive has reached its nominal speed under nominal load. Knowing that during transients, the current might reach higher values than the nominal current ( $I_{base}$ ) to achieve a short response time. Assuming also that the motor speed range might be extended above the nominal speed ( $\omega_{base}$ ), every per unit value may be greater than one. This fact forces the implementation to handle these situations and thus determine the best suited numerical format.

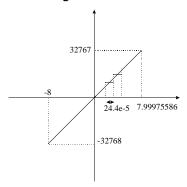

#### The Numeric Format

The numeric format used is 4 bit for integer number and 12 bit for fractional number. This numeric format is noted: 4.12 format. The resolution of this format is:

$$\frac{1}{2^{12}} = 0.00024414$$

The correspondence from rated magnitude to 16 bit DSP variable is the following:

$$(-8; 7.99975586) \Leftrightarrow (-32768; 32767)$$

This format has been chosen because the drive control quantities are (most of the time) not greater than four times their nominal values (in other words not greater than four when the per unit model is considered). Otherwise, a different format will be chosen. So using a representation range of [-8;8] ensures that the software values can handle each drive control quantity not only during steady state operation but during transient operation as well.

In this format if the p.u. variable is 1, the correspondent word is 01000h ( $2^{12}$ =4096). This representation allows for both of the above mentioned variables to be eight times bigger than the base quantities.

With sign extension mode set, the link between the real quantity and its 4.12 representation is given by Figure 8.

Figure 8. Format Correspondence Diagram

# **FOC Software Organization**

# **Software Synchronization**

This software is based on two modules: the initialization and control modules. The first one is performed only once at the beginning. The second module is based on a waiting loop interrupted by the PWM underflow event. When this interrupt flag is set the corresponding Interrupt Service Routine (ISR) is acknowledge and serviced.

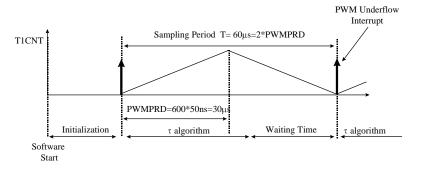

Figure 9 shows the time diagram for the initialization and the operating system.

Figure 9. FOC Software Initialization and Operating System

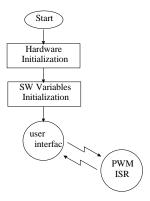

The complete FOC algorithm is computed within the PWM ISR and thus runs at the same frequency as the PWM frequency. The waiting loop could be easily replaced by a human machine interface. The interface software presentation is beyond the scope of this report but is useful to fit the control code and to monitor the control variables. The overview of the software is given in the flow chart below:

Figure 10. General Software Flowchart

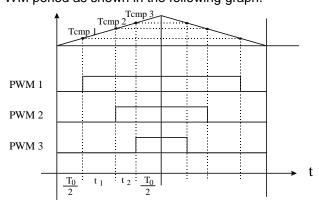

The DSP Controller Full Compare Unit is handled to generate the necessary pulsed signals to the power electronics board. It is set to generate symmetrical complementary PWM signals at the frequency of 16.6kHz with TIMER1 as time base and with the DEADBAND unit disabled. The sampling period (T) of  $60\mu$ s can be achieved by setting the timer period T1PER to 600 (PWMPRD=258h).

Figure 11. Control Algorithm Timing

#### Flow Chart

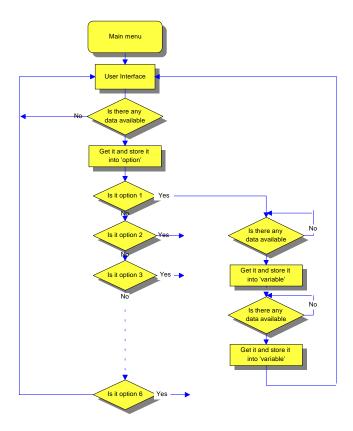

After the F240 features and variable initializations, the software jumps to the waiting loop. Below is presented the user interface. It is interrupted every time an interrupt occurs to start the control. This algorithm is asynchronous from the control and uses the MIPS not used by the control code. It behaves like a waiting loop.

Figure 12. Waiting Loop/User Interface

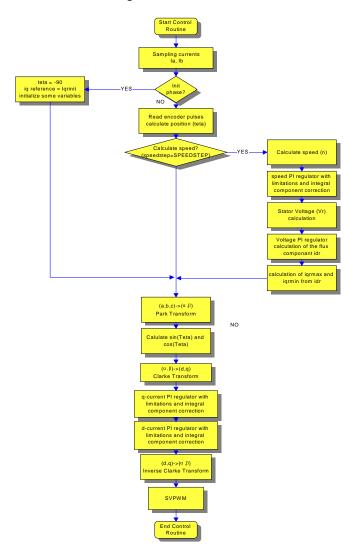

The next block diagram shows the control interrupt service routine. It is executed at the same frequency as the PWM.

Figure 13. Control Routine Block Diagram

# **Block Diagram**

Figure 14. Block Diagram of the FOC Including Closed Loop Field Weakening Control

# **Parameter Adaptation**

This section deals with parameter adaptation depending on the motor specifications. Changes will be done depending on motor poles, rated speed, encoder resolution and current sensor scaling. The proportional integral regulators will be explained for the user to handle the coefficient optimization. All of the parameter adaptation described here needs to be done in the initialization part of the software.

#### **Motor Poles**

Depending on the motor poles, the pulse increments have to be multiplied by Kencoder so that the number of QEP counts is equal to 360° after an electrical period (the angle 360° is equivalent to 1000h). In the general case Kencoder is calculated as follow:

$$Kencoder = N * \frac{1024}{Encoder\_resolution}$$

N is the number of pair poles.

In the case of a three-pair pole motor having a 1024 pulse encoder, set the variable Kencoder to 3 and make a filter as follows:

| Kencoder            | .word                    | 0c000h | ;equivalent to 3.0 in 4.12 format                                                                                                                                           |

|---------------------|--------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lt                  | encoder                  |        | ;multiply encoder pulses by Kencoder to have therotor electrical position                                                                                                   |

| mpyu<br>pac         | Kencoder                 |        | ;encoder pulses = 1365 -> theta = 0fffh = 360 degrees<br>;encoder pulses = 2731 -> theta = 1fffh = 1*360 degrees<br>;encoder pulses = 4096 -> theta = 2fffh = 2*360 degrees |

| sach                | theta,2                  |        | ;shift right by 12 for 4.12 format then by 2 to be scaled ;between 0 and 2fffh                                                                                              |

| lacl<br>and<br>sacl | theta<br>#0fffh<br>theta |        | ;filter to get an angle between 0 and 0fffh                                                                                                                                 |

#### **Initialization Vector**

Idr and iqr are the reference values of id and iq. In permanent state, these values correspond to a current generating a constant flux perpendicular to the magnet's flux and produce a constant torque. In the initialization phase, the stator flux is not rotating, theta must be set to place the rotor aligned with phase A. The rotor will be aligned with iq being different from 0, id angle equals -90°.

INITANGLE .set fc00h ;set to -90°

At this point the motor should be able to rotate until it reaches a position aligned with phase A. It is then able to generate some torque if forced to another position. The amplitude of the starting current is fixed in amplitude, the value capable of driving the maximum load torque at open loop. Id and iq are respectively equal to zero and Iqrinit.

Igrinit .set 1000h ;set to nominal current

# **DC Voltage**

The voltage constant is usually found as a motor characteristic Ke in V/rpm

The maximum inverter voltage is equal to VDC 310V

The rated voltage is determined by the BEMF voltage measurement at nominal speed. VDCpu is the variable that sets this magnitude.

VDC is determined as the maximum inverter voltage (ex: 310V) divided by the normalizing factor Vbase, scaled in format 4.12, e.g.,  $VDC = (310/195) *2^{12}$ .

VDC . set 196fh

VDCinvTc is the invert of VDC multiplied by the PWM period PWMPRD, VDCinvTc = (195/310)\*PWMPRD

PWMPRD .set 258h ;equivalent to 60us

VDCinvTc .set 179h

# **Current Sensing and Scaling**

#### **Hardware Interface**

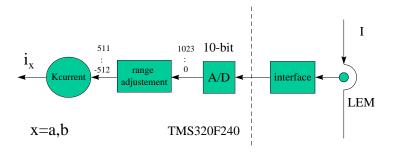

The FOC structure needs as input two-phase currents. In this application, the two currents are sensed by current-voltage transducers (LEM). The current sensor output needs then to be rearranged and scaled so that they can be used by the control software as 4.12 format values. The complete structure of the current obtained is depicted in Figure 15.

Figure 15. Current Measurement Chain

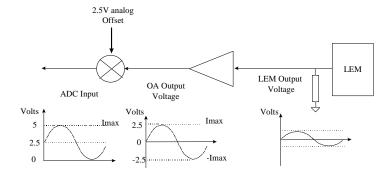

In this application the LEM output signal can be either positive or negative. This signal thus needs to be translated in the range of (0;5V) by the analog interface to allow the single voltage ADC module to read positive and negative values.

$$(-I_{\text{max}}; I_{\text{max}}) \Leftrightarrow (0;5V)$$

The resolution for the current measurements is:

$$resolution = \frac{2I_{\text{max}}}{2^{10}}$$

The integrated DSP A/D converters have a 10 bit resolution. The corresponding voltage step is:  $\frac{5}{2^{10}} = 4.88 \cdot 10^{-3} V$ . Figure 16 shows the different stages of the implemented current sensing:

Figure 16. Current Sensing Interface Block Diagram

Note that  $I_{\text{max}}$  represents the maximum measurable current, which is not necessarily equal to the maximum phase current. The 2.5V analog offset is digitally subtracted from the conversion result, giving thus a signed integer value of the sensed current. The result of this process is represented below:

Figure 17. Sensed Current Values before Scaling

#### **Scaling the Sensed Currents**

Like every other quantity in this application, the sensed phase currents must now be expressed with the p.u. model and then be converted into the 4.12 format. Knowing that the p.u. representation of the current is defined as the ratio between the measured current and the base current and that the maximum current handled by the hardware is represented by 512, the p.u. current representation into the 4.12 format is performed by multiplying the sensed current by the following constant:

$$K_{current} = \frac{4096}{(\frac{512 \cdot I_{base}}{I_{max}})}$$

This constant can be evaluated in one single calculation, not only the p.u. modeling but also the numerical conversion into 4.12 format. When nominal current flows in the motor running at nominal speed the current sensing and scaling block output is 1000h (equivalent to 1pu). You may change the numerical format by simply changing the numerator value. You may adapt this constant to its own current sensing range by simply recalculating  $K_{current}$  with its own  $I_{max}$  value.

Below is given the dedicated code to scale the current stored in ADCFIFO1. For each current measured, one A/D converter input is used. In this way two currents are converted at the same time (the conversion time for one channel is  $6.6 \mu s$ ). In the application, channel 1 for i1 and channel 9 for i2 were selected.

```

* Calculate I<sub>b</sub> from LEM measurement *

ldp #0e0h

NoConv bit ADCTRL1,1000b

bcnd NoConv,TC; wait the EOC

laccADCFIFO1,10

ldp #lb

sach ISR_Temp ;temporary variable

lacl ISR Temp

and #03ffh

sub #512 ;the range is [0fe00;01ffh]

sacIISR_Temp

spm 2 ;PM=10,

It ISR_Temp

mpy Kcurrent ;Kcurrent is defined like .word

pac

sach lb ;lb f 4.12 (1pu=1000h)

spm 0 ;PM=00

```

As an example, we consider an input of 0 to 5V representing a current from -10A to 10A. The register range is then:

| Input<br>Voltage | Related<br>Current |       |                      |

|------------------|--------------------|-------|----------------------|

| 0v               | -10A               | 0000h | 0000 0000 0000 0000b |

| 5v               | +10A               | FFC0h | 1111 1111 1100 0000b |

All the variables in the software are normalized. The currents are set as 1000h, which represents Ibase (4.1Amps). To give better flexibility, the constant Kcurrent is defined with a format 8.8. This does not influence the format of the currents i1 and i2, which remain in format 4.12.

The scaling factor required is:

Kcurrent=(4096\*10)/(512\*4.1)\*28=1383h. In format 8.8

Kcurrent .set 1383h

The next step is to verify that the currents sampled i1 and i2 are equal to 0 after scaling. To see this, emulate the software until you step into the label 'go'. Set a breakpoint after sacl I1, display the memory where I1 is contained or look at the F240 accumulator. If the memory is not exactly 0, it is possible to adjust it directly in the software with the addition of an offset (see comment DC offset in the software).

# **Current Regulation**

The currents *id* and *iq* are controlled with a PI regulator to match their reference values *idr* and *iqr*. The output *upi* from the regulator is limited between *Vmin* and *Vmax*. This is the anti-windup reset. *Xiq*, the PI integral component, is then adjusted from *upi* limitation.

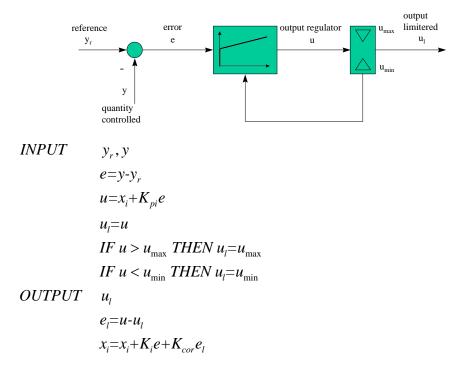

The following figure illustrates the block scheme and the algorithm:

The proportional component is named *Kpi*, the Integral is *Ki* and the PI output limitation error *elpi* is fed back in the *xiq* integral component with a coefficient *Kcor* and the relation *Kcor=Ki/Kpi*.

Below is the PI regulator used to control *iq*. The same scheme is used for *id*.

```

lacc

iqr

;epiq = iqr - iq

sub

sacl

epiq

lacc

xiq,12

;upi = xiq + Kpi*(iqr - iq)

lt

epiq

mpy

#Kpi

apac

;scale in 4.12

sach

upi,4

test if upi is negative

bit

upi,0

bcnd

upimagzeroq,NTC

#Vmin

lacc

sub

upi

neg_satq,GT

bcnd

;if upi<Vmin branch to saturate

lacc

;value of upi is valid

upi

b

limiterq

neg_satq

lacc

#Vmin

; set ACC to neg saturation Vmin

limiterq

upimagzeroq

;upi was positive

#Vmax

lacc

sub

upi

pos_satq,LT

bcnd

;if upi>Vmax branch to saturate

;value of upi is valid

lacc

upi

b limiterq

pos_satq

lacc

#Vmax

;set ACC to pos saturation

;at this point: Vmin < Vqr < Vmax

limiterq

```

```

Var

;Save ACC as reference value

sacl

sub

upi

elpi

;elpi = Vqr - upi

sacl

lt

elpi

#Kcor

mpy

pac

epiq

mpy

#Ki

apac

add

xiq,12

;calculation of the integral coefficient xiq

xiq = Kcor^*(Vqr - upi) + Ki^*(iqr - iq) + xiq

sach

xiq,4

If Kcor is set as Kcor=Ki/Kpi and upi replaced by upi = xiq + Kpi*(iqr - iq), the last

equation

```

$xia = Kcor^*(Var - upi) + Ki^*(iqr - iq) + xiq$

$xiq = Kcor^*(Vqr - xiq) + xiq$

# **Speed Regulation**

becomes

The speed is given by a 1024 point incremental encoder. The two sensor output channels (A and B) are directly wired to the QEP unit of the TMS320F240 DSP Controller . The QEP assigned timer counts the number of pulses, given by the timer counter register (T3CNT). At each sampling period this value is stored in a variable named *encincr*. As the mechanical time constant is much lower than the electrical one, the speed regulation loop frequency might be lower than the current loop frequency. The speed regulation loop frequency is realized in this application using a software counter. This counter increments on PWM interrupts. Its period is the software variable called *SPEEDSTEP*. The counter variable is named *speedstep*. When *speedstep* is equal to SPEEDSTEP, the number of counted pulses is stored in another variable called *speedtmp* and multiplied by KSPEED to get the motor speed. SPEEDSTEP multiplied by the current cycle time determines the speed cycle time

#### **Encoder Constant**

The TMS320F 240 QEP needs two input signals to count the pulses generated by the encoder. They consist of two pulse sequences with variable frequency shifted of a quarter of a period (90 degrees) apart. The QEP circuit counts both edges of these quadrature-encoded input pulses. Therefore, the frequency of the generated clock to the GP timer is four times the one of each input sequence. For example, if the encoder has 1024 pulses per revolution, the edges counted by the QEP circuit are 4096 for one revolution. This constant is indicated with "Encpulses" and the number of pulses is normalized in the range [0; Encpulses].

Encpulses .set 4096

In the case of an encoder with a number of steps not being a power of 2, the process remains the same.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

\*Read Encoder Pulses and Normalize to [0;EncoderPulses] \*

Idp

#0e8h

Iacc

T3CNT

Idp

#ISR\_Temp

sacl

ISR\_Temp

sub

encoderold

encoderold ;... subtract the previous sampling period value to have

;the increment that we'll accumulate in encoder

sacl encincr

add encoder

bcnd encmagzero,GT,EQ ;here we start to normalize encoder value to the

;range [0;Encpulses-1]

add #Encpulses ;the value of encoder could be negative, it depends on

the rotating direction (depends on motor windings to

;PWM Channels connections)

encmagzero

sacl

sub

encoder ;now encoder value is positive but could be

greater than Encoulses-1

#Encpulses ;we subtract Encpulses and we check whether the

;difference is negative. If it is we already have the

;right value in encoder

bcnd encminmax,LT

sacl encoder ;otherwise the value of encoder is greater than

;Encpulses and so we have to store the right value

encminmax ;ok, now encoder contains the right value in the range

lacc tmp ;[0,Encpulses-1]

;the actual value will be the old one during the next

sacl encoderold ;sampling period

#### **Speed Calculation**

The speedtmp variable holds the number of pulses in SPEEDSTEP. The following figure explains all of the steps in the speed calculation.

Kspeed is the constant that multiplies the encoder increment to calculate the real speed named in the assembly software *speed*. In case the encoder detects only one increment during a speed control time, the motor speed in 4.12 format is equal to:

Kspeedpu = (60 / (speed\_cycle\_time\*Encpulses\*speedpu))\*4096

The encoder constant in 8.8 format is equal to:

Kspeed=Kspeedpu\*256

To determine the speed with *speedtmp* as the number of encoder steps during a speed cycle time, the code is:

It speedtmp ;multiply encoder pulses by Kspeed (8.8 format constant)

mpy Kspeed ;to have the value of speed

pac

sfl ;shift by 8 to recover from Kspeed being in 8.8 format

sach speed,7 ;speed is in 4.12 format

As an example, to calculate Kspeed:

Control cycle time = SPEEDSTEP \* PWMPRD = 28\*60 us Encpulses = 4096 incr speedpu = 3000 rpm Kspeed = (60/Encpulses) \* (1/SPEEDSTEP \*PWMPRD) \* (4096/speedpu) \* 2<sup>8</sup> Kspeed = (60/4096) \* (1/(28\*60\*10<sup>-6</sup>)) \* (4096/3000))\*256 = 11.9\*256 Kspeed = 3048 = 0be7h Kspeed .set 0be7h ;14.28 in 8.8 format

#### **Coordinate Transformation**

#### **Generation of Sine and Cosine Values**

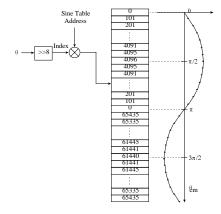

To generate sine and cosine values a sine look-up table and indirect addressing mode by auxiliary register AR5 have been implemented. As a compromise between the position accuracy and the used memory minimization, this table contains  $2^8$ =256 words to represent the  $[0;2\pi]$  range. The above computed position (16 bits integer value) thus needs to be shifted 8 positions to the right. This new position (8 bits integer value) is used as a pointer (named *Index*) to access this table. The output of the table is the  $\sin\theta$  value represented in 4.12 format. Figure 18 shows *theta*, the *Index* and the sine look-up table.

Figure 18.  $Sin\theta$  Calculation Using the Sine Look-Up Table

Note that to have the cosine value, 256/4=40h must be added to the sine *Index*. The assembly code to address the sine look-up table is given below:

```

***********

* sinTheta, cosTheta calculation

*,ar5

mar

theta

lt

mpyu

SR8BIT

pac

Index

sach

Index

lacl

#0ffh

and

add

#sintab

sacl

tmp

ar5,tmp

lar

lacl *

sacl

sine

;sine Theta value, 4.12 format

;The same for Cos ...

lacl

Index

;cos(theta)=sin(theta+90ø)

add

#40h

;90ø = 40h elements of the table

and

#0ffh

add

#sintab

tmp

sacl

lar

ar5,tmp

lacc*

saclcosine

;cosine Theta value, 4.12 format

* END sinTheta, cosTheta calculation

```

# The (a,b,c)-> $(\alpha,\beta)$ Transform (Clarke Transform)

For more details, refer to the TI application report, *Clarke & Park Transforms on the TMS320C2xx*, literature number BPRA048, where the theory is explained. The format used is also 4.12 format.

```

* Clarke transform

* (a,b,c)->(alfa,beta)

* ialfaS=la

* ibetaS=(2*lb+la)/sqrt(3)

lacc

ialfaS

;ialfaS=la

sacl

lacc

lb,1

add

la

sacl

ISR_Temp

;shift 4 places after multiplication

spm

lt

ISR_Temp

#SQRT3inv

mpy

pac

;ibetaS=(2*lb+la)/sqrt(3)

ibetaS

sach

;no shift after multiplication

spm

END Clarke transform *

```

where SQRT3inv is the following constant (.set):

$$SQRT3inv = \frac{1}{\sqrt{3}} = 0.577 \Leftrightarrow 0.93dh$$

#### The $(\alpha,\beta)$ ->(d,q) Transform (Park Transform)

For more details refer to TI application report, *Clarke & Park Transforms on the TMS320C2xx*, literature number BPRA048, where the theory is explained. The format used is also 4.12 format. With the quantity Theta we consider the rotor flux position.

```

*********************************

* Park transform

* (alfa, beta)->(d,q)

* id=ialfaS*cos(theta)+ibetaS*sin(theta)

* ig=-ialfaS*sin(theta)+ibetaS*cos(theta)

spm

ibetaS

lt

sinTheta

mpy

lta

ialfaS

mpy

cosTheta

sinTheta

mpya

idS

; shift 4 places after multiplication

sach

lacc

#0

ibetaS

mpys

cosTheta

apac

sach

iqS

spm

* END Park transform *

```

Inverse matrixes are used to perform the back transformation from currents [id, iq] to [i1, i2, i3].

# **Space Vector Modulation**

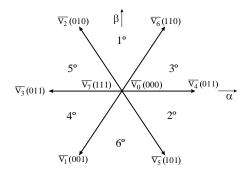

Using a three-leg inverter, eight transistor configurations are possible. These configurations generate eight vectors two of which are 'zero' vectors. The remaining vectors divide the plane into six sectors.

Figure 19. SVPWM, Vectors and Sectors

The first step in generating software PWM is to determine the sector where the reference voltage Vref is located. To do this, Vref is transformed into the stator coordinate system Va, Vb and Vc, and the following criteria is applied:

$$IF \ v_a > 0$$

$THEN \ A:=1$ ,  $ELSE \ A:=0$

$IF \ v_b > 0$   $THEN \ B:=1$ ,  $ELSE \ B:=0$

$IF \ v_c > 0$   $THEN \ C:=1$ ,  $ELSE \ C:=0$

$sec \ tor:= A+2B+4C$

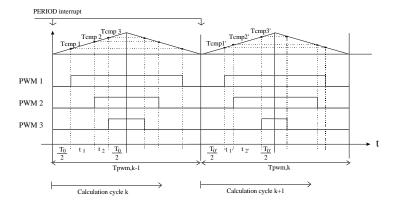

Depending on the sector, two adjacent vectors are chosen. The binary representations of two adjacent basic vectors are different by only one bit, so that only one of the upper transistor switches when the switching pattern switches from one vector to the adjacent one. The two vectors are time weighted by [t1, t2] in a sample period T to produce the desired output voltage<sup>1</sup>.

The PWM pattern retained for the output signal is symmetrical PWM where t1 and t2 are centered. T0, the remaining time, is shared equally on each side of t1 and t2 within a half PWM period as shown in the following graph.

The following equations give the method to determinate the right value for the compare register depending on [t1,t2] and the sector.

The first step is to perform saturation control of t1 and t2:

$$IF (t_1 + t_2) > PWMPRD THEN$$

$$t_{1SAT} = t_1 \frac{PWMPRD}{t_1 + t_2}$$

$$t_{2SAT} = t_2 \frac{PWMPRD}{t_1 + t_2}$$

The second step is to compute the three necessary duty cycles. This is shown below:

$$\begin{cases} t_{aon} = \frac{PWMPRD - t_1 - t_2}{2} \\ t_{bon} = t_{aon} + t_1 \\ t_{con} = t_{bon} + t_2 \end{cases}$$

<sup>&</sup>lt;sup>1</sup> More details about space vectors are given in the application note BPRA073.

The last step is to give the right duty cycle (txon) to the right motor phase (in other words to the correct CMPRx) according to the sector. Figure 20 depicts how this is determined.

Figure 20 Assigning the Right Duty Cycle to the Right Motor Phase

| Sector<br>hase | 1    | 2     | 3    | 4    | 5    | 6    |

|----------------|------|-------|------|------|------|------|

| CMPR1          | tbon | tbaon | taon | tcon | tcon | tbon |

| CMPR2          | taon | tcon  | tbon | tbon | taon | tcon |

| CMPR3          | tcon | tbon  | tcon | taon | tbon | taon |

# Field Weakening

# The Field Weakening

Under certain assumptions it is possible to extend the control speed range beyond the motor's nominal speed. This section explains one possible process to perform this speed range extension.

#### **Field Weakening Principles**

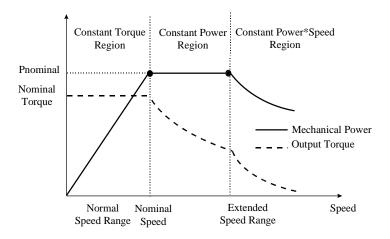

Under nominal load the mechanical power increases as a linear function of speed, up to the nominal power (reached when speed is equal to its nominal value). Knowing that mechanical power is proportional to the torque T times the speed n and that its nominal value has been reached when speed is equal to 3000rpm (nominal value), the torque production must be reduced if the desired speed is to be greater than 3000rpm. This is shown in Figure 21.

Figure 21. Field Weakening Real Operation

Note the three different zones. In the constant power region the nominal torque production behaves like the inverse function of speed, allowing thus constant power production ( $P=T\omega$ ). In the constant Power\*Speed region the nominal torque production behaves as the inverse function of the squared speed.

The maximum torque function is equal to a constant in the first region as V (the phase voltage) increases linearly with speed. Above the nominal speed the phase voltage is maintained constant and equal to its nominal value, thus making the maximum torque an inverse function of the squared speed. This results in the curve shown in Figure 22.

Constant Torque | Constant Power Constant Power\*Speed Region Region Region Maximum Torque Nominal Torque  $\omega$ Extended Normal Nominal Speed Speed Range Speed Speed Range

Figure 22. Maximum and Nominal Torque vs Speed

Note that the nominal torque curve crosses the maximum torque curve. This cross point is the brake point, delimiting the constant power region and the constant power\*speed region. Note also that the nominal torque curve crosses the depicted steady state torque curves in the stability zone (making nominal torque to be smaller than the maximum torque) until the brake point. Once this point has been crossed the nominal torque is forced equal to the maximum torque, thus making the power behave as the inverse function of speed.

These characteristics are only related to the motor capabilities. Good control will enable the full speed, torque and efficiency of the drive to be exploited.

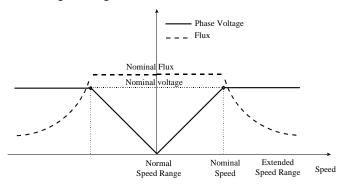

# **Field Weakening Constraints**

The drive constraints for the extended speed range are first the phase voltages and second the phase currents. Knowing that the phase voltage references increase with speed and as their value can not exceed the nominal value, the flux component must then be reduced down to a value that allows the nominal phase voltage to be maintained and the desired speed to be reached.

Knowing that phase currents increase with load, the maximum resistive torque put on the drive during the extended speed range operation must be set to a value that keeps the phase currents not greater than their nominal value. The maximum resistive torque decreases then as a function of speed.

Both the maximum phase voltage and flux references are given for normal and extended speed range in the following scheme (see Figure 23).

Figure 23. Field Weakening Voltage Constraints

Note that both voltage and current constraints must be respected in steady state operation. In fact, during transient operation the phase current might reach several times its nominal value without any risk for the drive. This only assumes that the resulting drive overheating can be dissipated before performing another transient operation.

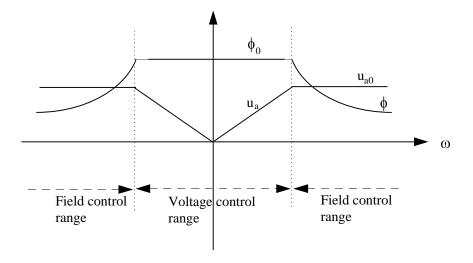

# Field Weakening of the Motor at High Speeds with Closed Loop Scheme

The stator current frequency is increased to achieve high speeds. The stator voltage is directly proportional to the motor flux and the angular speed. In normal condition the motor flux is kept constant. It is then obvious that a maximum stator speed is reached with the limit output voltage of the power converter. To reach a higher speed, the flux is reduced as an inverse of the angular speed to keep the stator voltage constant and equal to its maximum.

Figure 24. Control Range of a PMSM in Steady State

Practically, if we consider the stator current in the d,q rotating reference frame and its relationship with the a,b stationary reference frame, below the speed where the maximum output voltage is reached, the best choice is  $\delta=\pm\pi/2$  and  $i_q=0$ . The effect of the field weakening can be achieved by advancing the current vector beyond  $\delta=\pi/2$ , which means introducing a current component in the negative d-axis. As a consequence,  $i_q$  and then the torque are reduced so as not to exceed the maximum output current  $i_{smax}$ :

$$i_s = \sqrt{i_d^2 + i_q^2} \le i_{s \max}$$

Two schemes are possible to implement the field weakening operation. The simplest is the standard **open loop** control for the d axis current reference. Despite the relative simplicity of this realization, it has the following drawbacks:

- ☐ The reference current equation must be set in the worst-case condition of operation because it corresponds to the lower line voltage and gives a low utilization of the inverter with higher voltages.

- ☐ High-speed reliability: to guarantee the correct operation of control at high speeds, it is necessary to reduce further the voltage capability of the inverter.

- ☐ The reference current equation depends on the motor electrical characteristics, and it is necessary to consider these parameter variations in the determination.

A **closed loop** control avoids these negative effects. It consists of feeding back a proportional integral (PI) regulator with the motor d and q axis voltages applied to the motor and calculating a new reference for the d-current component. This diagram allows us to exploit the full voltage capability of the inverter independently of the line voltage and the motor characteristics. Idr being determined, the new iqr limitation range set by [iqrmin,iqrmax] is then calculated to not exceed i<sub>smax</sub>, as explained before.

# TMS320F240 Field Weakening Implementation

This section describes in detail the field weakening closed-loop control system. All calculations are performed in real time. No look-up table or approximation of steady-state characteristics is used for this implementation.

Figure 25. Field Weakening Function Structure

Vdr and Vgr are used to determine the neutral-phase voltage.

$$Vr = \sqrt{Vdr^2 + Vqr^2}$$

The square root is calculated in real time using the Newton-Raphson method with the recursive equation:

```

X(n) = 0.5 * (X(n-1) + N/X(n-1))

*****************

* Macro

*************

isart .macro

:lacc Vr, X(0)

lacc *+

sfr

;Initial approximate root=N/2

sacl *+

(AR5+1) = X(0)/2

splk #10,* ;(AR5+2) = 10 (iterations for square root)

isqrt?:

X(n) = 0.5 * (X(n-1) + N/X(n-1)):

sbrk #2

lacc *+

rpt #15

subc *

and

#0FFFFh

add

sfr

*+

sacl

lacc

;Repeat until iterations completed:

sub

#1

sacl

bcnd isqrt?,NEQ

;Restore AR5 & put result in acclow:

mar

lacc

mar

.endm

```

Vr and the reference value Vbase are controlled with a PI regulator to generate the output idr. In the field weakening region, |idr| increases. In order not to go over the nominal stator current ismax, iqmax is decreased with the relation:

$$iq \max = \sqrt{is \max^2 - idr^2}$$

The new iqmax calculated serves as limitation for iqr, the result of the speed controller. As iqr is directly proportional to the motor torque, modifying iqmax also changes the torque available on the motor.

### Results

# **Software Implementation**

The proposed control scheme has been implemented on the TMS320F240 EVM. All of the control routines are implemented using assembler language with fixed-precision numerical representation.

The calculation time of the whole control algorithm is described below:

|                                        | PWM (us) | Control (us) | MIPS |

|----------------------------------------|----------|--------------|------|

| FOC                                    | 60       | 32,6         | 10,9 |

| FOC+speed control                      | 60       | 35           | 11,7 |

| FOC+field weakening FOC+speed control+ | 60       | 35,6         | 11,9 |

| field weakening                        | 60       | 38           | 12,7 |

The inverter switching frequency is 16.6 kHz. The timing of the control algorithm is shown in Figure 4. The control algorithm is run by an interrupt (PERIOD interrupt) generated by the event manager PWM unit to synchronize the control and the PWM generating ramp. The speed reference and the main parameters of the control scheme can be changed in real time by means of a host PC linked to the evaluation board via a RS232 link.

# **Experimental Results**

This section handles the results of the different drive operations. The motor has been mounted on a test bench with adjustable resistive torque.

At power up, a constant flux is imposed to the drive so that the shaft aligns to a position that is defined as zero angle (index mark). This initialization phase is performed so that a non-absolute encoder may be used as position sensor. This phase does not take into account the direction of shaft at start up. The current amplitude during the initialization phase is the nominal current so that the shaft can be aligned even at nominal torque.

#### **Results until Nominal Speed**

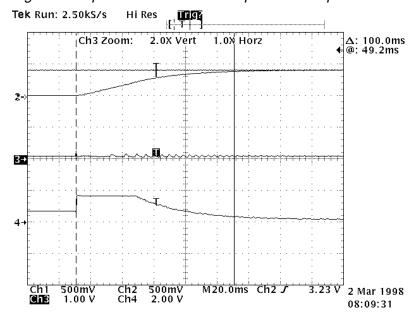

Figure 26. Speed Transient from 0 rpm to 1000 rpm

This speed transient picture is given with no torque. The values observed on the oscilloscope are directly derived from control variables through four digital-to-analog converters included in the F240 EVM.

- □ plot1: n\_ref the reference speed

- plot2: n the sensed speed

- □ plot3: id the magnetizing current

- □ plot4: iq the current proportional to the torque

The scaling factor for the variables are 1.25 volts for 1 pu (1000h). In this case:

- ☐ 415mV is equivalent to 1000rpm.

- ☐ 1.56V is equivalent to 5.12Amps, the maximum current.

The first part of the plot illustrates the PI behavior in steady-state at initialization phase. Id is maintained to 0 and iq to Iqrinit = 1.5Amps, the starting phase current.

After the speed reference step, iq is set to its maximum value for a better dynamic response, then goes back to its steady-state value related to the low torque implied.

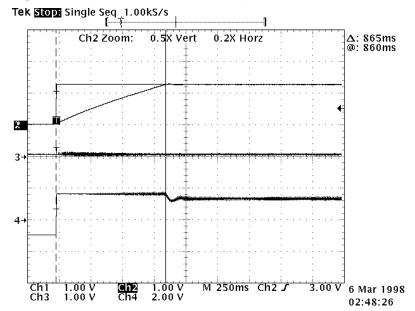

Figure 27. Speed Transient from 0 rpm to 3000 rpm at Nominal Torque

This plot is a speed transient from zero speed to nominal speed (3000rpm) at nominal torque (2.2Nm). Id is always kept at zero, iq during transient reaches the maximum current which is 25% higher (5.12Amps) than the nominal current (4.1Amps). In steady state iq is equal to its nominal current as the conditions are nominal power.

Figure 28. Speed Transient from -1000 rpm to 1000 rpm at Nominal Torque

The speed transient from -1000rpm to 1000rpm is done in two phases. The first step from -1000rpm to zero speed is helped by the resistive torque and the acceleration phase from 0 to 1000rpm. All the transient times can be increased by increasing the maximum iq value to more than 25% of the base value.

#### **Field-Weakening Operation**

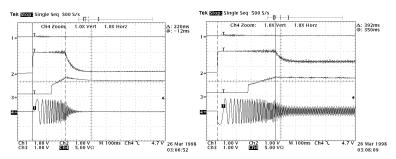

Figure 29. Speed Transient from 0 rpm to 3000 rpm Graph1 without Torque, Graph2 with 1.1Nm

Plot1 is id. It remains constant even during transients, as the voltage Vr (plot3) does not exceed its maximum value equal to Vbase, the BEMF at nominal speed.

Iq (plot2) increases to its maximum value iqrmax and goes back to a value related to the torque imposed when the speed reference is reached.

The break observed in Vr comes from the fact that this variable is only calculated for voltage above Vbase/2.

The last plot is the phase current. It illustrates the control performance never losing the motor position.

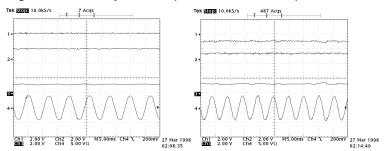

Figure 30. Steady-State Speed at Nominal Speed and 33% Above at Maximal Torque

The first graph is done at nominal conditions 3000rpm and 2.2Nm. Id is equal to zero and iq to its maximum value iqrmax. Vr is equal to Vbase.

The second graph is done at 4000rpm with 1.3Nm. Id is controlled negative. 2.2Nm can't be achieved, as iqr is limited to iqrmax, which is updated so that the stator current

$i_s = \sqrt{i_d^2 + i_q^2}$  remains constant and equal to its maximum ismax during field weakening operation.

Figure 31. Speed/Torque Plot

The maximum speed reached is 60% above the nominal speed. The table below gives the results in term of torque and efficiency achieved depending on the speed.

| Speed (rpm) | Torque (Nm) | Efficiency (%) | Power (W) |

|-------------|-------------|----------------|-----------|

| 1000        | 2,21        | 74             | 690       |

| 2000        | 2,21        | 82             | 690       |

| 3000        | 2,21        | 85             | 690       |

| 3500        | 1,91        | 85             | 690       |

| 3650        | 1,81        | 85             | 690       |

| 4000        | 1,31        | 80             | 540       |

| 4500        | 1,04        | 78             | 490       |

| 5000        | 0           | 0              | 0         |

#### **User Interface**

The user interface is implemented to help the programmer while optimizing some of the control parameters. It allows changing the speed, or selection of any of the control variables to be visualized through any of the four DAC outputs, to run and stop the motor or to change in real-time the PI parameters. Many other options may be implemented. The main program is written in Qbasic. Below is the appearance of the User screen:

Figure 32. User Screen

The Qbasic code is given in the appendix. Another part is needed to perform the data exchange from the DSP serial communication interface to the PC. The code is found at the end of the assembly code.

#### Conclusion

This document presented a field orientated control scheme for a three-phase permanent magnet drive based on the Texas Instruments TMS320F240 DSP Controller. It has been shown how the real-time processing capabilities of this DSP controller can lead to a highly reliable and effective drive. Not only is drive reliability and efficiency improved, but so is the motor and drive cost effectiveness.

This document also described the speed variation capability, direct torque and flux control, and excellent dynamic behavior. This level of performance has been reached by utilizing only 10.6 MIPS from the 20 MIPS available with the code size not exceeding 1.1Kword of program memory with 300 words of data memory.

### References

Texas Instruments, *Field Orientated Control of Three-Phase AC-Motors*, Literature number: BPRA073, December 1997.

Texas Instruments, *DSP Solution for Permanent Magnet Asynchronous Motor*, Literature number: BPRA044, Nov. 1996.

Werner Leonard, *Control of Electrical Drives*, 2nd Completely Revised and Enlarged Edition, Springer, ISBN 3-540-59380-2.

Texas Instruments, *Current Measurement Using a Single Shunt Resistor*, Literature number: BPRA077, December 1997.

T.J.E. Miller, *Brushless Permanent-Magnet and Reluctance Motor Drives*, Oxford Science Publications, ISBN 0-19-859369-4.

Texas Instruments, *Implementation of a Speed Controlled Brushless DC Drive Using TMS320F240*, Literature number BPRA064, July 1997,

Texas Instruments, *Clarke & Park Transforms on the TMS320C2xx*, literature number BPRA048, June 1998,

## Appendix A. TMS320F240 FOC Software

```

TEXAS INSTRUMENTS

Field Orientated Control for PMSM

with field weakening

File Name: focmck7.asm

Originator: Michel Platnic

Description: The software includes

-PMSM field oriented control

-2 phase current measurement

-PDPINT routine for fault

-Current closed-loop initialization phase

-Vr BEMF real-time calculation

-iqr real-time limit calculation / idr

-idr PI calculation

-User Interface

Function list: -c_int0

Target:

TMS320F240, MCK240

Code can be Flashed

ACPM750E Power board

Digiplan Motor MD3450

status:

Working

History: Completed on 26 March 98

.include ".\c240app.h"

.mmregs

******************

.globl _c_int0 ;set _c_int0 as global symbol

.sect "vectors"

b _c_int0 :reset interrupt handler

b _c_int1 :RTI.SPI.SCI.Xint interrupt handler

_c_int1

```

```

_c_int2 ;PWM interrupt handler _c_int3 ;

b _c_int3;

b _c_int4;

b _c_int5;

b _c_int6;

_c_int3

_c_int4

_c_int5

_c_int6

_c_int6 ;capture/ encoder Interrupts

.space 16*6 ;reserve 6 words in interrupt table

*******************

* Auxiliary Register used

* ar4 pointer for context save stack

* ar5 \stackrel{-}{\text{used}} in the interruption c_int2 for control calculation

for main program

.usect "blockb2",15 ;space for Status Register context save in Page 0

.usect "blockb2",5 ;space for dac values in Page 0

dac_val

*** Motor Digiplan ***

*** Numeric formats: all 4.12 fixed point format twos complement for negative values

*** (4 integer & sign + 12 fractional) except otherwise specified

* - Nominal current 4.1 Amps max= 2.2/0.76 *sqrt(2) (max value)

* - Nominal Torque 2.2 Nm

* - Rated Power 1150W

* - Currents: 1000h (4.12) = 4.1 A = Ibase (max value)

* - Voltages: 1000h (4.12) = 325 V = Vbase (max value) phase-neutral

* - Angles : [0;ffffh] = [0;360] degrees

* - Speed : [0;1000h] (4.12) = [0;3000] rpm

*** END Numeric formats

*****************

Look-up tables .includes

* N.B. all tables include 256 elements

*****************

.usect "table", 256 ; space to copy sine table in RAM

sintab

.sect "table_f"

;sine table in ROM

sine.tab

sintab_flash

.include

; sine wave look-up table for sine and cosine waves generation

; generated by the BASIC program "SINTAB.BAS"

;4.12 format

*** END look-up tables .includes

* Variables and constants initializations

* To program the flash array all variable are set to bss

* A 'V' is added in front of the variable initialized later

******************

.data

*** current sampling constants

VKcurrent .set 00b38h ;8.8 format (*11.22) sampled currents normalization

constant

;ADCIN6 (il current sampling)

;ADCIN14 (i2 current sampling)

i+/- 5.75 Amps for Ibase = 4.1 Amps

*** axis transformation constants

VSQRT3inv .set 093dh ;1/SQRT(3) 4.12 format

0ddbh ; SQRT(3)/2 4.12 format

VSQRT32

.set

*** PWM modulation constants

PWMPRD .set 258h

;PWM Period=2*600 -> Tc=2*600*50ns=60us

;(50ns resolution)

.set 0 ;minimum PWM duty cycle

.set PWMPRD-2*Tonmax ;maximum utilization of the

Tonmax

MAXDUTY

*** PI current regulators parameters

VKi

.set 07Ah ;4.12 format = 0.03

```

```

VKpi

999h

;4.12 format = 0.60 (include period)

.set

.set Occh

;4.12 \text{ format} = 0.05

VKcor

;Kcor = Ki/Kpi

*** PI speed regulators parameters

VKispeed .set 7ah ;4.12 format = 0.03

06800h ;4.12 format = 6.5

VKpispeed

.set

;4.12 \text{ format} = 0.0046

VKcorspeed

.set

12h

*** PI field-weakening regulators parameters

.set

07Ah ; 4.12 format = 0.03

;4.12 format = 0.60 (include period)

999h

VKpiweak

.set

VKcorweak

.set

0cch ;4.12 \text{ format} = 0.05

*** Vqr and Vdr limitations

01000h ;BEMF at base speed

.set

.set

0ec00h ; 4.12 format = -1.25 pu

Vmin

01400h ;4.12 format = 1.25 pu

Vmax

.set

*** Is and Idr limitations

.set 0bb5h

Vismax

;4.12 format = 3Amps Limitation for

;ACPM750E

Idrmin

Of44bh ;4.12 format = -3Amps limit. for ACPM750E

.set

.set 00000h ;4.12 format = 0A (1000h = Ibase)

Idrmax

*** Initialization phase Iqr

Iqrinit

.set

009clh ;4.12 format = 2.5A (1000h = Ibase)

*** Encoder variables and constants

VKencoder

0c000h ; this constant is needed only with

.set

encoder !

;it is used to convert encoder pulses [0;4095] to an

electric angle [0;360]=[0000h;1000h]

;2.14 format unsigned = 3.0 (see "Theta calculation" block

for details)

Encpulses

.set 4096 ; this constant is needed only with encoder!

;number of encoder pulses per round (mechanical)

*** Speed and estimated speed calculation constants

.set 1000h ;Base speed

Nbase

Kspeed

Obe7h ; this constant is needed only with encoder !

;it is used to convert encoder pulses to a speed value.

;8.8 format = 11.9 (see manual for details about this constant

calculation)

;base speed 3000rpm, PWMPR 258h

SPEEDSTEP

.set 28

;speed samplig period = current sampling period * 10

*** Speed and estimated speed calculation constants

;temporary variable (to use in ISR only !!!)

.bss

tmp,1

.bss

option,1

; virtual menu option number

.bss

daout,1

; address of the variable to send to the DACs

.bss

daouttmp,1

; value to send to the DACs

*** DAC displaying table starts here

.bss i1,1 ;phase current i1

;phase current i2

.bss

i2,1

;phase current i3

;Phase 1 voltage

.bss

i3,1

.bss

Ua,1

Ub,1

;Phase 2 voltage

.bss

.bss

Uc,1

;Phase 3 voltage

seno1,1

;generated sine wave value

.bss

t1,1

;SVPWM T1 (see SV PWM references for details)

.bss

;SVPWM T2 (see SV PWM references for details)

.bss

t2,1

.bss

coseno,1

;generated cosine wave value

;Phase 1 voltage for sector calculation

.bss

Va,1

Vb,1

.bss

; Phase 2 voltage for sector calculation

.bss

Vc,1

;Phase 3 voltage for sector calculation

vDC,1

;DC Bus Voltage

.bss

taon,1

;PWM commutation instant phase 1

.bss

.bss

tbon,1

;PWM commutation instant phase 2

```

```

.bss

tcon,1

;PWM commutation instant phase 3

.bss

theta,1

;rotor electrical position in the range [0;1000h]

;4.12 format = [0;360] degrees

.bss

ialfa.1

;alfa-axis current

.bss

ibeta,1

;beta-axis current

.bss

Valfar,1

;alfa-axis reference voltage

;beta-axis reference voltage

.bss

Vbetar,1

idr,1

;d-axis reference current

.bss

.bss

iqr,1

;q-axis reference current

id,1

;d-axis current

.bss

;q-axis current

.bss

iq,1

.bss

Vdr,1

:d-axis reference voltage

.bss

Vgr,1

;q-axis reference voltage

epiq,1

;q-axis current regulator error

.bss

;d-axis current regulator error

.bss

epid,1

;q-axis current regulator integral component

.bss

xiq,1

xid,1

.bss

;d-axis current regulator integral component

.bss

n,1

;speed

.bss

n_ref,1

;speed reference

epispeed,1

.bss

;speed error (used in speed regulator)

xispeed,1

.bss

; speed regulator integral component

;SVPWM variable

.bss

X,1

;SVPWM variable

.bss

Y,1

Z,1

;SVPWM variable

.bss

sectordisp,1

;SVPWM sector for display

.bss

.bss

initphase,1 ;flag for initialization phase

.bss

encoder,1

.bss

Vr,1

;Phase max voltage

.bss

iqrmin,1

;iqr min limitation

iqrmax,1

.bss

;igr max limitation

*** END DAC displaying table

sector,1 ;SVPWM sector

serialtmp,1 ;serial communication temporary variable

.bss

.bss

dal,1 ;DAC displaying table offset for DAC2

;DAC displaying table offset for DAC3

.bss

.bss

da3,1 ;DAC displaying table offset for DAC3

da4,1 ;DAC displaying table offset for DAC4

vDCinvTc,1 ;VDCinv*(Tc/2) (used in SVPWM)

epvr,1 ;PI error for field weakening

xvr 1 ;PI integral term for field weakening

.bss

.bss

.bss

.bss

xvr,1 ;PI integral term for field weakening indice1,1 ;pointer used to access sine look-up table

.bss

.bss

.bss

upi,1

;PI regulators (current and speed) output

.bss

elpi,1

;PI regulators (current and speed) limitation error

.bss

faultreset,1

;Used to re-enable the hardware protection

tmp1,1

;tmp word

. bss

accb,2

;2 words buffer

.bss

acc_tmp,2

;2 words to allow swapping of ACC

.bss

.bss

encoderold,1

; encoder pulses value stored in the previous sampling

;period

.bss

encincr,1

; encoder pulses increment between two consecutive

;sampling periods

speedtmp,1

; used to accumulate encoder pulses increments (to

.bss

; calculate the speed each speed sampling period)

.bss

speedstep,1

; sampling periods down counter used to define speed

; sampling period

.bss

Kcurrent,1

;Cf explanation given above

;Cf explanation given above

.bss

SQRT3inv,1

;Cf explanation given above

bss

SORT32,1

;Cf explanation given above

.bss

Cf explanation given above

.bss

Kpi,1

.bss

Kcor,1

;Cf explanation given above

Kpispeed,1 ;Cf explanation given above Kcorspeed,1 ;Cf explanation given above Kiweak,1 ;Cf explanation given above

;Cf explanation given above

.bss

.bss

.bss

.bss

Kpiweak,1

;Cf explanation given above

.bss

;Cf explanation given above

.bss

Kcorweak.1

```

```

.bss

;Cf explanation given above

;Cf explanation given above

.bss

Kencoder,1

*** END Variables and constants initializations

; link in "text section

.text

**************

* Macro

* Inputs: argument in *AR5 !MUST BE POSITIVE!

* Outputs:result in ACClow

* Notes: this function uses the Newton-Raphson method:

X(n) = 0.5 * (X(n-1) + N/X(n-1))

* this function uses *(AR5+1) & *(AR5+2) locations!

isqrt .macro

clrc sxm

lacc

;lacc Vr, X(0)

sfr

;Initial approximate root = N/2

sacl

;(AR5+1) = X(0)/2

#10,*

splk

;(AR5+2) = 10 (iterations for square root)

isqrt?:

X(n) = 0.5 * (X(n-1) + N/X(n-1)):

#2

sbrk

lacc

*+

rpt

#15

subc

#0FFFFh

and

add

sfr

sacl

*+

;Repeat until iterations completed:

lacc

sub

#1

sacl

isqrt?,NEQ

bcnd

;Restore AR5 & put result in acclow:

mar

lacc

mar

setc sxm

.endm

****************

* _c_int2 Interrupt Service Routine

\mbox{*} synchronization of the control algorithm with the PWM

* underflow interrupt

_c_int2:

*******

* Context Saving

******

ar4

;context save

mar

#1,*-

;status register 1

;status register 0

sst

#0,*-

sst

* _

* _

sach

;Accu. low saved for context save

;Accu. high saved

sacl

* END Context Saving *

*,ar5

;used later for DACs output

mar

ldp

#DP_EV

lacc

IVRA

ldp

#tmp

sacl

tmp

#20H

sub

bcnd

PDPRoutine, EQ

sub

#9

```

```

bcnd

ControlRoutine, EQ

ContextRestoreReturn

b

* END Int2 Interrupt Service Routine *

ContextRestoreReturn

**********

* Context restore and Return

**********

larp ar4

mar

*+

lacl

*+

;Accu. restored for context restore

*+,16

add

#0,*+

lst

#1,*+

lst

clrc

INTM

ret

* END Context Restore and Return *

PDPRoutine

ldp

#IFRA>>7

#001h, IFRA ; Clear all flags, may be change

splk

; with only T1 underflow int.

ldp

#DP_EV

#0fffh,ACTR

splk

splk

#0207h,COMCON ;FIRST enable PWM operation

splk

#8207h, COMCON ; THEN enable Compare operation

ldp

#DP_PF2

#0FF00h,PBDATDIR;IOPB 1 conf. as output, set to logic 0

splk

;to re-enable protection circuitry

;after a fault on ACPM750E

; wait minimum 2us (needed by circuitry)

#200

rpt

nop

;here 10us

#0FF02h,PBDATDIR;IOPB 1 conf. as output, set to logic 1

splk

b

ContextRestoreReturn

* END PDPRoutine

ControlRoutine

*****************

* Current sampling - AD conversions

* N.B. we will have to take only 10 bit (LSB)

*****************

ldp

#DP_PF2

\#0\text{FF}08h, PCDATDIR; bit IOPC7 set to 0 for test purposes

splk

ldp

#DP PF1

#186Dh,ADC_CNTL1;i2 and i3 conversion start

splk

;ADCIN6 selected for i2 A/D1 110

;ADCIN14 selected for i3 A/D2 110 \,

;01101101

*** current sampling

conversion

bit.

ADC_CNTL1,8

bcnd

conversion,tc ; wait approximatly 6.6us

lacc

ADC_FIFO1,10

ldp

#i2

sach

i2

ldp

#DP_PF1

ADC_FIFO2,10

lacc

ldp

#i3

sach

i3

*** fault enable and test EVM LED On/Off

lacc

faultreset

bcnd

initcontrol, EQ

#DP_EV

ldp

#0999h,ACTR

splk

#faultreset

ldp

#0,faultreset

splk

```

```

*** Initialization phase

initcontrol

lacl

initphase

; are we in initialization phase ?

bcnd

noinit1,NEQ

setc

xf

;if yes, set theta = 0fc00h 4.12 format = -90 degrees

lacc

#0fc00h

;(align rotor with phase 1 flux)

sacl

theta

#Iqrinit

;q-axis reference current = initialization q-axis

lacc

;reference current

sacl

iqr

lacc

#0

;zero some variables and flags

sacl

idr

encoder

sacl

sacl

encoderold

sacl

speedtmp

sacl

lacc

#SPEEDSTEP

;restore speedstep to the value SPEEDSTEP for next speed

;control loop

sacl

speedstep

ldp

#DP EV

#1,T3CNT

splk

;zero Incremental Encoder value if initialization step

ldp

#initphase

;there is no need to do position and speed calculation

b

go

; in initialization phase (the rotor is locked)

*** End Initialization phase

noinit1

*** Encoder pulses reading

clrc

xf

#DP EV

ldp

lacc

T3CNT

;we read the encoder pulses and ...

;encoder plug in the opposite direction for ACPM

neg

ldp

#i1

sacl

tmp

encoderold

; subtract the previous sampling period value to have

sub

;the increment that we'll accumulate in encoder

sacl

encincr

add

encoder

encmagzero,GT,EQ;here we start to normalize encoder value to the

band

;range [0;Encpulses-1]

add

; the value of encoder could be negative, it depends on

#Encpulses

;the rotating direction (depends on motor windings to

; PWM Channels connections)

encmagzero

; now encoder value is positive but could be

sacl

encoder

;greater than Encoulses-1

sub

#Encpulses

; we subtract Encpulses and we check whether the

;difference is negative. If it is we already have the

;right value in encoder

bcnd

encminmax,LT

sacl

encoder

;otherwise the value of encoder is greater than

; Encpulses and so we have to store the right value

encminmax

; ok, now encoder contains the right value in the range

lacc

;[0,Encpulses-1]

;the actual value will be the old one during the next

sacl

encoderold

;sampling period

*** END Encoder pulses reading

******

* Theta calculation

******

encoder

; multiply encoder pulses by Kencoder (4.12 format

; constant) to have the rotor electrical position

Kencoder

mpyu

;encoder pulses = 1600 -> theta = 1fffh = 1*360 degrees

pac

;encoder pulses = 3200 -> theta = 2fffh = 2*360 degrees

sach

theta.2

```

```

lacl

theta

#0fffh

and

theta

sacl

*** END theta calculation

*************

* Calculate speed and update reference speed variables

**************

lacc speedstep ;are we in speed control loop ? (SPEEDSTEP times current

;control loop)

#1

sub

sacl

speedstep

bcnd

;if we aren't, skip speed calculation

nocalc,GT

*** Speed calculation from encoder pulses

speedtmp ;multiply encoder pulses by Kspeed (8.8 format constant)

; to have the value of speed

#Kspeed

mpy

pac

rpt

sfr

sacl

lacc

#0

;zero speedtmp for next calculation

speedtmp

sacl

lacc

sacl

*** END Speed calculation from encoder pulses

***************

* Speed regulator with integral component correction

lacc n_ref

sub

sacl

epispeed

lacc

xispeed,12

lt

epispeed

mpy

Kpispeed

apac

sach

upi,4

;here start to saturate

upi,0

bit.

upimagzeros, NTC ; If value +ve branch

bcnd

lacc

iqrmin

sub

upi

neg_sat,GT