SCHS011 - D3512, JUNE 1990 - REVISED MARCH 1992

- Upgrade of the SN74ACT2160

- 2-Way Architecture Significantly Improves Hit Rate

- Implements LRU Replacement Algorithm

- Useful for Bus Watching

- On-Chip Parity Generator and Checker

- Easily Expandable in Depth and Width

- Open-Drain Look-Ahead Circuitry on Match Outputs

- Self-Timed Write Circuitry

- Fully TTL Compatible

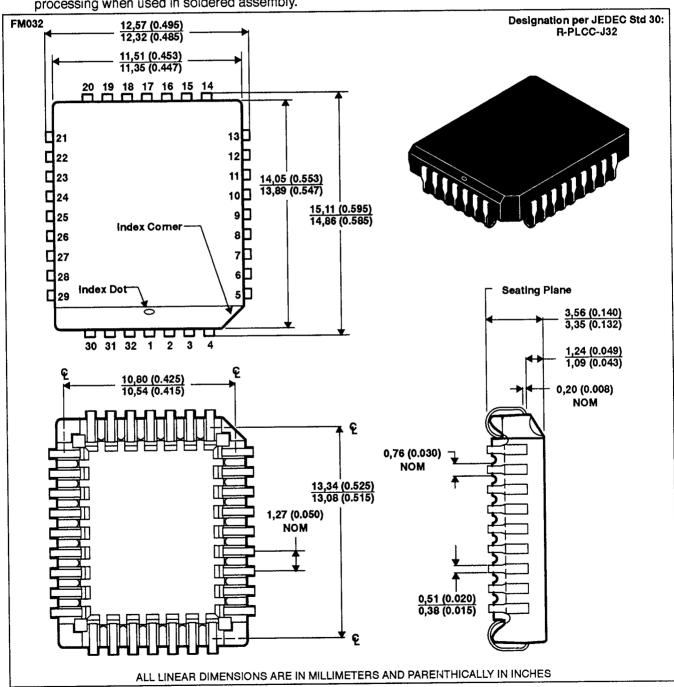

#### **FM PACKAGE** (TOP VIEW) 5 4 5 5 5 5 5 6 6 2 32 31 30 29**∏** D1 A6 0 28**∏** D2 Α7 **]** 6 27 D3 7 **8**A Α9 Пв 26 □ Vcc 25 MATCH1 **GND** MATCH2 RESET 24 10 23 GND LRU-W 11 **[**] 12 22 ∏ PF R 21 BANK **₩R П** 13 14 15 16 17 18 19 BSEL A10

#### description

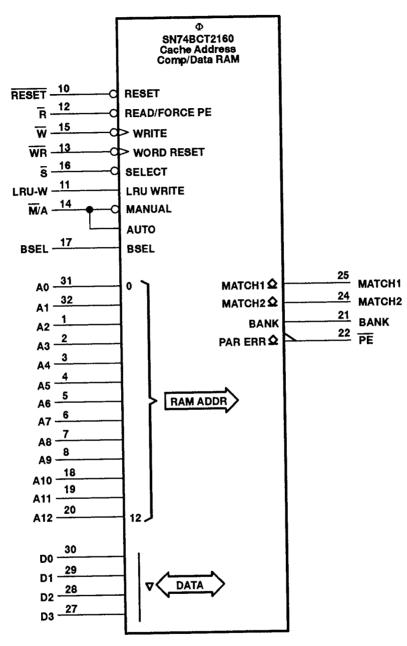

The SN74BCT2160 is a valuable building block for implementing fast two-way set associative caches. This device consists of two separate 8K×5 RAMs for tag and parity storage, an 8K x 1 LRU RAM, two high-speed comparators, and the control circuitry necessary to give the designer the freedom to determine how this device will be used. The SN74BCT2160 also includes single-entry invalidation circuitry and parity generation and checking for ease of design and high system reliability.

The SN74BCT2160 is fabricated using advanced BiCMOS technology for high speed and simple interface with bipolar TTL circuits. By combining the SN74BCT2160 with programmable logic, a cache can be constructed that specifically addresses the individual system requirements. Significant reductions in cache memory component count, board area, and power dissipation can be achieved by using this device.

## direct-mapped versus two-way set associative caches

A cache memory is a small high-speed memory that is used to store a portion of the data found in the larger main memory to achieve optimum processor performance and to reduce main memory bus traffic. Since the cache memory is smaller than the main memory, only part of the address, the least significant bits referred to as the index, is used to address the cache memory. The most significant address bits, called the tag, are stored along with the cache data and are used to identify what data is stored in an indexed location. When the processor requests data, the index portion of the processor address points to a word of data in the cache-data RAM and to a tag in the cache tag RAM. If the upper portion of the processor address is equal to the stored tag, a cache hit is said to occur and the cached data can be immediately sent to the processor.

In a direct-mapped or one-way set associative cache, only one data word and tag exist in cache for each index. This means that when the processor requests data, only one cache memory location can contain the requested data. Also, if the requested data is not in the cache and the cache is updated, the data in the indexed cache memory location will be written over regardless of how recently it has been used.

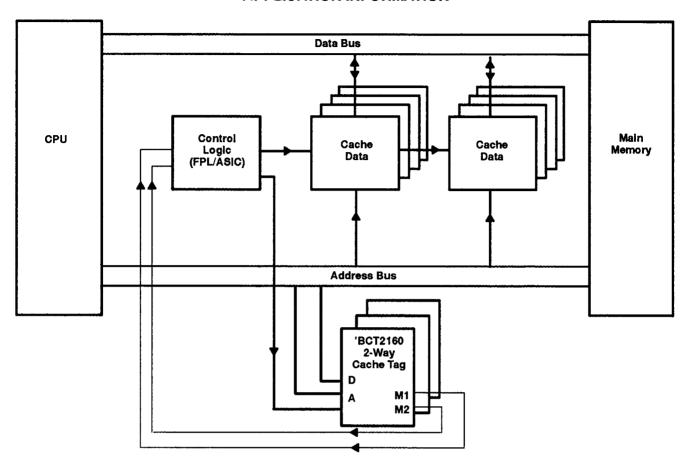

In a two-way set associative cache, two data words and tags exist for each index. This means that the requested data can reside in one of two cache locations. When a miss occurs and the cache is updated, the least recently used data can be written over. As would be expected, studies have shown that the hit rate improves significantly when using a two-way cache design over a one-way or direct-mapped cache design. Through use of the 'BCT2160, the logic complexity and parts count usually associated with a two-way cache are greatly reduced.

This device is covered by U.S. Patents 4,831,625; 4,837,743; 4,858,182; 4,860,262; 4,884,270; and additional patents pending.

1

#### **SN74BCT2160**

## $8K \times 4$ 2-WAY CACHE ADDRESS COMPARATOR/TAG RAM

SCHS011 - D3512, JUNE 1990 - REVISED MARCH 1992

#### address comparison

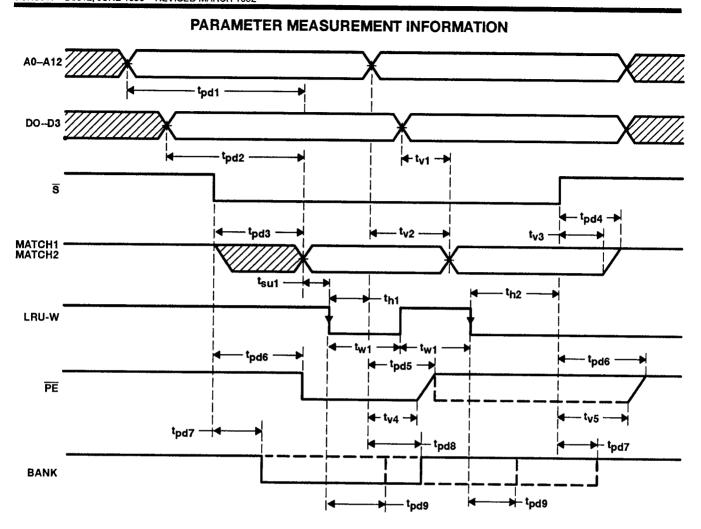

The 'BCT2160 compares the contents of the memory location addressed by A0–A12 with the address bits (or tag) applied at D0–D3. An equality is indicated by a high level on the MATCH1 or MATCH2 outputs. MATCH1 is high when the applied tag is equal to the stored tag in bank 1. MATCH2 is high when the applied tag is equal to the stored tag in bank 2.

#### writing to the 'BCT2160

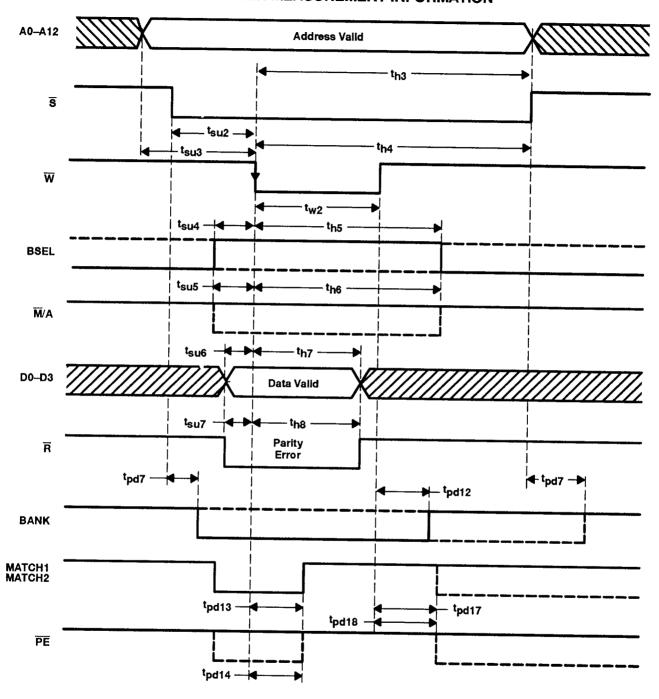

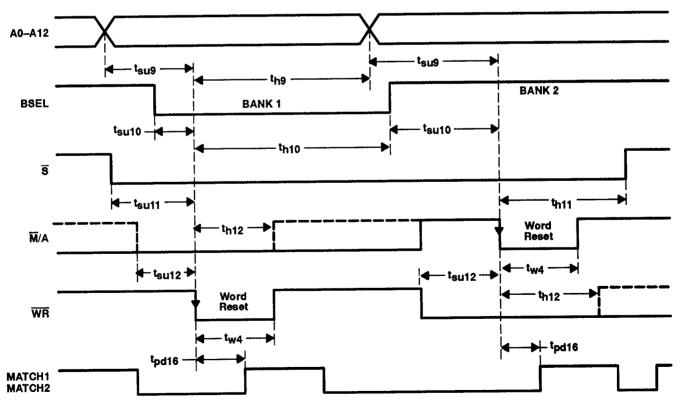

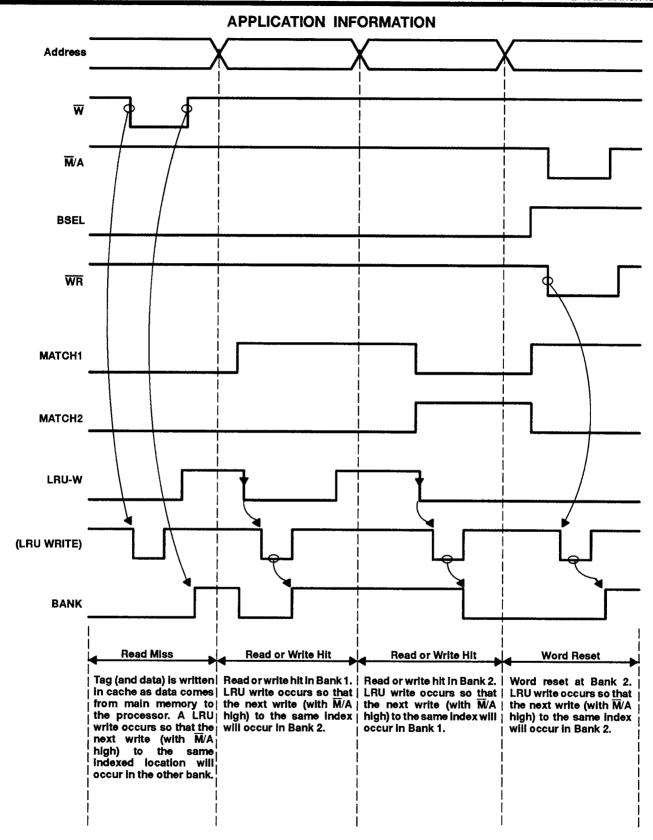

The 'BCT2160 has been designed with self-timed write circuitry. A high-to-low transition at the  $\overline{W}$  input initiates an internally generated write pulse. After a high-to-low transistion at  $\overline{W}$ ,  $\overline{W}$  may be held low without initiating additional write pulses. The manual/auto ( $\overline{M}/A$ ) input on the 'BCT2160 provides two methods of selecting which tag bank will be written to when the write input ( $\overline{W}$ ) is taken low. When  $\overline{M}/A$  is low, the bank select input (BSEL) selects the bank to be written to. BSEL low selects bank 1 and BSEL high selects bank 2. When  $\overline{M}/A$  is high, the least recently used (LRU) circuitry automatically selects the bank written to when  $\overline{W}$  is taken low. The BANK output is latched when  $\overline{W}$  goes low. This latch will return transparent when  $\overline{W}$  returns high. When  $\overline{W}$  is low, the D0–D3 outputs are disabled. A high-to-low transition at the  $\overline{S}$  input when  $\overline{W}$  is low will not initiate a write (self-timed) pulse.

#### writing to the cache data RAMs

When a read or a write miss occurs and the cache is updated, the BANK output indicates to which bank the data should be written (BANK is the output of the internal 8K x 1 LRU RAM). If BANK is low, bank 1 should be written, if BANK is high, bank 2 should be written. When writing a tag with  $\overline{M}/A$  low, the BANK output does not indicate which bank is being selected by the BSEL input. When a write hit occurs, the match outputs indicate to which bank the data should be written.

#### LRU replacement circuitry

A concept commonly referred to in cache design is the property of locality. An aspect of the property of locality says that the information currently in use is likely to be used again soon. Based on this property, it is desirable to replace the information that has not been used recently when writing to cache. With a set size of two, this is easily done using one bit to indicate which of the two addressed locations is oldest or least recently used. The 'BCT2160 contains an 8K×1 RAM and the necessary circuitry to implement the LRU replacement algorithm.

The  $\overline{M}/A$  input allows the user to choose between automatic LRU and manual replacement. When  $\overline{M}/A$  is high, the LRU RAM output selects which bank to write to. When the LRU bit for a given address is low, a write pulse will write D0–D3 to bank 1. When the LRU bit for a given address is high, a write pulse will write D0–D3 to bank 2. The LRU RAM is updated every time a write, a match (with LRU-W signal), or a word reset occurs.

When a write occurs with  $\overline{M}/A$  high, the addressed LRU bit is inverted and written back in so that the next write with  $\overline{M}/A$  high to that address will be to the other bank. When a write occurs with  $\overline{M}/A$  low, the bank is selected by the BSEL input and the addressed LRU bit is adjusted so that the next write to the same address with  $\overline{M}/A$  high will be to the other bank.

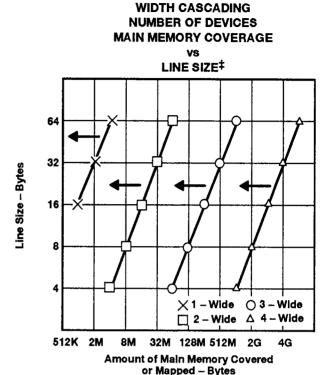

With a match output high indicating a match, the LRU RAM will also be updated when the LRU-W input is taken low. The logic level at each match output is fed back internally to the LRU circuitry. If MATCH1 or MATCH2 are high, the LRU-W input provides an LRU write timing signal that causes an internal LRU write pulse to be generated. With MATCH1 high, the LRU bit is set high so the next write to the same address with  $\overline{\text{M}}/\text{A}$  high will be to bank 2. With MATCH2 high, the LRU bit is set low so the next write to the same address with  $\overline{\text{M}}/\text{A}$  high will be to bank 1. When cascading these devices for wider address coverage, the MATCH1 outputs must be wire-ANDed together so an LRU write will not occur unless all MATCH1 outputs are high. In the same manner, the MATCH2 outputs (in width) must be tied together. When MATCH1 and MATCH2 are forced high during deselect, write, read, word reset, or reset, and LRU-W is taken low, a false LRU write will not occur. When a word reset occurs, the addressed LRU bit is updated so that the next write to that address will be to the reset (invalidated) location.

SCHS011 - D3512, JUNE 1990 - REVISED MARCH 1992

## parity generation and checking

The 'BCT2160 contains parity generation and checking circuitry. When the  $\overline{PE}$  output goes low, a parity error exists in one of the two tag RAMs.

During a write cycle, address bits or data on D0–D3 plus generated odd parity are written into the 5-bit memory location in either bank 1 or bank 2 that is addressed by A0–A12. The bank written to is selected automatically or manually via the BSEL input depending on the state of the  $\overline{M}/A$  input. Also during write, a parity error may be forced for diagnostic purposes by holding the  $\overline{R}$  input low. The addressed parity bits are included in the comparator circuitry of the 'BCT2160 so if a parity error occurs, the corresponding match output will be forced low. The LRU bit is not parity protected. The BANK outputs of the 'BCT2160s that are cascaded in width could be externally exclusive ORed to provide protection for the LRU bits.

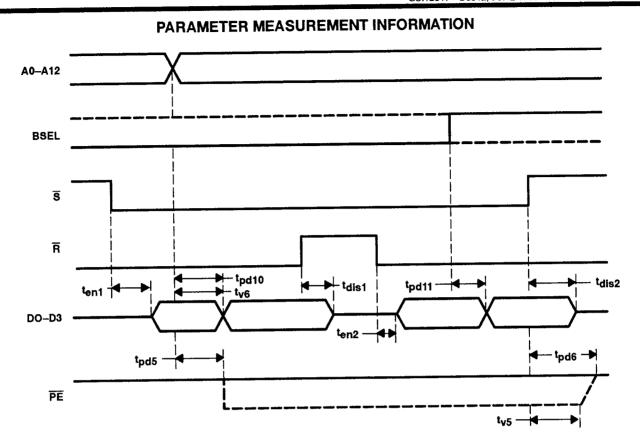

## operation as a data RAM

The 'BCT2160 can be used as a two-way 8K×4 data RAM with parity generation and checking. By tying the manual/auto  $(\overline{M}/A)$  pin low, the BSEL input can be used to select which bank is being written to or read from. Through the use of the select pin, the 'BCT2160 can be cascaded for a deeper data RAM. Inputs  $\overline{WR}$  and LRU-W should be tied high when using the 'BCT2160 as a data RAM.

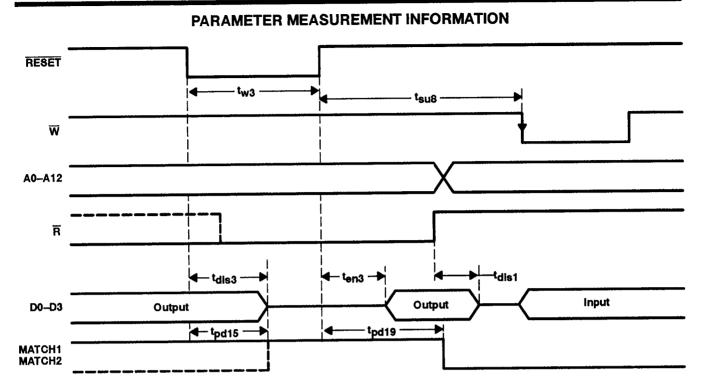

#### initialization

A reset input is provided for initialization. When RESET is taken low, all three 8K RAM locations are cleared to zero (with valid parity) and the MATCH1 and MATCH2 outputs are forced high. If a D0–D3 input of zero is compared to any memory location that has not been written into since reset, MATCH1 and/or MATCH2 will be high indicating that D0–D3 plus generated parity is equal to the reset memory location. By tying a single data input pin high, this bit will function as a valid bit and a match will not occur unless data has been written into the addressed memory location. When cascading in the width direction, only one bit needs to be tied high regardless of the address width. After reset, PE will be high for every addressed memory location indicating no parity error in the RAM data. After power-up, the 'BCT2160 must be initialized by resetting the device to ensure that all memory locations are at a known state. The 'BCT2160 could also be initialized by writing to every memory location (both banks).

## single-entry invalidation

In cache tag systems, it is often necessary to invalidate a tag memory location when data in the cache becomes inconsistent with the data in main memory or in additional caches. The word-reset function on the 'BCT2160 allows any addressed memory location to be cleared to zero with valid parity by taking the word reset pin  $\overline{(WR)}$  low. By tying one of the D0–D3 input pins high, that particular bit can be used as a valid bit. Whenever D0–D3 is compared to a memory location cleared by  $\overline{WR}$  (or by the master  $\overline{RESET}$ ), a miss will occur. If a D0–D3 input pin is not tied high, a false match will occur whenever a D0–D3 of zero is compared to a reset location. Word reset is independent of the input at the D0–D3 pins. The  $\overline{M}/A$  input must be low for a word reset to occur when  $\overline{WR}$  is taken low. Word reset can also be accomplished by holding  $\overline{WR}$  low and taking  $\overline{M}/A$  low to reset the addressed location. At the same time that an addressed location is reset, the addressed LRU bit is updated so that the next write to the same address with  $\overline{M}/A$  high will be to the reset location. Input BSEL determines which bank  $\overline{WR}$  affects. When cascading in width, all devices must receive the word-reset pulse for proper LRU RAM update.

Since the LRU bit is updated during a word reset operation, attention must be given when designing cache systems as to when the operation occurs. For instance, if a word reset is allowed at the same time as a cache line fill and it is followed by a tag write, the tag could actually be written to the wrong bank. This would result in the tag residing in one bank with its corresponding data residing in the other bank (a fatal error).

SCHS011 - D3512, JUNE 1990 - REVISED MARCH 1992

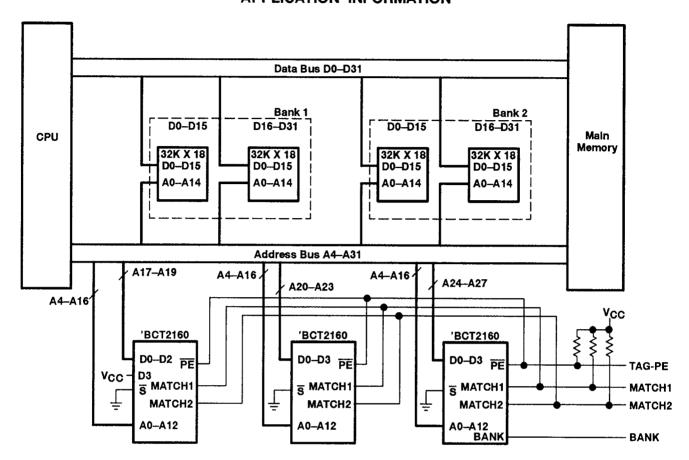

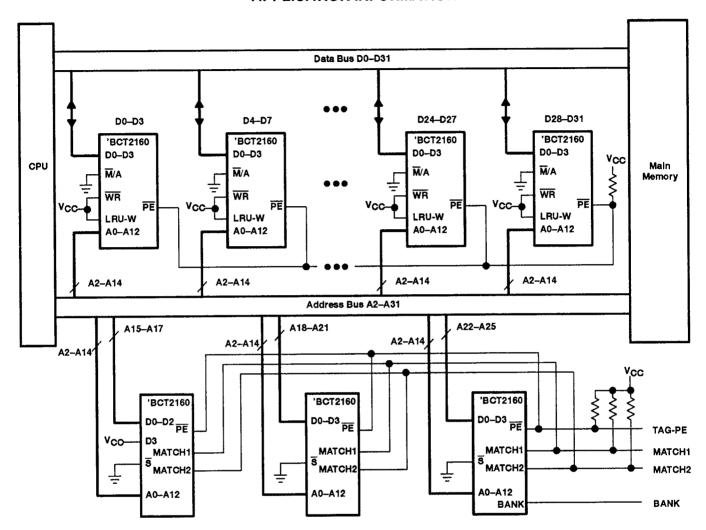

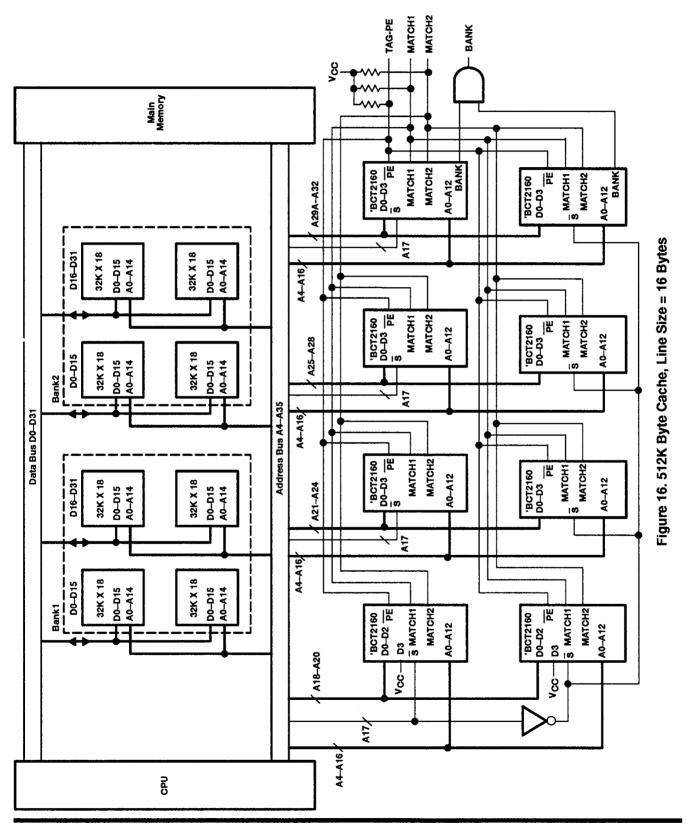

#### cascading the 'BCT2160

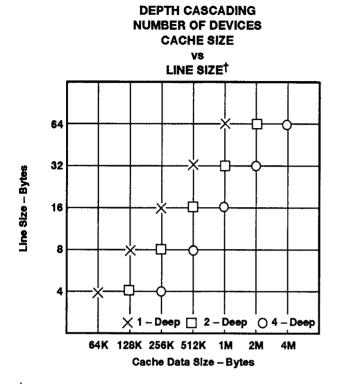

The 'BCT2160 is easily cascaded in width and depth. Wider addresses can be compared by driving the A0–A12 inputs of each device with the same index and applying the additional address bits to the D0–D3 inputs. The select ( $\overline{S}$ ) input allows this device to be easily cascaded in depth. When a device is deselected, the MATCH1 and MATCH2 outputs are driven high. This allows the match outputs to be wire tied or gated together when cascading in depth. A decoder can be used to drive the select inputs since the propagation delay from select to match is much faster than from address to match. MATCH1 and MATCH2 are open-drain outputs for easy wire-ANDing and must be wired-ANDed in the width direction to ensure proper LRU update. Figure 16 shows the 'BCT2160 cascaded.

## cache coherency through bus watching

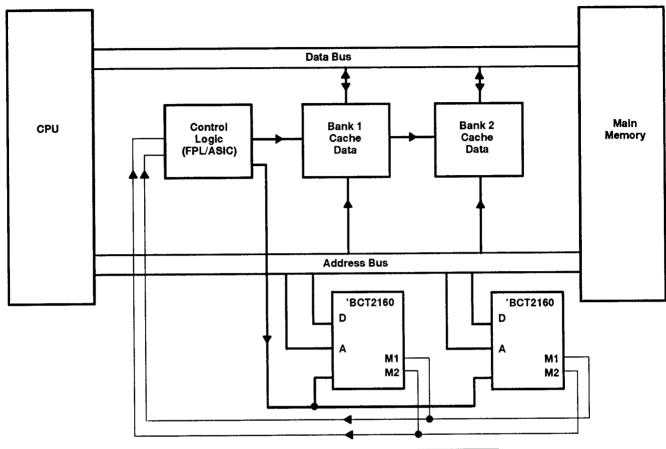

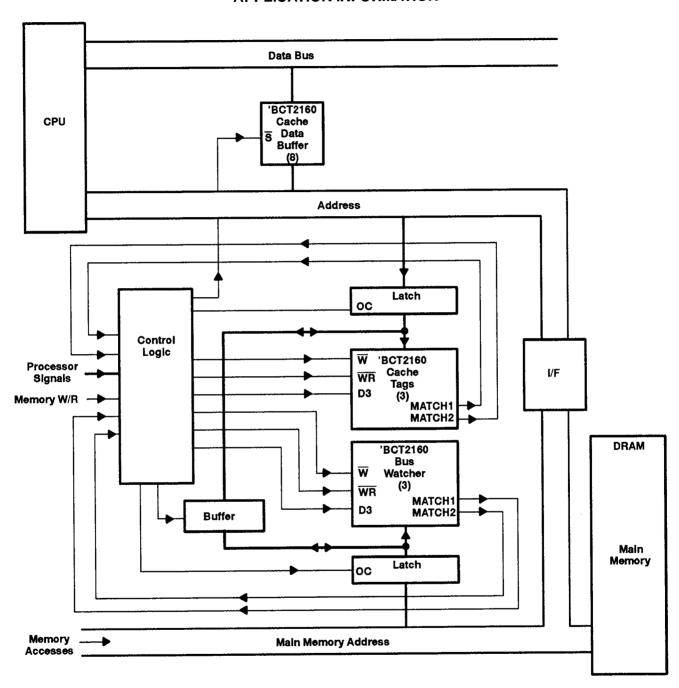

When implementing cache designs, cache coherency is usually a concern. A solution to this problem is to implement bus watching using the 'BCT2160. By storing the same tags in the bus watcher RAM as are stored in the cache tag RAM, the bus watcher will indicate a hit every time a cached address passes down the main address bus. If data is being modified in main memory, the index can be passed to the cache tag RAM for invalidation. Figure 17 shows a possible bus-watching application.

#### 'BCT2160/'ACT2160 comparison

When designing a system that will use the 'BCT2160 and the slower 'ACT2160 interchangeably, the following difference should be noted. The 'ACT2160 uses conventional write circuitry where data is written into the device as long as the write enable  $(\overline{W})$  is low. Address and data setup and hold times are with respect to the rising edge of  $\overline{W}$ . The 'BCT2160 uses self-timed write circuitry where an internal write pulse is generated when the write enable  $(\overline{W})$  is taken low. Address and data setup and hold times are with respect to the falling edge of  $\overline{W}$ .

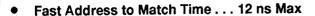

# logic symbol<sup>†</sup>

$<sup>\</sup>ensuremath{^{\dagger}}$  This symbol is in accordance with ANSI/IEEE Std 91-1984.

##

SCHS011 - D3512, JUNE 1990 - REVISED MARCH 1992

#### **Terminal Functions**

| PIN NAME         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A12           | Address inputs. Addresses a memory location in each of the three 8K RAM arrays. Address must be stable for the duration of the write cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BSEL             | Bank select input. This input is used in conjunction with the manual/auto, read and word reset functions. When BSEL is low, bank 1 is selected. When BSEL is high, bank 2 is selected. When M/A is high, the BSEL input does not affect writing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| BANK             | Bank output. The BANK output is used during a write to indicate which bank D0–D3 is being written into when $\overline{M}/A$ is high. BANK is low for bank 1 and high for bank 2. BANK is forced high during reset and deselect. BANK is used to indicate which cache SRAM bank the system data should be written into. When $\overline{W}$ is taken low, the output of the LRU RAM is latched causing BANK to remain stable. When $\overline{W}$ returns high, the latch returns transparent and the BANK output will switch if the LRU bit was changed. BANK is a totem-pole output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| D0-D3            | Data (tag) inputs and outputs. Provides input to RAM bank 1 or bank 2 depending on the state of the $\overline{S}$ , $\overline{W}$ , BSEL, $\overline{M}$ /A, and $\overline{W}\overline{R}$ pins. When in the compare mode, D0-D3 plus generated parity are compared to the addressed 5-bit memory location in bank 1 and bank 2. D0-D3 also function as outputs (see the $\overline{R}$ pin description).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LRU-W            | Least recently used write timing signal. In the compare mode, a falling edge on LRU-W will initiate an LRU write pulse if MATCH1 and/or MATCH2 are high. If a falling edge at LRU-W occurs before MATCH1 or MATCH2 are valid, the LRU write may not occur or a false LRU write could occur – this is critical when cascading. LRU-W will only initiate a LRU write pulse on a falling edge. LRU-W has no effect during any other mode of operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <del>M</del> ∕A  | Manual/auto input. The M/A input determines the bank select mode for writing data. When M/A is low, the bank to be written into is selected manually via the BSEL input. When the M/A input is high, the bank selection is done automatically. An internal 8K x 1 RAM is used to keep track of the bank to be written into using the least recently used (LRU) replacement algorithm. After the device is reset, the first write is into bank 1. The next time data is written to the same address, it will be stored in bank 2. Successive writes to the same address automatically alternate between bank 1 and bank 2. M/A can also be used to perform the word reset function. With WR low, the addressed location in the selected bank will be reset when M/A is taken low.                                                                                                                                                                                                                                                                                          |

| MATCH1<br>MATCH2 | Match outputs. When MATCH1 or MATCH2 are high during a compare cycle, D0–D3 plus generated parity equal the contents of one of two memory locations addressed by A0–A12. MATCH1 is high when D0–D3 matches D0–D3 stored in bank 1. MATCH2 is high when D0–D3 matches D0–D3 stored in bank 2. The match outputs are high during deselect, write, read, word reset, and reset. The logic level at the match outputs is fed back to the internal LRU circuitry. If a match output is high indicating a match when LRU-W is taken low, the LRU bit is adjusted so that the next write into that address will be into the other bank (LRU concept). If a match occurs with both banks (MATCH1 and MATCH2 high) and LRU-W is taken low, bank 2 will be written into next, if M/A was low; bank 1 will be written into next, if M/A was high. Since this device features open-drain match outputs, an external pullup resistor of 180 Ω minimum is required. If a parity error is present in bank 1 or bank 2 during compare, the corresponding match output will be forced low. |

| PE               | Parity error output. During compare cycles, a low level at $\overline{PE}$ indicates a parity error in one of the 8K x 5 RAMs. A parity error will force the corresponding match output low. $\overline{PE}$ will also indicate an error during read cycles. $\overline{PE}$ is an open-drain output and an external pullup resistor is required. $\overline{PE}$ is disabled during write, reset, word reset, and deselect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Ŕ                | Read input. When $\overline{R}$ is low and the device is selected, D0–D3 are enabled as outputs. The output data (tag) is determined by A0–A12 and the BSEL input. Outputs D0–D3 are disabled during write, word reset, reset, deselect, and when $\overline{R}$ is high. During write cycles, a parity error can be forced into the memory location addressed by A0–A12 of the selected bank when $\overline{R}$ is taken low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RESET            | Reset input. Asynchronously clears all three RAM arrays to zero with valid parity independent of the select pin when RESET is low. By tying a single data input high, a false match will not occur when a tag of zero is applied after initialization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <u>s</u>         | Chip select input. Enables device when $\overline{S}$ is low. When $\overline{S}$ is high, MATCH1 and MATCH2 are forced high. $\overline{PE}$ and D0-D3 are disabled when $\overline{S}$ is high and BANK is forced high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| WR               | Word Reset input. The WR input allows any addressed memory location to be cleared to zero with valid parity. This is achieved by taking WR low while in the manual mode (M/A low). The desired bank is selected using the BSEL input. When WR is asserted, the addressed LRU bit is adjusted so that the next write to that address (with M/A high) is into the reset memory location. By tying a single D0–D3 input high, this bit will act as a valid bit assuring that a false match will not occur with a reset memory location.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| W                | Write control input. When the device is selected and $\overline{W}$ is taken low, D0–D3 and generated parity are written into the addressed memory location in either bank 1 or bank 2. The RAM bank to be written into can be selected automatically or manually depending on the $\overline{M}/A$ input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

SCHS011 - D3512, JUNE 1990 - REVISED MARCH 1992

#### **FUNCTION TABLES**

#### WRITE MODE

|            |   |              | INP | UTS  |       |    |        | OUTPU  | TS |        | I/O   |                                    |

|------------|---|--------------|-----|------|-------|----|--------|--------|----|--------|-------|------------------------------------|

| W          | R | \$           | M/A | BSEL | RESET | WR | MATCH1 | MATCH2 | PE | BANKT  | D0-D3 | FUNCTION                           |

| ↓          | Н | L            | L   | L    | Н     | Н  | Н      | Н      | Н  | Н      | Input | Write into bank 1                  |

| <b>↓</b>   | Н | L            | L   | H    | Н     | Н  | Н      | Н      | Н  | Н      | Input | Write into bank 2                  |

| \          | Н | L            | Н   | Х    | Н     | X  | Н      | Н      | Н  | L      | Input | LRU write into bank 1              |

| <u></u>    | H | L            | H   | Х    | Н     | Χ  | Н      | Н      | Н  | Н      | Input | LRU write into bank 2              |

| ↓          | L | L            | L   | L    | Н     | Н  | Н      | Н      | Н  | Н      | Input | Write parity error into bank 1     |

| <u></u>    | L | L            | L   | Н    | H     | Н  | Н      | Н      | Н  | Н      | Input | Write parity error into bank 2     |

| ↓          | L | L            | Н   | X    | Н     | Н  | Н      | H      | Н  | L      | Input | LRU write parity error into bank 1 |

| <u></u>    | L | L            | Н   | Х    | Н     | Н  | Н      | Н      | Н  | Н      | Input | LRU write parity error into bank 2 |

| <b>↓</b> ‡ | Н | L            | Ļ   | X    | Н     | L‡ | Н      | Н      | Н  | н‡     | Hi-Z  | Write zero into selected bank      |

| L          | X | $\downarrow$ | Χ   | Х    | Н     | Н  | Н      | Н      | Н  | HorL   | Hi-Z  | No write occurs                    |

| L          | X | <u> </u>     | Н   | X    | Н     | Х  | н      | Н      | Н  | H or L | Hi-Z  | No write occurs                    |

#### **READ MODE**

|   |   |   | INP | UTS  | _     |    |        | OUTPU  | TS |        | I/O    |                             |

|---|---|---|-----|------|-------|----|--------|--------|----|--------|--------|-----------------------------|

| W | R | ទ | M/A | BSEL | RESET | WR | MATCH1 | MATCH2 | PE | BANK   | D0D3   | FUNCTION                    |

| Н | L | L | Х   | L    | Н     | Н  | Н      | Н      | Н  | H or L | Output | Read bank 1                 |

| Н | L | L | Χ   | Н    | H     | Н  | Н      | Н      | Н  | H or L | Output | Read bank 2                 |

| Н | L | L | H   | L    | Н     | X  | Н      | Н      | Н  | H or L | Output | Read bank 1                 |

| Н | L | L | Н   | н    | Н     | Χ  | Н      | Н      | Н  | H or L | Output | Read bank 2                 |

| H | L | L | Х   | Х    | Н     | Н  | Н      | Н      | L  | H or L | Output | Parity error in bank 1 or 2 |

| Н | H | L | X   | Х    | Н     | Н  | HorL   | HorL   | EN | H or L | Hi-Z   | Disable/compare             |

#### **COMPARE MODE**

|   |   |   | INF | PUTS |       |    | T ******** | OUTPU  | TS | -      | I/O   |                                   |

|---|---|---|-----|------|-------|----|------------|--------|----|--------|-------|-----------------------------------|

| W | R | 5 | M/A | BSEL | RESET | WR | MATCH1     | MATCH2 | PE | BANK   | D0-D3 | FUNCTION                          |

|   |   |   |     |      |       | -  | Н          | L.     | Н  | HorL   |       | Match bank 1, miss bank 2         |

|   |   |   |     |      |       |    | L          | н      | Н  | HorL   |       | Match bank 2, miss bank 1         |

| Н | Н | L | Х   | X    | Н     | Н  | Н          | Н      | Н  | HorL   |       | Match bank 1 and 2                |

|   |   |   | 1   | or   |       |    | L          | L      | Н  | HorL   | Input | Miss bank 1 and 2                 |

| Н | Н | L | Н   | X    | Н     | Χ  | L          | L      | L  | H or L |       | Parity error bank unknown         |

|   |   |   |     |      |       |    | L          | Н      | L  | HorL   |       | Parity error bank 1, match bank 2 |

|   |   |   |     |      |       |    | Н          | L      | L  | HorL   |       | Parity error bank 2, match bank 1 |

EN denotes enabled, H denotes a high level, L denotes a low level, X denotes a don't care level,  $\downarrow$  denotes the falling edge of the signal.

† The BANK output is transparent when  $\overline{W}$  is high and latched when  $\overline{W}$  is low, if  $\overline{M}/A$  is high. When writing with  $\overline{M}/A$  high, the BANK output indicates which bank D0–D3 is being written into. When writing with  $\overline{M}/A$  low, the BANK output will not indicate which bank is being written into. After  $\overline{W}$  returns high with  $\overline{M}/A$  low, the BANK output will indicate the correct LRU bit state.

$^{\ddagger}$  The state of BANK after  $\overline{W}$  and  $\overline{M}/A$  or  $\overline{W}$  and  $\overline{WR}$  return high is indeterminate. This operation is not recommended.

SCHS011 - D3512, JUNE 1990 - REVISED MARCH 1992

#### **FUNCTION TABLES (Continued)**

### RESET, WORD RESET, AND DESELECT MODE

|               |                     |               | INF                 | UTS           |       |             |        | OUTPU  | TS |        | 1/0   | FUNCTION              |

|---------------|---------------------|---------------|---------------------|---------------|-------|-------------|--------|--------|----|--------|-------|-----------------------|

| W             | R                   | Ŝ             | M/A                 | BSEL          | RESET | WR          | MATCH1 | MATCH2 | PE | BANK   | D0-D3 |                       |

| <del></del> - | <del></del>         | <del></del> - | X                   | X             | L     | Н           | Н      | Н      | Н  | Г      | Hi-Z  | Memory reset-selected |

| Н             | X                   | 1             | Н                   | X             | L     | X           | н      | н      | Н  | L      | Hi-Z  | Memory reset-selected |

| <del>''</del> | $\frac{\hat{x}}{x}$ | <del>-</del>  | X                   | $\frac{x}{x}$ |       | X           | Н      | Н      | Н  | Н      | Hi-Z  | Memory reset-deselect |

| <u>^</u>      | $\frac{\hat{x}}{x}$ | <del></del> - | Lor↓                | 1             | Н     | <del></del> | н      | Н      | Н  | L†     | Hi-Z  | Word reset in bank 1  |

| Н             | X                   |               | 1                   | L             | H     | Lor↓        | l н    | Н      | Н  | լ†     | Hi-Z  | Word reset in bank 1  |

| <u>-</u>      | $\frac{\hat{x}}{x}$ |               | Lor↓                | — Н           | Н.    | <del></del> | Н      | Н      | Н  | Lf     | Hi-Z  | Word reset in bank 2  |

|               | •                   | _<br>         |                     | н             | н     | Lor↓        | Н      | н      | н  | լ†     | Hi-Z  | Word reset in bank 2  |

| H             | $\frac{x}{x}$       | <u> </u>      | <del></del>         | <u></u>       | — ;;  | L           | H      | Н      | Н  | Н      | Hi-Z  | No word reset         |

|               |                     | <del>*</del>  | <u>-</u> -          | $\frac{x}{x}$ | н     |             | HorL   | H or L | EN | HorL   | Hi-Z  | Word reset disabled   |

| Н             |                     | 1             | Х                   | X             | Н     | H           | HorL   | H or L | EN | H or L | Hi-Z  | Word reset disabled   |

| H<br>X        | <u> </u>            | <u>-</u> -    | $\frac{\hat{x}}{x}$ | $-\hat{x}$    | — ;;  | <del></del> | Н      | Н      | Н  | Н      | Hi-Z  | Device disabled       |

#### **LRU WRITE**

| ร              | WR             | $\overline{\mathbf{w}}$ | M/A                                       | BSEL                | LRU-W <sup>‡</sup> | MATCH1   | MATCH2 | QI§ | LRU WRITE   | QN | FUNCTION                                   |

|----------------|----------------|-------------------------|-------------------------------------------|---------------------|--------------------|----------|--------|-----|-------------|----|--------------------------------------------|

| -L             | X              | <u></u>                 | H                                         | X                   | X                  | Н        | Н      | L   | YES         | Н  | Write to bank 1, selected by LRU circuitry |

| _              | X              | Ţ                       | н                                         | X                   | X                  | Н        | Н      | Н   | YES         | L  | Write to bank 2, selected by LRU circuitry |

| -              | <del>-</del> - | Ť                       | <del></del>                               | L                   | X                  | H        | H      | Х   | YES         | Н  | Write to bank 1, selected by BSEL input    |

| L              | Н              | ĭ                       | ı                                         | H                   | X                  | Н        | Н      | Х   | YES         | L  | Write to bank 2, selected by BSEL input    |

| <u> </u>       | <u> </u>       | _ <u>*</u> _            | _ <u>_</u>                                | <u></u>             | $\frac{x}{x}$      | Н.       | H      | X   | NO          | QI | No write occurs                            |

| $\downarrow$   | Х              | L                       | H                                         | X                   | X                  | н        | Н      | Х   | NO          | QI | No write occurs                            |

| L              | $-\hat{H}$     | <u>-</u>                | _ <u>''</u> _                             | - X                 | <del></del>        | L        |        | Х   | NO          | QI | Miss, no LRU update                        |

| <u> </u>       | <u>- Н</u>     | <del>- Н</del>          | $-\hat{x}$                                | $\frac{\hat{x}}{x}$ | <u>`</u>           | Н        | L      | Х   | YES         | Н  | Match bank 1, LRU update                   |

| 1              | X              | Н                       | Н                                         | X                   | Ţ                  | Н        | Ł      | Х   | YES         | Н  | Match bank 1, LRU update                   |

| ĻĻ             | <del>-</del>   | - <del> </del>          | X                                         | $\frac{\lambda}{X}$ | <u>`</u>           | <u></u>  | H      | Х   | YES         | L  | Match bank 2, LRU update                   |

|                | X              | Н                       | Н                                         | X                   | Ţ                  | Ĺ        | Н      | Х   | YES         | L  | Match bank 2, LRU update                   |

| L-             | <del>-</del> - | <u>П</u>                | <u>                                  </u> | <u>X</u> _          | <u>`</u>           | <u>-</u> | Н      | X   | YES         | Н  | Match bank 1 and 2, LRU update             |

| L              | Х              | Н                       | Н                                         | X                   | .].                | H        | Н      | Х   | YES         | L  | Match bank 1 and 2, LRU update             |

| L              | $-\hat{+}$     | <del></del> -           | <u>''</u> _L                              | <u>-</u> -          | <del></del>        | Н        | Н      | X   | YES         | L  | Word reset in bank 1                       |

| L              | 1              | Н                       | Ţ                                         | L                   | X                  | Н        | Н      | Х   | YES         | L  | Word reset in bank 1                       |

| 는              | <u> </u>       | - <del>   </del>        | <u> </u>                                  | Н_                  | X                  | Н        |        | Х   | YES         | Н  | Word reset in bank 2                       |

| 1:             | ¥<br>1         | Н                       | ↓<br>↓                                    | H                   | X                  | H        | Н      | Х   | YES         | Н  | Word reset in bank 2                       |

| <del>  -</del> |                | <br>H                   | — <del>ў</del>                            | X                   | <u>X</u>           | H        | ——     | Х   | NO          | QI | Word reset disabled                        |

| -              | Η              | H                       |                                           | X                   | X                  | н        | H      | Х   | NO          | QI | Word reset disabled                        |

| 1              | 1              | <u></u> -               | <del>`</del> _                            | ^_                  | X                  | Н        | — Н    | X   | NO          | QI | No word reset occurs                       |

| H              | <u>L</u>       | X                       | X                                         |                     | X                  | Н        | Н      | X   | NO          | QI | Device disabled                            |

|                |                |                         |                                           |                     | ^_                 |          |        |     | <del></del> |    | des of the signal                          |

H denotes a high level, L denotes a low level, X denotes a don't care level, \( \psi \) denotes the falling edge of the signal.

The BANK output is forced low during word reset. After a word reset in bank 2, the BANK output will be high.

<sup>‡</sup> LRU-W is falling-edge-triggered and has effect only during the compare mode. A falling edge at LRU-W must not be allowed immediately after  $\overline{W}$  or  $\overline{WR}$  high, since the match outputs may be switching.

<sup>§</sup> QI is the state of the LRU RAM output before a LRU write occurs.

QN is the state of the LRU RAM output after a LRU write occurs. This level will be seen at the BANK output, when the write (W) and word reset  $(\overline{WR} \text{ or } \overline{M}/A)$  signals are high.

SCHS011 - D3512, JUNE 1990 - REVISED MARCH 1992

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, Voc (see Note 1)                             |                            |

|--------------------------------------------------------------------|----------------------------|

| Input voltage range, any input                                     | -1.5 V to 7 V              |

| Input clamp current I (V = 0 or V = V                              | -1.5 V to 7 V              |

| Contract all an interest, ilk (Al < 0 Ot Al > ACC)                 | ± 25 mA                    |

| $\alpha$                                                           | 1 OF A                     |

| Continuous output current, $I_{O}(V_{O} = 0 \text{ to } V_{CC})$ : | D0-D3, BANK ± 25 mA        |

|                                                                    | MATCHE MATCHO DE           |

| Continuous surrent through M                                       | MATCH1, MATCH2, PE ± 50 mA |

| Continuous current through VCC or GND                              | ± 000 m A                  |

| Operating free-air temperature range                               | 0°C to 70°C                |

| Storage temperature range                                          | 0°C to 70°C                |

| Load tomporature of Commo (4/40 to 1) (                            | -65°C to 150°C             |

| read temperature 1,0 mm (1/16 inch) from case f                    | or 10 seconds              |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to GND.

# recommended operating conditions (see important notice)

| 1/. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | MIN         | NOM | MAX                  | UNIT       |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|-----|----------------------|------------|

| Vcc | Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    | 4.75        | 5   | 5.25                 | V          |

| VIH | High-level input voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    | 2.2         |     |                      | \ <u>\</u> |

| VIL | Low-level input voltage (see Note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    | 2.2         |     | V <sub>CC</sub> +0.5 | V          |

| Vон | High-level output voltage, MATCH1, MATCH2, and PE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |             |     | 0.8                  | V          |

| ЮН  | High-level output current, D0-D3 and BANK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <del></del>        | <del></del> |     | 5.25                 | ٧          |

|     | 5 Table 1 Tabl |                    |             |     | 8                    | mΑ         |

| loL | Low-level output current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D0-D3, BANK        |             |     | 8                    |            |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MATCH1, MATCH2, PE |             |     | 27                   | mA         |

| TA  | Operating free-air temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    | 0           |     | 70                   | °C         |

NOTE 2: The algebraic convention, where the more negative (less positive) limit is designated as minimum, is used in this data sheet for logic voltage levels only.

#### important notice

Negative undershoot at the address or data inputs could cause this device to reset if the  $V_{IH}$  level at  $\overline{RESET}$  is at its minimum high level (2.2 V). In systems with - 1.5 V or more of undershoot at the address and data inputs, it is recommended that the minimum  $V_{IH}$  level at  $\overline{RESET}$  be 4 V. As with all designs, proper termination and capacitive bypass techniques should be employed. Unused inputs should be tied to either  $V_{CC}$  or GND.

Due to the high-performance characteristics of this device and to ensure the integrity of stored data (or tag), the address inputs must not be allowed to float through the input threshold region (1.2 V - 1.8 V). Rise and fall times at the threshold region of the address inputs must not exceed 20 ns/V. Slow rise and fall times through the threshold region may be eliminated by not using pullup resistors on the address lines and minimizing the high-impedance time when switching between bus drivers. An alternate approach is to use latches or registers in front of the cache tag address inputs to eliminate floating-address conditions. Ground bounce, due to simultaneous switching, into the threshold region of the address inputs should be avoided in order to ensure that a slow rise/fall condition does not occur.

SCHS011 - D3512, JUNE 1990 - REVISED MARCH 1992

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                |                               |                       | SN74BCT2160-                                                                          | 12  | UNIT  |

|----------------|-------------------------------|-----------------------|---------------------------------------------------------------------------------------|-----|-------|

|                | PARAMETE                      | R                     | TEST CONDITIONS MIN TYPT                                                              | XAN | ONLI  |

| Vон            | High-level output voltage     | D0-D3, BANK           | V <sub>CC</sub> = 4.75 V, I <sub>OH</sub> = -8 mA 2.4                                 |     | V     |

| VOH.           | Trigit for or output rollings | D0-D3, BANK           | V <sub>CC</sub> = 4.75 V, I <sub>OL</sub> = 8 mA                                      | 0.4 |       |

| VOL            | Low-level output voltage      | MATCH1, MATCH2,<br>PE | V <sub>CC</sub> = 4.75 V, I <sub>OL</sub> = 27 mA                                     | 0.4 | · · · |

| ЮН             | High-level output current     | MATCH1, MATCH2,<br>PE | V <sub>CC</sub> = 4.75 V, V <sub>OH</sub> = 5.25 V                                    | 10  | μА    |

| lı .           | Input current                 |                       | V <sub>CC</sub> = 5.25 V, V <sub>I</sub> = 0 to V <sub>CC</sub>                       | ±5  | μA    |

| loz            | Off-state output current      |                       | $V_{CC} = 5.25 \text{ V}$ , $V_O = 0 \text{ to } V_{CC}$ , $\overline{S}$ at $V_{IH}$ | ±10 | μА    |

| ICC1           | Supply current (operating     | )                     | V <sub>CC</sub> = 5.25 V, RESET at V <sub>CC</sub> , S at 0 V 110                     | 180 | mA    |

| ICC2           | Supply current (reset)        | <u> </u>              | V <sub>CC</sub> = 5.25 V, RESET at 0 V, S at 0 V 38                                   | 75  | mΑ    |

| ICC3           | Supply current (deselecte     | ed)                   | V <sub>CC</sub> = 5.25 V, RESET at V <sub>CC</sub> , S at V <sub>CC</sub> 80          | 150 | mA    |

| C <sub>i</sub> | Input capacitance‡            | <u></u>               | f = 1 MHz                                                                             | 5   | рF    |

| C <sub>o</sub> | Output capacitance            |                       | f = 1 MHz                                                                             | 5   | pF    |

<sup>&</sup>lt;sup>‡</sup> This is the capacitance at an input, output, or I/O pin.

# timing requirements over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

#### pulse durations

|                 | durations                  |                     | SN74B | CT2160-12 | LIAIP |

|-----------------|----------------------------|---------------------|-------|-----------|-------|

|                 | PARAMETEI                  | R                   | MIN 7 | TYPT MAX  | UNIT  |

|                 |                            | High                | 7     |           | กร    |

| t <sub>w1</sub> | Pulse duration, LRU-W      | Low                 | 7     |           | 110   |

| t <sub>w2</sub> | Pulse duration, W low      |                     | 10.5  |           | ns    |

| tw3             | Pulse duration, RESET low  |                     | 35    |           | ns    |

| ·W3             |                            | WR low with M/A low | 10    |           | กร    |

| t <sub>w4</sub> | Pulse duration, word reset | M/A low with WR low | 10    |           |       |

<sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

SCHS011 - D3512, JUNE 1990 - REVISED MARCH 1992

# timing requirements over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (continued) setup and hold times

|                  | DADAMETED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       | SN74BC1 | 2160-12       |     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------|---------------|-----|