## 82C5087

IBM PC-AT Host SCSI Controller

Datasheet

May, 1991

PRELIMINARY

#### **Copyright Notice**

Copyright © 1991, Chips and Technologies, Inc.

#### Trademark Acknowledgement

Chips and Technologies™, CHIPS™, CHIPS/250™, CHIPS/280™, CHIPS/450™, CHIPS/450™, CHIPSpak™, CHIPSport™, CHIPSet™, CHIPSlink™, LeAPsetsx™, SMARTMAP™, are trademarks of CHIPS and Technologies, Inc.

IBM ATTM, IBM XTTM, PS/2TM, and Personal System/2TM are trademarks and IBM, is a registered trademark of International Business Machines Corporations.

#### Disclaimer

This data sheet is provided for the general information of the customer. Chips and Technologies, Inc., reserves the right to modify these parameters as necessary and the customer should ensure that it has the most recent revision of the data sheet. CHIPS makes no warranty for the use of its products and bears no responsibility for any errors which may appear in this document. The customer should be on notice that the field of personal computers is the subject of many patents held by different parties. Customers should ensure that they take appropriate action so that their use of the products does not infringe upon any patents. It is the policy of CHIPS and Technologies, Inc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

### Scope

#### Contents

This manual contains the information needed to program the CHIPS F82C5087 SCSI-Bus Interface Controller to implement the SCSI (Small Computer System Interface) interface on a host computer or a device controller. A working knowledge of the SCSI interface is assumed.

The information in this manual is divided into five chapters, one appendix, and a glossary.

- Chapter 1 provides an overview of the CHIPS F82C5087 IBM AT HOST SCSI Controller.

- Chapter 2 describes the F82C5087 hardware specifications. It supplies

physical and functional pin specifications, signal descriptions, electrical

specifications, and packaging specifications.

- Chapter 3 describes the operational modes of the F82C5087.

- Chapter 4 provides a detailed description of the function and operation of each of the 24 internal registers of the F82C5087.

- Chapter 5 provides a detailed description of the operation of each of the 46 commands of the F82C5087.

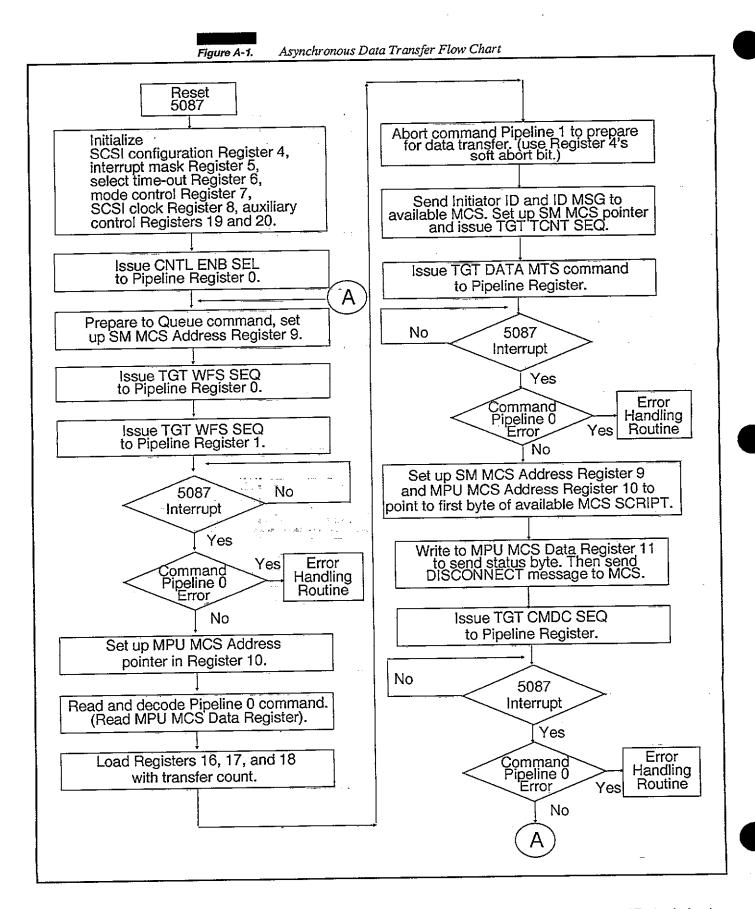

- Appendix A contains a sample flow chart that illustrates the steps involved in completing an asynchronous data transfer to a target device.

- The glossary provides a list of abbreviations and definitions of the key terms used throughout this manual

## Related Publications

- CHIPS 5086B SCSI Bus Interface controller Reference Manual

- CHIPS 5055B DMA Memory Controller/Programmable Data Sequencer Reference Manual

- CHIPS 5080 SCSI Multifunctional Device Reference Manual.

- American National Standard for Information Systems Small Computer System Interface (SCSI). (X3.131-1986.)

## Notational Conventions

The following conventions are used throughout this manual:

UPPERCASE is used to indicate names of commands, signals, SCSI bus phases.

a minus sign prefix to a signal name indicates an active low polarity.

+ a plus sign prefix to a signal name indicates an active high polarity.

| Chapter 1: Overview 1-3                       | Ĺ |

|-----------------------------------------------|---|

| Introduction                                  | 1 |

| Hardware Features                             | 2 |

| Firmware Features                             | 3 |

| Typical Applications                          | 4 |

| Host Adapter                                  | 4 |

| Motherboard                                   | 4 |

| Operational Modes                             | 6 |

| Initiator or Target Mode                      | 6 |

| Non-Differential Mode                         | 7 |

| Asynchronous or Synchronous Mode              | 7 |

| Master or Slave Mode                          | 7 |

| System Interface                              | 8 |

| I/O Interface                                 | 8 |

| Command Set                                   |   |

| Memory Structure                              | 0 |

| Performance Specifications                    | 0 |

| Chapter 2: Hardware Specifications 2-         | 1 |

| Physical Specifications                       | 1 |

| Pin Descriptions                              | 2 |

| Package Specifications                        | 4 |

| Functional Chip Specifications 2-             | 5 |

| Functionality of the F82C5087 Host Adapter 2- | 5 |

| Interfacing with the SCSI Control Bus         | 7 |

| Interfacing with the SCSI Data Bus            | 7 |

| Interfacing with the Host Computer's MPU 2-   | 7 |

| Interfacing with the Host Computer's DMA Controller 2- |

|--------------------------------------------------------|

| Signal Descriptions                                    |

| I/O Signals                                            |

| Signals Specific to 8085/8051 Mode                     |

| Signals Specific to Z8 Mode                            |

| Signals Specific to Wide Data Bus Transfers 2-1        |

| Pad Drive Capacity                                     |

| Electrical Specifications                              |

| Clock Timing                                           |

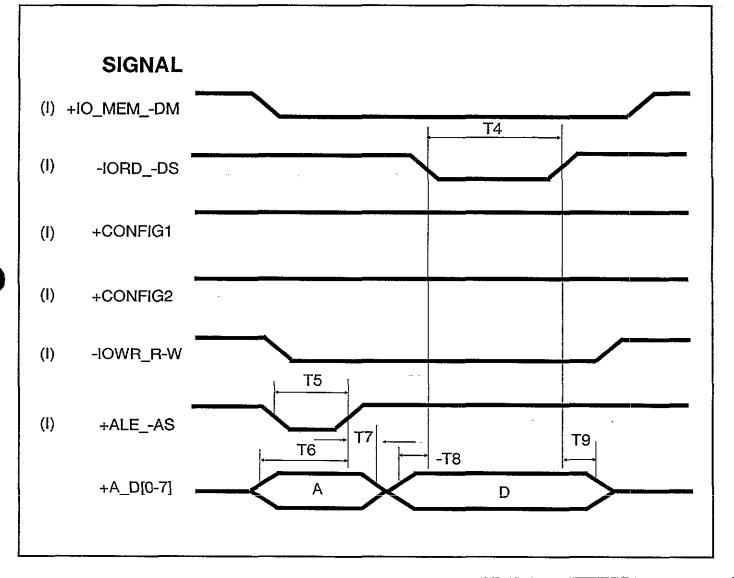

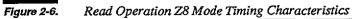

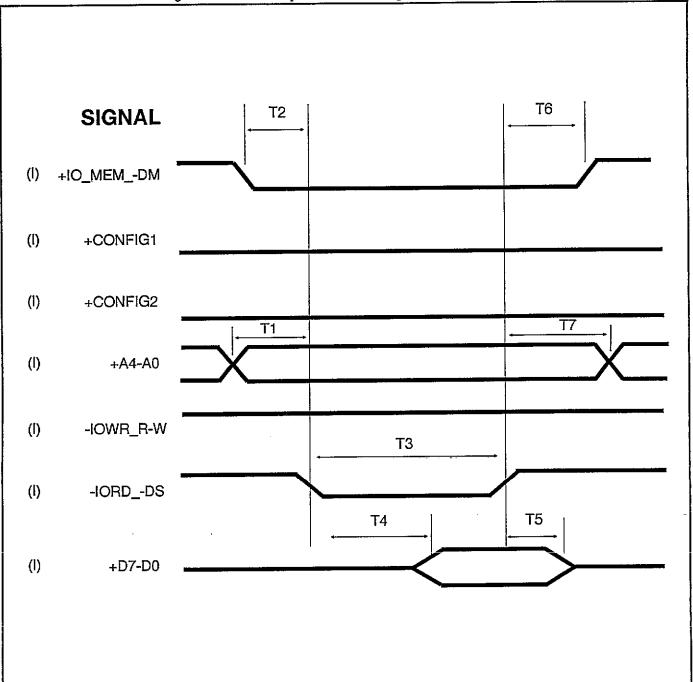

| Z8 Mode Timing                                         |

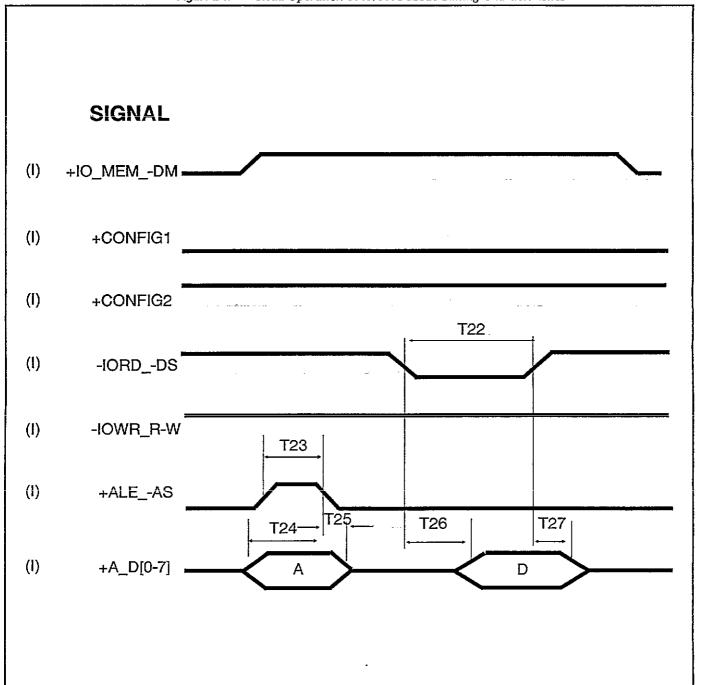

| 8085/8051 Mode Timing                                  |

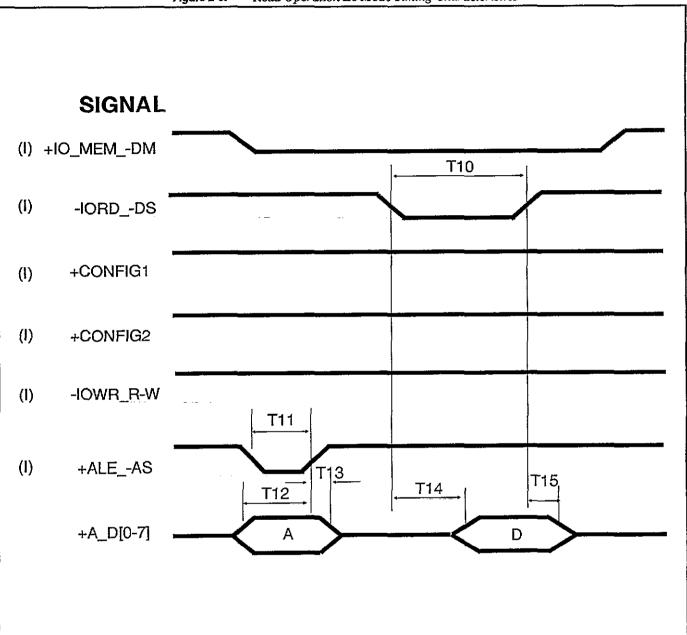

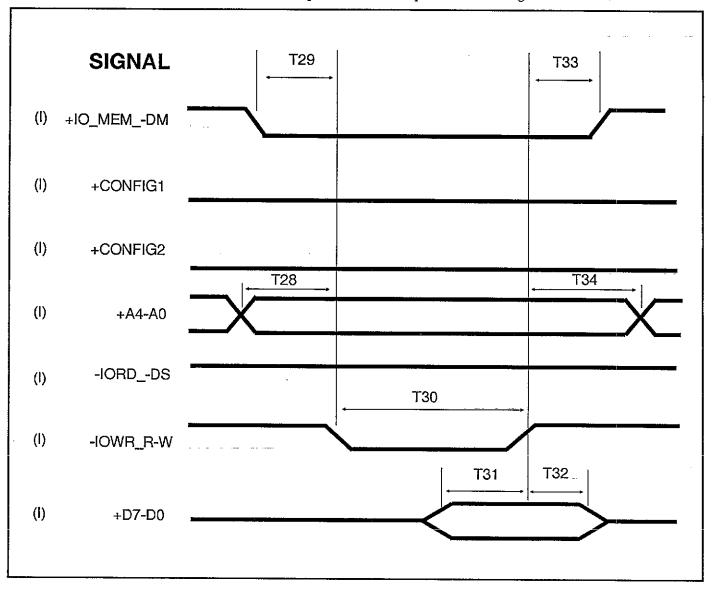

| Non-multiplexed Mode Timing                            |

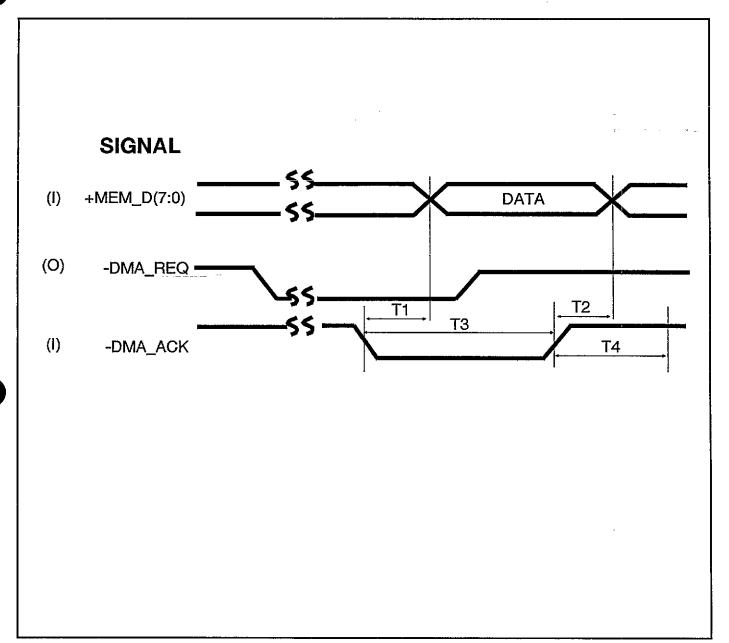

| Timing for Data Transfers to System Memory 2-2         |

| Timing for I/O Interface to Buffer Memory 2-3          |

| SCSI Interface Timing                                  |

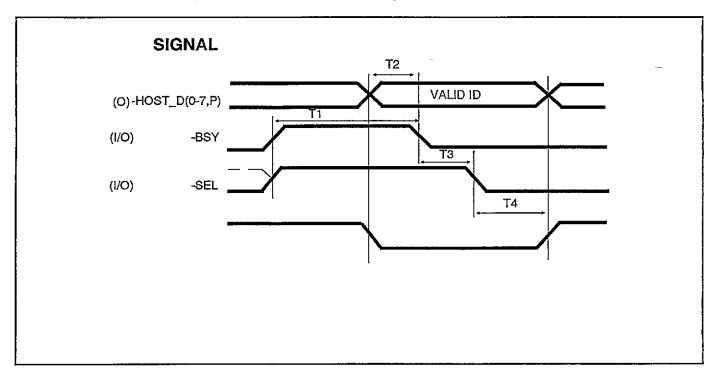

| Timing for the SCSI Bus ARBITRATION Phase 2-3          |

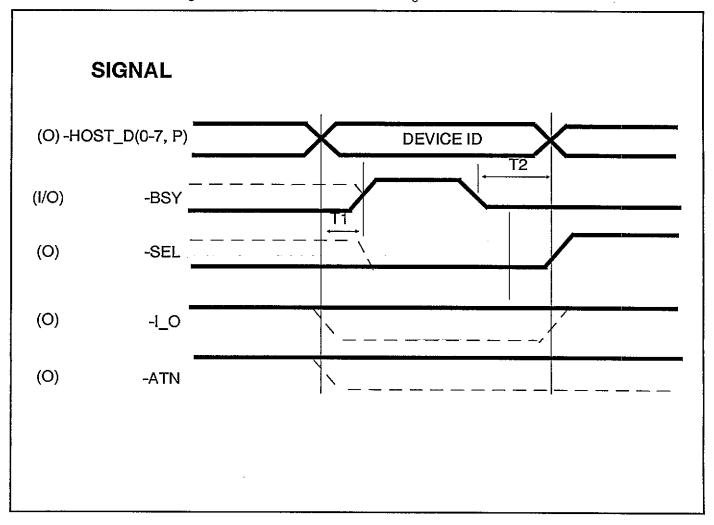

| Timing for SCSI Bus SELECT/RESELECT Phases 2-3         |

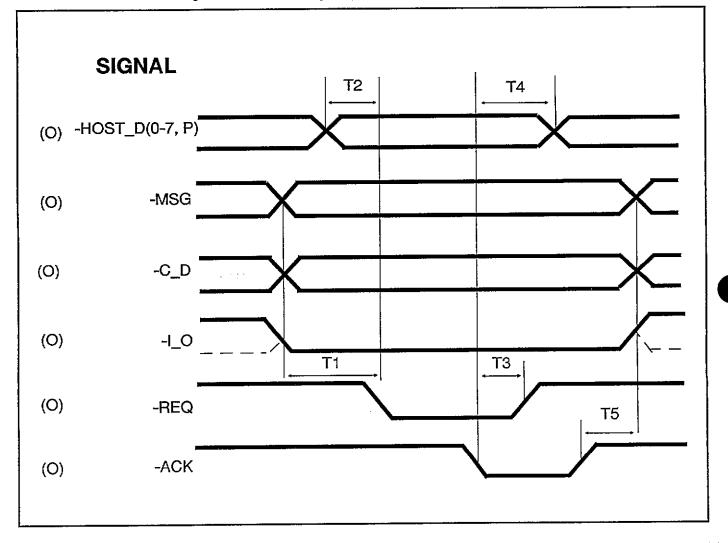

| Timing for Asynchronous/Synchronous Transfers 2-3      |

| D.C. Specifications                                    |

| Absolute Maximum Ratings                               |

| Standard Test Conditions                               |

| D.C. Characteristics                                   |

| D. C. Characteristics for Drivers/Receivers            |

| Chapter 3: Operation 3-1                               |

| Modes of Operation                                     |

| Initiator and Target Modes                             |

| Role of Initiator                                      |

| Role of the Target                                     |

| Transfer Modes                                         |

| Asynchronous Transfers                                 |

| Synchronous Transfers                                  |

| Master/Slave Mode                                      |

| Master/Master Mode                                     |

| Slave/Master Mode                                      |

| Slave/Slave Mode                                       |

| Synchronizing Memory Data Bus Transfers                       |

|---------------------------------------------------------------|

| Synchronizing SCSI Bus Data Transfers                         |

| Hardware Specifications                                       |

| Method of Operation                                           |

| I/O Interface                                                 |

| Example 1. I/O Interface Providing a Path to the SCSI Bus 3-8 |

| Example 2. I/O Interface to Buffer Memory                     |

| Example 3. I/O Interface to the MPU 3-8                       |

| Example 4. I/O Interface to the Host Computer                 |

| Command Set                                                   |

| Memory Structure                                              |

| Data FIFO                                                     |

| MCS Script                                                    |

| MCS Address Pointers                                          |

| MCS Auto Advance                                              |

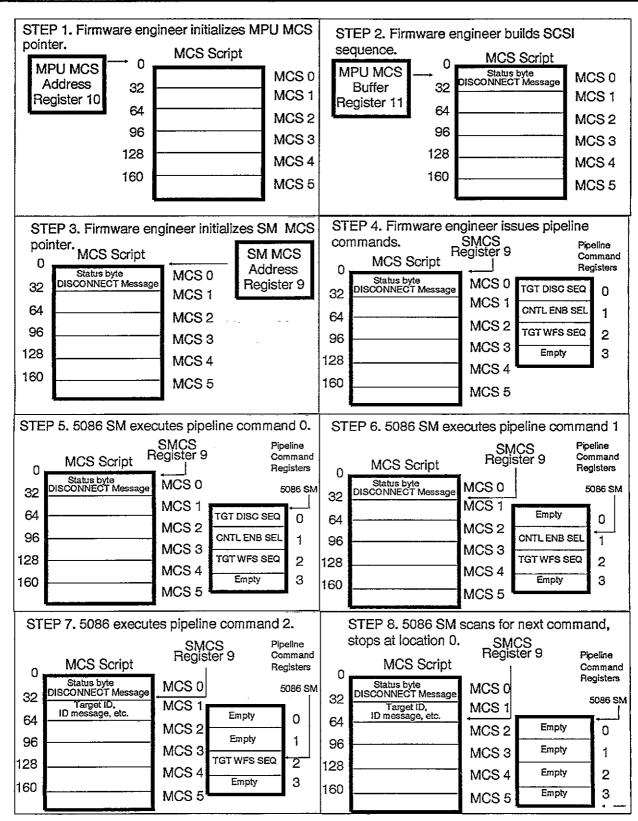

| Pipelining Structure                                          |

| Example 1. SCSI Transfer Command                              |

| Example 2. SCSI Select/Reselect Process                       |

| Target ID                                                     |

| Identify Message                                              |

| Tag Message                                                   |

| Multi-byte Commands                                           |

| Chapter 4: Registers 4-1                                      |

| Function of Registers                                         |

| Register Description                                          |

| Registers 0-3 (0-3h)                                          |

| Register 0-3 (0-3h) - Write Operation                         |

| Registers 0-3 (0-3h) - Read Operation                         |

| Register 4 (4h)                                               |

| Register 4 (4h) - Write Operation                             |

| Register 4 - Read Operation                                   |

| Register 5 (5h)                                               |

| Register 5 (5h) - Write Operation                             |

| Register 5 (5h) - Read Operation                              |

| Register 6 (6h)                                            |

|------------------------------------------------------------|

| Register 6 (6h)- Write Operation                           |

| Register 6 (6h) - Read Operation                           |

| Register 7 (7h)                                            |

| Register 7 (7h) - Write Operation                          |

| Register 7 (7h) - Read Operation                           |

| Register 8 (8h)                                            |

| Register 8 (8h) - Write Operation (Lower 4 bits only) 4-19 |

| Register 8 (8h) - Read Operation                           |

| Register 9 (9h)                                            |

| Register 9 (9h) - Write Operation                          |

| Register 9 (9h) - Read Operation                           |

| Register 10 (0Ah)                                          |

| Register 10 (0Ah) - Write/Read Operation 4-21              |

| Register 11 (0Bh)                                          |

| Register 11 (0Bh) - Write Operation                        |

| Register 11 (0Bh) - Read Operation                         |

| Register 12 (0Ch)                                          |

| Register 12 (0Ch) - Write/Read Operation                   |

| Register 13 (0Dh)                                          |

| Register 13 (0Dh)- Write Operation                         |

| Register 13 (0Dh)- Read Operation                          |

| Register 14 (0Eh)                                          |

| Register 14 (0Eh) - Write Operation                        |

| Register 14 (0Eh) - Read Operation                         |

| Register 15 (0Fh)                                          |

| Register 15 (0Fh) - Write Operation                        |

| Register 15 (0Fh) - Read Operation                         |

| Registers 16 - 18 (10 - 12h)                               |

| Register 16 - 18 (10 - 12h)- Write Operation 4-28          |

| Registers 16 - 18 (10 - 12h) - Read Operation              |

| Register 19 (13h)                                          |

| Register 19 (13h) - Write Operation                        |

| Register 19 (13h) - Read Operation                         |

| Register 20 (14h)                                          |

| Register 20 (14h) - Write Operation         |

|---------------------------------------------|

| Register 20 (14h) - Read Operation          |

| Register 21 (15h)                           |

| Register 21 (15h)- Write Operation          |

| Register 21 (15h) - Read Operation          |

| Register 22 (16h)                           |

| Register 22 (16h) - Write Operation         |

| Register 22 (16h) - Read Operation          |

| Register 23 (17h)                           |

| Register 24 (18h)                           |

| Register 25 (19h)                           |

| Register 25 (19h) - Write Function          |

| Chapter 5: Commands 5-1                     |

| Command Functions                           |

| Command Description                         |

| Command Code                                |

| Bus Condition                               |

| Execution Time                              |

| Operational Description                     |

| Possible Errors                             |

| Control Command Descriptions 5-4            |

| CNTL NOP - No Operation                     |

| Operational Description                     |

| CNTL RST FIFO - Control Reset Data FIFO 5-6 |

| Operational Description                     |

| CNTL RST ON - Control RESET On              |

| Operational Description                     |

| CNTL RST OFF - Control RESET                |

| Operational Description                     |

| CNTL ATN ON - Control Attention On 5-8      |

| Operational Description                     |

| CNTL ATN OFF - Control Attention Off 5-8    |

| Operational Description                     |

| CNTL ENB SEL - Control Enable Select 5-9    |

| Operational Description                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CNTL DIS SEL - Control Disable Select 5-10                                                                                                                                        |

| Operational Description                                                                                                                                                           |

| CNTL ENB RESEL - Control Enable Reselect 5-11                                                                                                                                     |

| Operational Description                                                                                                                                                           |

| CNTL DIS RESEL - Control Disable Reselect 5-12                                                                                                                                    |

| Operational Description                                                                                                                                                           |

| CNTL ENB ADV - Control Enable MCS Auto Advance 5-13                                                                                                                               |

| Operational Description                                                                                                                                                           |

| CNTL DIS ADV - Control Disable MCS Auto Advance 5-14                                                                                                                              |

| Operational Description                                                                                                                                                           |

| CNTL DATA PTM - Control Data from MPU to Memory Data Bus 5-15                                                                                                                     |

| Operational Description                                                                                                                                                           |

| CNTL DATA MTP - Control Data from Memory Data Bus to MPU                                                                                                                          |

| Operational Description                                                                                                                                                           |

| Initiator Command Descriptions 5-17                                                                                                                                               |

| INIT SWOA SEQ - Initiator Select without Attention Sequence . 5-18                                                                                                                |

| Operational Description                                                                                                                                                           |

| Possible Errors                                                                                                                                                                   |

| INIT SWA SEQ - Initiator Select with Attention Sequence 5-19                                                                                                                      |

| Operational Description                                                                                                                                                           |

| Possible Error                                                                                                                                                                    |

| INIT SWOA CMD - Initiator Select without Attention Command 5-21                                                                                                                   |

| Operational Description                                                                                                                                                           |

| Possible Errors                                                                                                                                                                   |

|                                                                                                                                                                                   |

| INIT SWA CMD - Initiator Select with Attention Command 5-22                                                                                                                       |

| INIT SWA CMD - Initiator Select with Attention Command 5-22  Operational Description                                                                                              |

| ·                                                                                                                                                                                 |

| Operational Description                                                                                                                                                           |

| Operational Description                                                                                                                                                           |

| Operational Description       5-22         Possible Errors       5-22         INIT REC INFO - Initiator Receive Information       5-23                                            |

| Operational Description       5-22         Possible Errors       5-22         INIT REC INFO - Initiator Receive Information       5-23         Operational Description       5-23 |

| Possible Errors                                                     |

|---------------------------------------------------------------------|

| INIT DATA PTS - Initiator Receive Data from MPU to SCSI Bus         |

| Operational Description                                             |

| Possible Errors                                                     |

| INIT DATA STM - Initiator Receive Data from SCSI to Memory Data Bus |

| Operational Description                                             |

| Possible Errors                                                     |

| INIT DATA STP - Initiator Receive Data from SCSI to MPU Bus         |

| Operational Description                                             |

| Possible Errors                                                     |

| INIT SEND MSG - Initiator Send Message                              |

| Operational Description                                             |

| Possible Errors                                                     |

| INIT SEND CMD - Initiator Send Command5-29                          |

| Operational Description                                             |

| Possible Errors                                                     |

| INIT XFER PAD - Initiator Transfer Pad                              |

| Operational Description                                             |

| Possible Error                                                      |

| INIT XFER BYTE - Initiator Transfer Byte5-32                        |

| Operational Description                                             |

| Possible Error                                                      |

| INIT CMDC SEQ - Initiator COMMAND COMPLETE/DISCONNECT Sequence      |

| Operational Description                                             |

| Possible Errors                                                     |

| INIT WFR CMD - Initiator Wait for Reselect5-34                      |

| Operational Description                                             |

| Possible Error                                                      |

| INIT WFR SEQ - Initiator Wait for Reselect Sequence5-35             |

| Operational Description                                             |

| Possible Errors 5.35                                                |

| Ta | rrget Command Descriptions,                                                     | 5-37         |

|----|---------------------------------------------------------------------------------|--------------|

|    | TGT SEND MSG - Target Send Message                                              | 5-38         |

|    | Operational Description                                                         | 5-38         |

|    | Possible Error                                                                  | <i>5-</i> 38 |

|    | TGT SEND STAT - Target Send Status                                              | 5-39         |

|    | Operational Description                                                         | 5-39         |

|    | Possible Errors ,                                                               | 5-39         |

|    | TGT DATA MTS - Target Receive Data from Memory Data Bus to SCSI Bus             |              |

|    | Operational Description                                                         | 5-40         |

|    | Possible Errors                                                                 | 5-40         |

|    | TGT DATA PTS - Target Receive Data from MPU to SCSI Bus                         | 5-41         |

|    | Operational Description                                                         | 5-41         |

|    | Possible Errors                                                                 | 5-41         |

|    | TGT REC CMD - Target Receive Command                                            | 5-42         |

|    | Operational Description                                                         | 5-42         |

|    | Possible Errors                                                                 | 5-42         |

|    | TGT REC MSG - Target Receive Message                                            | 5-43         |

|    | Operational Description                                                         | 5-43         |

|    | Possible Errors                                                                 | 5-43         |

|    | TGT DATA STM - Target Receive Data from SCSI Bus to Memor                       | -            |

|    | Data Bus                                                                        |              |

|    | Operational Description                                                         |              |

|    | Possible Errors                                                                 |              |

|    | TGT DATA STP - Target Receive Data from SCSI to MPU Bus Operational Description |              |

|    | Possible Errors                                                                 |              |

|    | TGT CMDC SEQ - Target COMMAND COMPLETE Sequence                                 |              |

|    |                                                                                 |              |

|    | Operational Description                                                         |              |

|    |                                                                                 |              |

|    | TGT XFER BYTE - Target Transfer Byte                                            |              |

|    | Operational Description                                                         |              |

|    | Possible Error                                                                  |              |

|    | TGT DISC CMD - Target Disconnect Command                                        |              |

|    | Operational Description                                                         |              |

|    | TGT DISC SEQ - Target DISCONNECT Sequence                                       | 5-49         |

| Operational Description                       |

|-----------------------------------------------|

| Possible Error                                |

| TGT RCNT SEQ - Target Reconnect Sequence5-50  |

| Operational Description                       |

| Possible Errors                               |

| TGT SEND BSY - Target Send Busy Command       |

| Operational Description                       |

| Possible Errors                               |

| TGT WFS CMD - Target Wait for Select Command  |

| Operational Description                       |

| Possible Error                                |

| TGT WFS SEQ - Target Wait for Select Sequence |

| Operational Description                       |

| Possible Errors                               |

| Appendix A A-1                                |

| Glossary                                      |

F82C5087

# Figures

| Chapter 1: Overview 1-                                    | 1  |

|-----------------------------------------------------------|----|

| Figure 1-1.                                               |    |

| Typical F82C5087 Application                              | -1 |

| Figure 1-2.                                               |    |

| Block Diagram of the F82C5087                             | -2 |

| Figure 1-3.                                               |    |

| An AT Host Adapter System Configuration                   | -5 |

| Figure 1-4.                                               |    |

| SCSI on Motherboard System Configuration                  | -6 |

| Figure 1-5.                                               |    |

| Typical Wide SCSI Bus Configuration                       | -8 |

| Chapter 2: Hardware Specifications 2-                     | -1 |

| Figure 2-1.                                               |    |

| Physical Pin-out of the 80-pin PFP Package                | 2  |

| Figure 2-2.                                               |    |

| 80-pin PFP Package Specification                          | -4 |

| Figure 2-3.                                               |    |

| Functional Pin out of the F82C5087 in Host Adapter Mode 2 | -6 |

| Figure 2-4.                                               |    |

| Clock Timing Characteristics                              | 20 |

| Figure 2-5.                                               |    |

| Write Operation Z8 Mode Timing Characteristics            | 21 |

| Figure 2-6.                                               |    |

| Read Operation Z8 Mode Timing Characteristics             | 22 |

| Figure 2-7.                                               |    |

| Write Operation 8085/8051 Mode Timing Characteristics 2-  | 23 |

| Figure 2-8.                                                        |

|--------------------------------------------------------------------|

| Read Operation 8085/8051 Mode Timing Characteristics 2-24          |

| Figure 2-9.                                                        |

| Write Operation, Non-multiplexed MPU Timing Characteristics 2-25   |

| Figure 2-10.                                                       |

| Read Operation, Non-multiplexed MPU Timing Characteristics . 2-26  |

| Figure 2-11.                                                       |

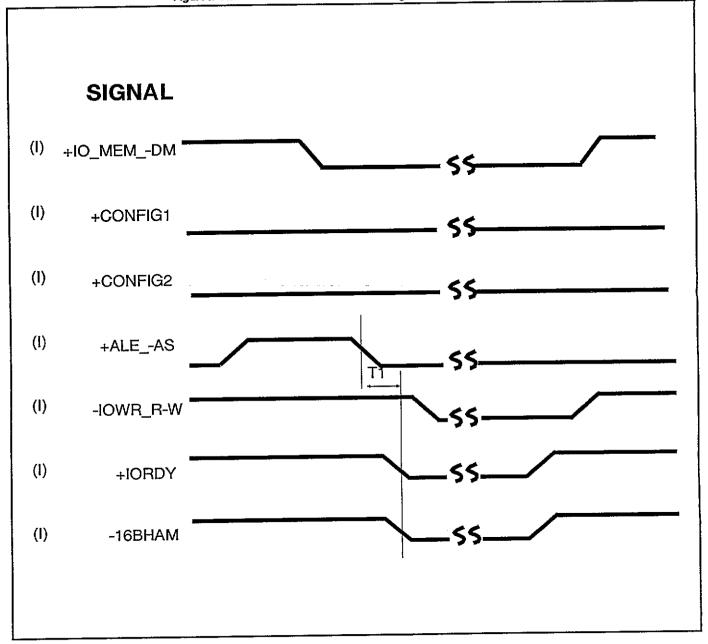

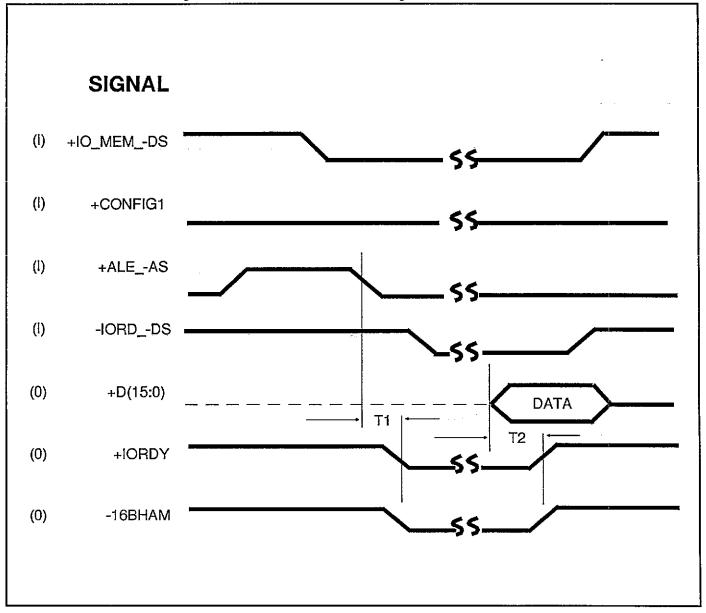

| MPU Write IORDY Timing Characteristics 2-28                        |

| Figure 2-12.                                                       |

| MPU Read IORDY Timing Characteristics 2-29                         |

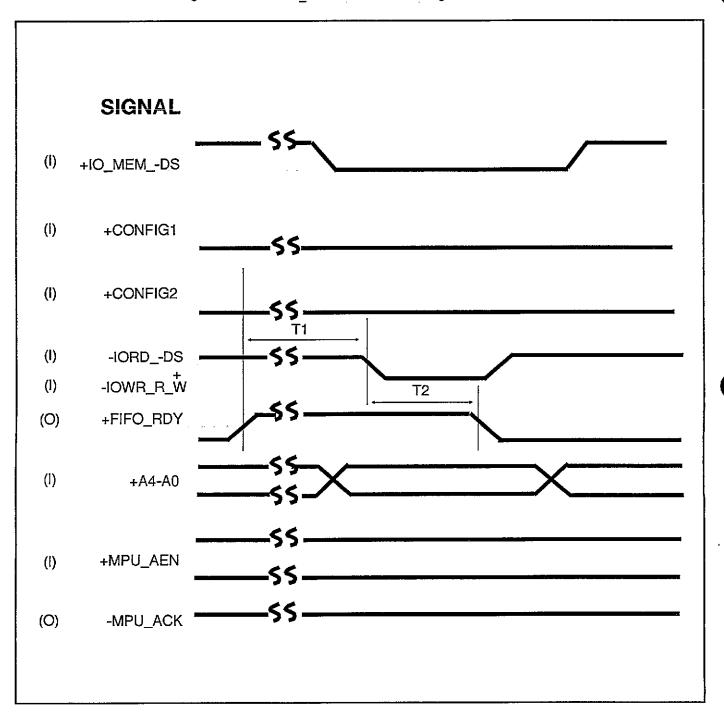

| Figure 2-13.                                                       |

| FIFO_RDY with Address Timing Characteristics 2-30                  |

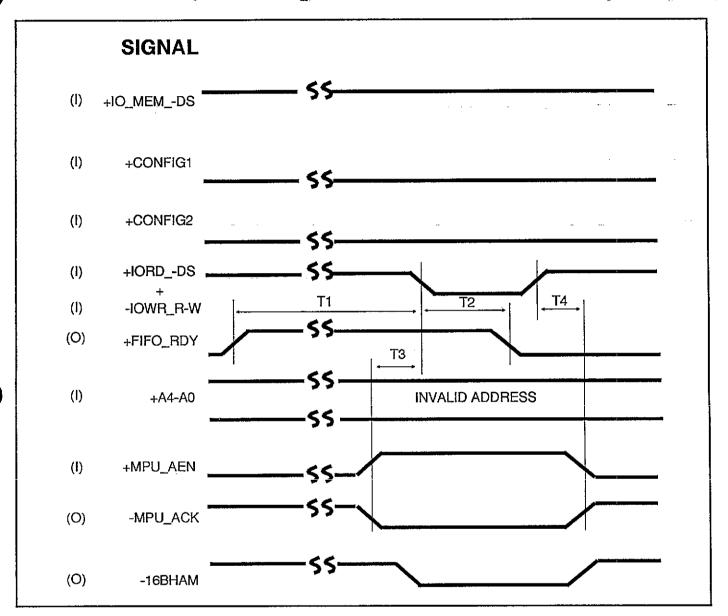

| Figure 2-14.                                                       |

| FIFO_RDY without Address Timing Characteristics 2-31               |

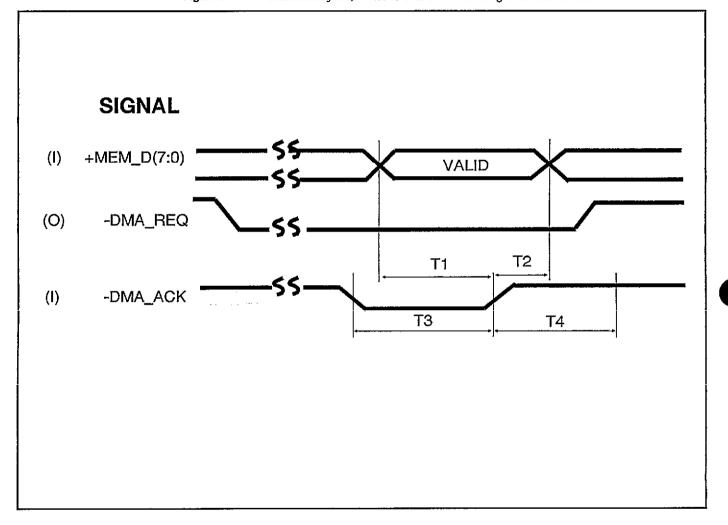

| Figure 2-15.                                                       |

| DMA Interface, Write to F82C5087 Timing Characteristics 2-32       |

| Figure 2-16.                                                       |

| DMA Interface, Read from F82C5087 Timing Characteristics 2-33      |

| Figure 2-17.                                                       |

| SCSI Arbitration Timing Characteristics 2-34                       |

| Figure 2-18.                                                       |

| SCSI Select/Reselect Timing Characteristics 2-35                   |

| Figure 2-19.                                                       |

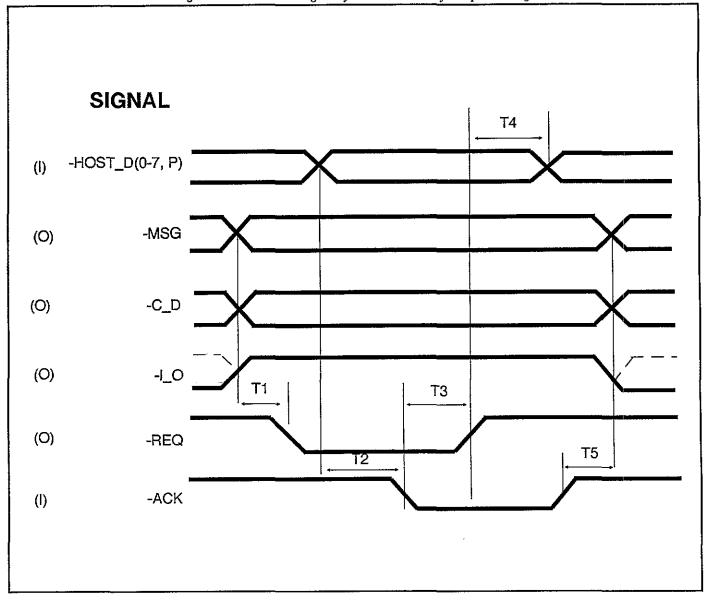

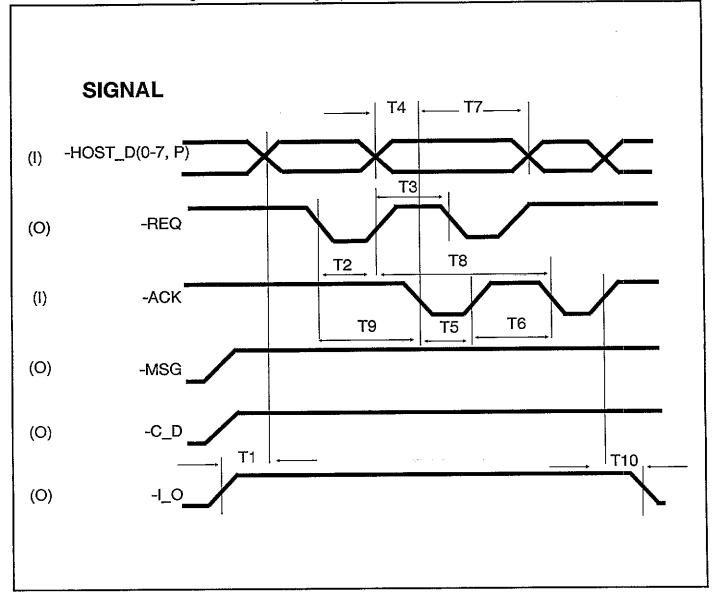

| SCSI Target Asynchronous Transfer Output Timing Characteristics    |

| Figure 2-20.                                                       |

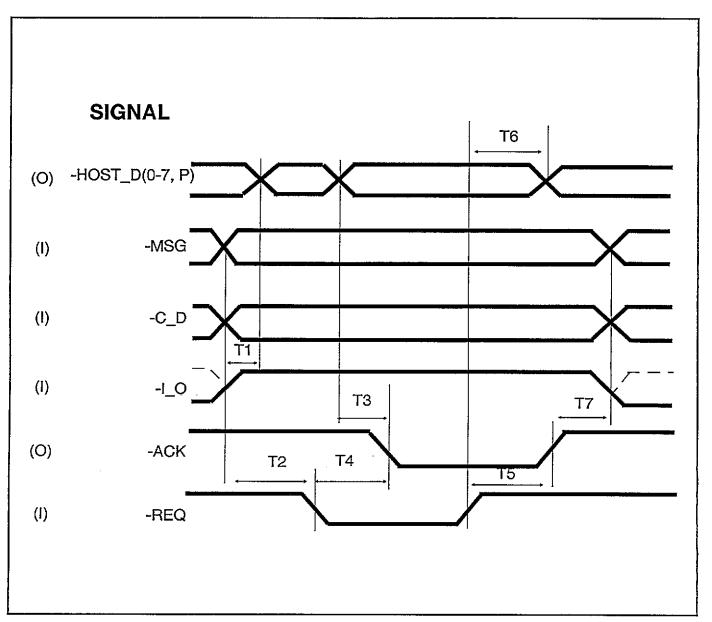

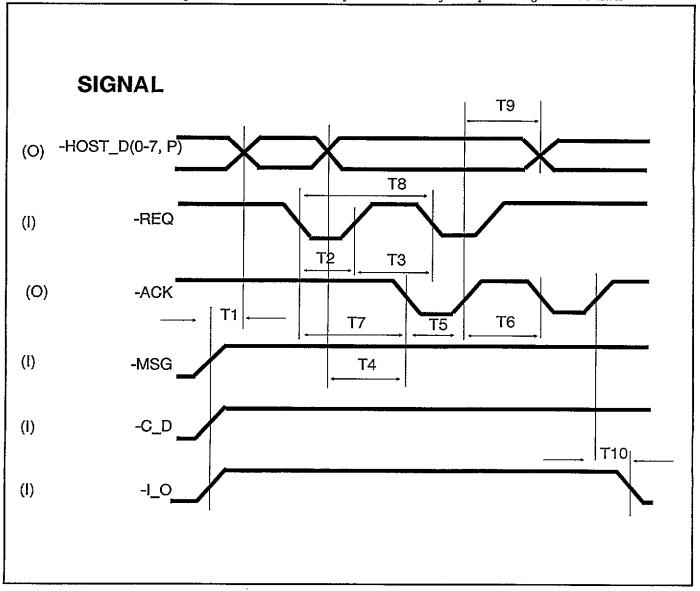

| SCSI Target Asynchronous Transfer Input Timing Characteristics     |

| Figure 2-21.                                                       |

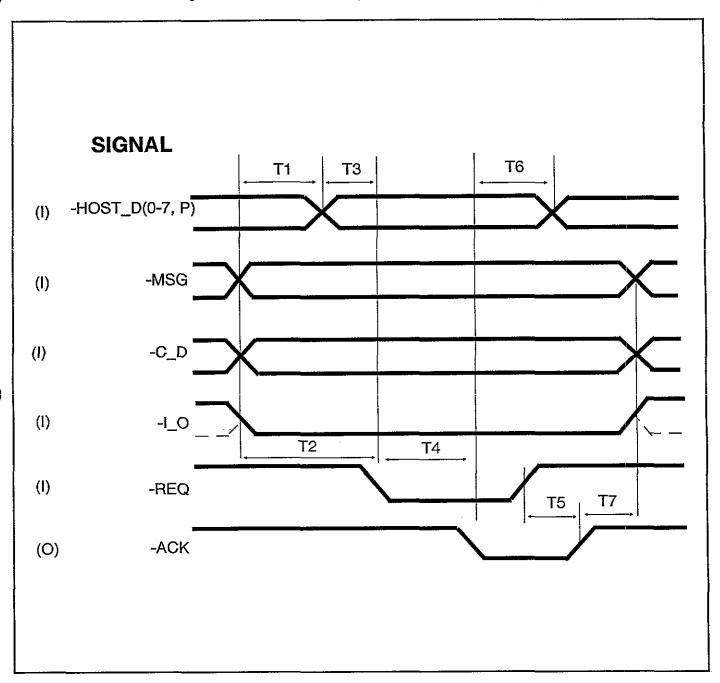

| SCSI Initiator Asynchronous Transfer Output Timing Characteristics |

| Figure 2-22.                                                       |

| SCSI Initiator Asynchronous Transfer Input Timing Characteristics  |

| Figure 2-23.                                                       |

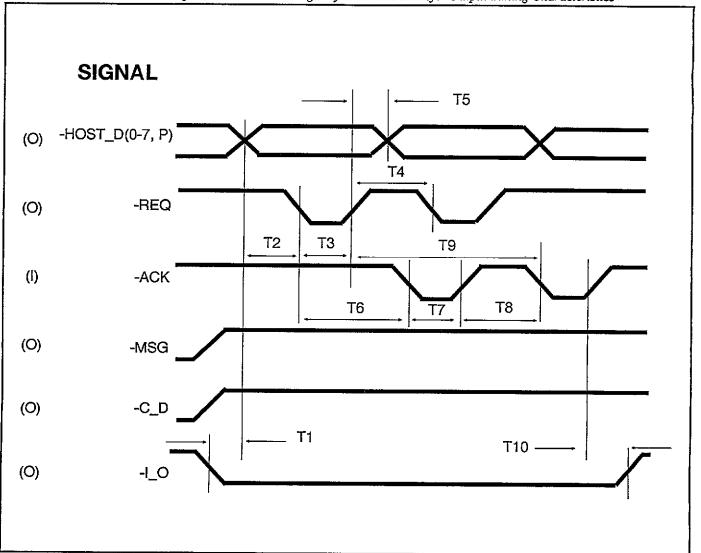

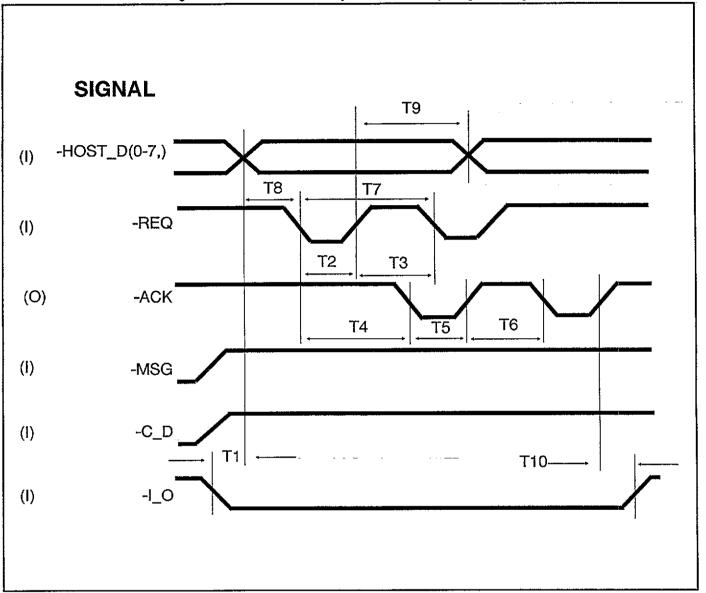

| SCSI Target Synchronous Transfer Output Timing Characteristics     |

| Figure 2-24.                                                      | -            |

|-------------------------------------------------------------------|--------------|

| SCSI Target Synchronous Transfer Input Timing Characteristics     |              |

| Figure 2-25.                                                      |              |

| SCSI Initiator Synchronous Transfer Output Timing Characteristics | <u>.</u><br> |

| Figure 2-26.                                                      | •            |

| SCSI Initiator Synchronous Transfer Input Timing Characteristics  | 2-43         |

| Chapter 3: Operation                                              | 3-1          |

| Figure 3-1.                                                       |              |

| Functional Pin out of Cascaded 5087s                              | 3-4          |

| Figure 3-2.                                                       | <u> </u>     |

| Conceptual Diagram of the F82C5087's Memory                       | 3-9          |

| Figure 3-3.                                                       |              |

| F82C5087's Command Queueing                                       |              |

| Appendix A                                                        | - A-1        |

| Figure A-1.                                                       |              |

| Asynchronous Data Transfer Flow Chart                             | Δ-2          |

| Chapter 1: Overview                         | 1-1  |

|---------------------------------------------|------|

| Table 1-1.                                  |      |

| F82C5087 Command Set                        | 1-9  |

| Table 1-1.                                  |      |

| F82C5087 Command Set (continued)            | 1-10 |

| Chapter 2: Hardware Specifications          | 2-1  |

| Table 2-1.                                  |      |

| A Pin List of the 80-pin Package            | 2-3  |

| <b>Table 2-2.</b>                           |      |

| Input/Output Signals                        | 2-9  |

| Table 2-3.                                  | -    |

| Signals Specific to 8085/8051 Mode          | 2-16 |

| Table 2-4.                                  | •    |

| Signals Specific to Z8 Mode                 |      |

| <b>Table 2-5.</b>                           |      |

| Signals Specific to Wide Data Bus Transfers | 2-18 |

| Table 2-6.                                  |      |

| Pad Drive Capacity                          | 2-19 |

| Chapter 3: Operation                        | 3-1  |

| Table 3-1.                                  |      |

| Mode Control Register Setting               | 3-5  |

| Table 3-2.                                  |      |

| Master/Slave Mode                           | 3_5  |

| Chapter 4: Registers                          | 4-1   |

|-----------------------------------------------|-------|

| Table 4-1.                                    |       |

| Addressing the F82C5087 Registers             | . 4-1 |

| Table 4-1.                                    |       |

| Addressing the F82C5087 Registers (continued) | . 4-2 |

| Chapter 5: Commands                           | 5-1   |

| Table 5-1.                                    |       |

| F82C5087 Control Commands                     | . 5-4 |

| Table 5-2.                                    |       |

| Initiator Commands                            | 5-17  |

| Table 5-3.                                    |       |

| Command Length Codes                          | 5-29  |

| Table 5-4.                                    |       |

| F82C5087 Target Commands                      | 5-37  |

#### Introduction

The CHIPS F82C5087 SCSI controller provides all the functions needed to implement the SCSI interface on a host computer or a device controller. The chip provides an I/O interface to the SCSI bus and to the other system components (e.g., buffer memory, the on-board microprocessor (MPU), and the host computer).

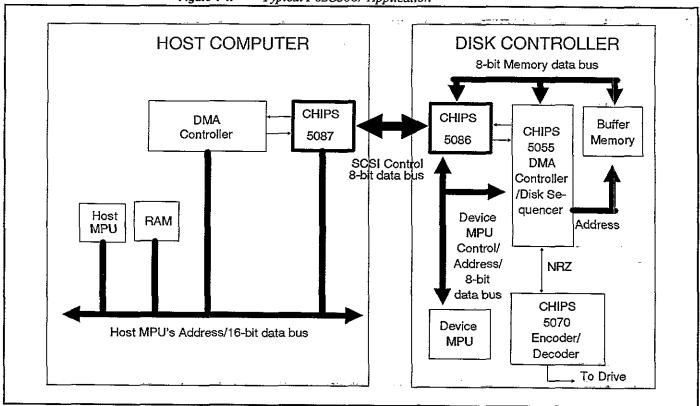

Used as a host adapter, the F82C5087 functions as a bridge between the host computer bus and the SCSI bus. In this application, the F82C5087 connects an 8- or 16-bit host computer data bus to an 8-bit SCSI data bus. The F82C5087 interfaces such peripheral equipment as a Winchester drive to the SCSI bus. Refer to Figure 1-1 for an illustration of these two applications. For more details on F82C5087 applications refer to the section "Typical Applications."

Figure 1-1. Typical F82C5087 Application

The F82C5087's hardware and firmware make it a flexible, as well as a powerful chip. It is available in an 80-pin flat pack, and can be purchased with or without firmware, standalone, or as part of a host adapter board provided as a Turnkey Manufacturing Package (MK5087 SCSI Host Adapter for PC/AT).

### Hardware Features

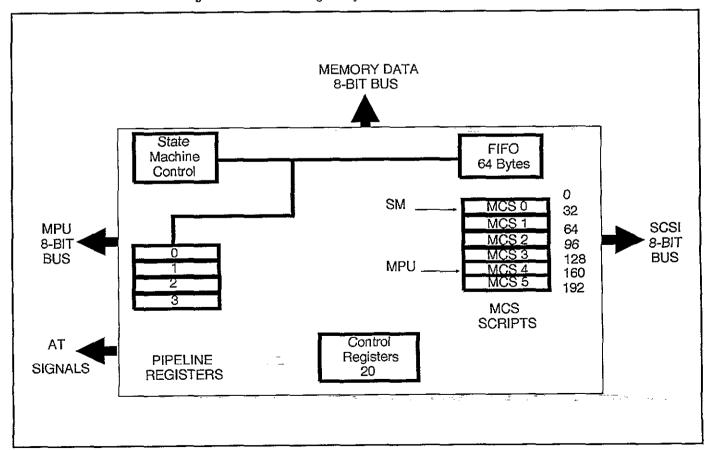

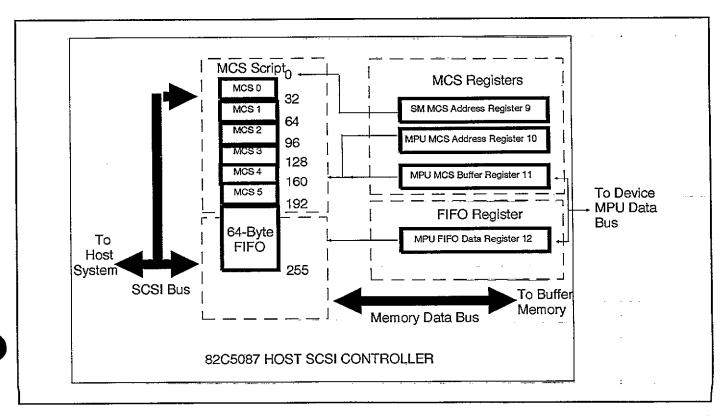

The F82C5087's memory structure consists of 64 bytes of FIFO and six individual 32-byte Message/Command Space (MCS) scripts. The large FIFO buffer is used to store all the data transferred between the MPU's bus, the memory data bus or the SCSI bus. This increases system throughput by smoothing out the system's data transfers.

The MCS is a valuable tool for tailoring the F82C5087 to the needs of particular applications. It can be used to store blocks of frequently used commands, messages, and status. For instance, if the F82C5087 is used as a host adapter operating as an initiator in a system configuration with an 80286 host MPU, the firmware might decide to use the MCS to store messages frequently sent by the initiator. This improves system performance because the information can be accessed as a block, and does not have to be retrieved from system memory. Because the F82C5087 provides two MCS address pointers the MPU can be processing one MCS segment, while the F82C5087 state machine (SM) is simultaneously processing another 32-byte MCS segment. Figure 1-2 shows a simplified block diagram of the chip's functions.

Figure 1-2. Block Diagram of the F82C5087

The F82C5087's 24 registers provide a means to control the F82C5087's internal operation, and to gain status on the F82C5087's operation. The F82C5087's first four registers, the command pipeline registers, in conjunction with the MCS, enable up to four F82C5087 commands to be queued.

The F82C5087 hardware has an internal state machine that manages the system flow of SCSI information. Because the F82C5087 hardware is managing this lower-level task, the firmware is free to manage such higher-level system activities as task scheduling and resource allocation.

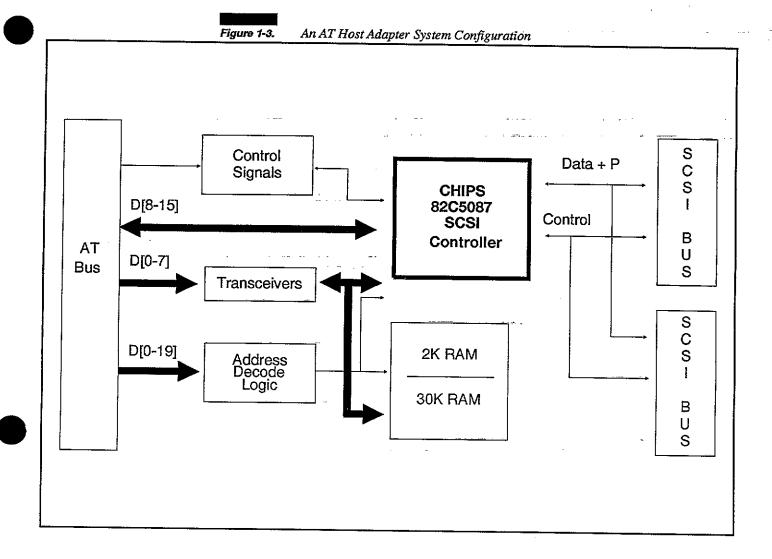

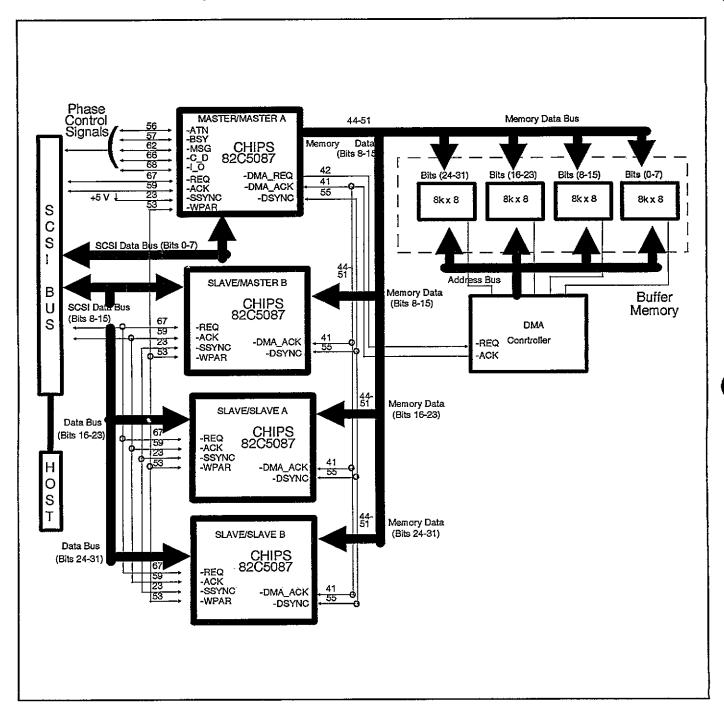

The F82C5087's bus structure increases system performance and provides system design flexibility. The F82C5087 supports an 8-bit MPU data bus, an 8-bit SCSI bus, and an 8-bit high-speed memory data bus. This separate high-speed data bus increases system throughput by enabling data and control activities to be independent. The F82C5087's bus structure also adds to the chip's versatility. For instance, the bandwidth of the SCSI bus and the memory data bus can be extended from 8 to 16 or 32 bits by cascading F82C5087s. The F82C5087 also supports the option of extending the MPU data bus to 16 bits by using the memory data bus as the MPU's upper data bus. Figure 1-3 shows a F82C5087 host adapter supporting 16-bit MPU data transfers. For more information on cascading F82C5087s refer to the section "Master or Slave Mode."

The F82C5087 supports two user-controlled power management features making it ideal for notebook, palmtop and laptop applications. The sleep mode registers allows the clock input to the chip to be turned off. Termination power resistors to the SCSI connector can be switched on or off through a pin on the F82C5087.

Other F82C5087 hardware features include a power-on flag, and input pins that support jumper-selectable options that reduce on-board circuitry.

Because the F82C5087 is built using proven CMOS low-power technology it requires only a single +5 Volt supply.

Such firmware features as an extensive command set provide firmware engineers with a high degree of control over the F82C5087's operation. The F82C5087's large set of 46 commands enables firmware engineers to exercise a great deal of control over the SCSI bus activities, and to manage the system flow of SCSI information. These commands perform such simple tasks as transferring a byte from the SCSI bus into the MCS, or such series of tasks as receiving a command complete sequence from the SCSI bus, and transferring it into the MCS. Certain control commands can be used to establish a data path between the MPU's data bus, the memory data bus, and the SCSI bus.

One of the F82C5087's main firmware features is command queuing which reduces command overhead. The F82C5087 enables up to four F82C5087 commands to be queued in the pipeline registers. These commands can enable the F82C5087 to sequence through several SCSI bus phases without firmware intervention. For example, the F82C5087 command can handle a complete SCSI command sequence from disconnect, to connect, and to bus free. For more details refer to the section "Command Queuing".

## Firmware Features

The F82C5087's set of 24 registers provide maximum programming flexibility because registers record the status of all commands executed, and keep records of previous executions. This facilitates the monitoring of command flow, and error recovery.

Another important feature is the F82C5087's support of programmable conditions for interrupt generation. This enables the firmware to dictate the conditions under which an interrupt should be generated to the on-board MPU. This is useful because the conditions for interrupt generation will vary depending on the amount of firmware control desired, and whether the F82C5087 is used as an initiator or a target. Thus, the firmware can tailor the conditions for interrupt generation to fit their particular applications.

## Typical Applications

The F82C5087 can be designed into a system as a host adapter or can provide the SCSI host function on a PC-AT motherboard. It provides system design flexibility. For instance, as well as supporting the option of cascading, the F82C5087 provides two different ways of wiring the F82C5087 to support data transfers to/from system memory. The F82C5087's FIFO\_RDY pin can be connected to a DMA controller on the system's memory data bus, or it can be connected to the F82C5087's IORDY pin to the MPU's wait state generator to support burst transfers (string operation) from the MPU to the F82C5087.

### Host Adapter

Used as a host adapter, the F82C5087 functions as a bridge between the PC-AT host computer bus and the SCSI bus. The 8-bit bidirectional MPU address/data bus and its associated control signals connect the F82C5087 to the host computer's MPU. The F82C5087 uses the SCSI control bus, comprised of nine F82C5087 control signals, as a path to the SCSI bus. For 16-bit host computer MPU's, the 8-bit memory data bus is used to transfer the high byte. Figure 1-3 shows a configuration in which the F82C5087 is used as a host adapter.

Typically, the host computer requires such information as status or data from the devices connected to the SCSI bus. The host adapter queues up these requests, and sends them to the appropriate device(s) via the SCSI bus. The host adapter enables SCSI peripheral devices to communicate with such host systems as an IBM PC AT that do not directly support the SCSI interface. In host adapter mode, the MPU data bus can be extended up to 16 bits; the memory data bus functions as the MPU's upper data bus. In this mode, the F82C5087 performs byte to word packing and unpacking. It provides 24 mA drive capability for direct interface to a PC-AT bus.

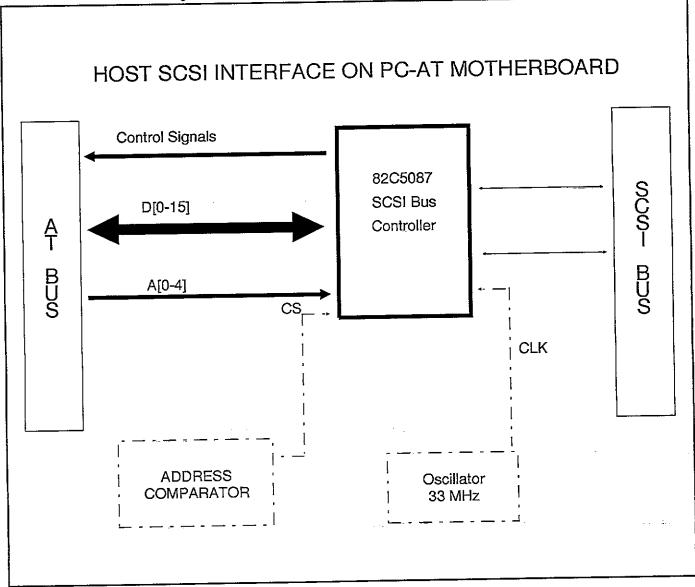

#### Motherboard

The F82C5087 can be used to implement a SCSI port on a PC-AT motherboard. It requires only the termination resistors and connector, besides the chip, to provide an optimized SCSI host solution. The F82C5087 has two useful power management, sleep mode and termination power disable, that make it ideal for laptop and notebook environments. Figure 1-4 shows such a configuration.

Figure 1-4.

SCSI on Motherboard System Configuration

## Operational Modes

The F82C5087 offers application flexibility because of the wide range of operational modes it supports. The F82C5087 supports the SCSI bus initiator or target mode, asynchronous or synchronous transfer mode, and master or slave mode (wide SCSI).

## Initiator or Target Mode

Systems can be configured with single or multiple initiators and targets. Typically, the initiator is the host adapter responsible for originating the operation. The F82C5087 initiator arbitrates for the SCSI bus, selects the target device, and sends it a stored multi-byte SCSI command from the MCS.

A F82C5087 operating in target mode saves the initiator's device ID, receives the multi-byte command, sends a DISCONNECT message or terminates the sequence, then switches to the BUS FREE phase.

#### Non-Differential Mode

SCSI bus signals transmitted between initiators and targets can be single-ended or differential. The SCSI interface controller must operate in non-differential mode if single-ended drivers/receivers are used. The F82C5087 supports on-board 48 mA drivers for the single-ended SCSI bus. A six meter cable is the maximum supported in non-differential mode. The F82C5087 does not support a differential SCSI bus.

### Asynchronous or Synchronous Mode

The F82C5087 supports both asynchronous and synchronous data transfers over the SCSI bus. For high-performance systems, the F82C5087 device can operate in synchronous mode to support higher transfer rates.

In asynchronous and synchronous transfer mode, one byte of information is transferred over the SCSI bus with each REQ/ACK handshake. The F82C5087's large, internal FIFO acts as a buffer that evens out data transfers between the SCSI bus and buffer memory to support transfers at 4 and 5.3 megabytes/second. For systems with sustained transfers this buffering can increase system performance. Three of the F82C5087's internal registers, Registers 16-18, provide two 24-bit transfer counters that track data transferred to/from the FIFO.

When the F82C5087 is operating in synchronous mode, a transfer rate and an offset must be specified. The F82C5087's clock rate of 33 MHz, results in the F82C5087's unbeatable synchronous transfer rate of 5.3 megabytes/second. The maximum offset is 63 bytes.

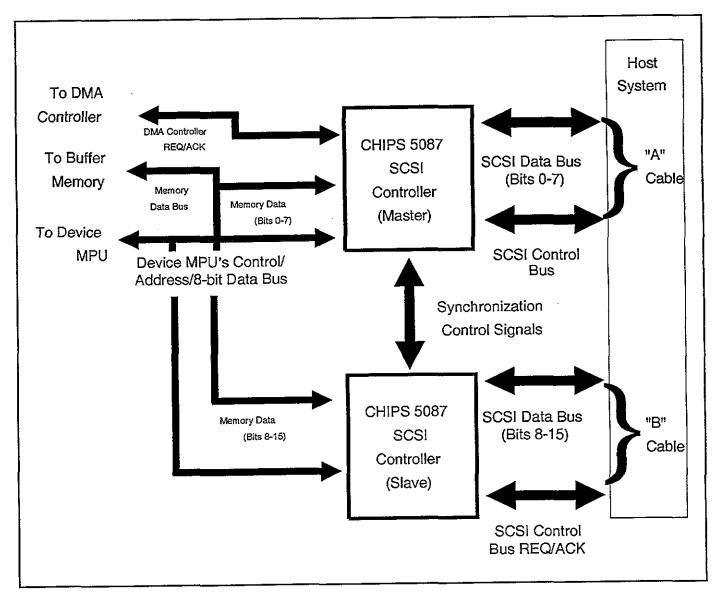

#### Master or Slave Mode

To extend the bandwidth of the SCSI bus and the memory data bus, the F82C5087 can be cascaded. Refer to Figure 1-5. Cascading is supported by the F82C5087's ability to operate in master or slave mode. Through the Mode Control Register, the F82C5087 can be configured as a master or slave chip for its main operational mode (e.g., performing such basic operations as transferring data to/from buffer memory), and for its SCSI bus operational mode. In slave mode, the F82C5087 is under the control of the F82C5087 master chip. For instance, the master F82C5087 is responsible for synchronizing the slaves' transfer of data.

Figure 1-5. Typical Wide SCSI Bus Configuration

### System Interface

The F82C5087 contains functional blocks that support these operational modes (e.g., master/slave, synchronous/asynchronous). These blocks provide the logic necessary for the F82C5087 to interface with the other system components, and to manage the flow of SCSI information through the system. They can be grouped into three categories: the I/O interface, the set of F82C5087 commands, and the memory structure.

#### I/O Interface

It is through its I/O interface that the F82C5087 is able to send/receive signals, addresses, and data to/from the system's other components. This interface

enables the F82C5087 to interface to the buffer memory, the on-board MPU, and the SCSI bus.

#### **Command Set**

Through its set of commands, the F82C5087 provides the SCSI protocol for the system flow of command, data, message and status, and allows the firmware to transfer data between the MPU and memory data bus. These commands are arranged in control, initiator, and target groups. Refer to Table 1-1.

Table 1-1.

| F82C5087 Comma    | nd <u>Set</u>                                                 |                |                                                                                  |

|-------------------|---------------------------------------------------------------|----------------|----------------------------------------------------------------------------------|

| Command           | Function                                                      | Command        | Function                                                                         |

| CONTROL COMMAN    | IDS                                                           |                |                                                                                  |

| CNTL NOP<br>FIFO. | No Operation                                                  | CNTL RST FIFO  | Reset 5087 data                                                                  |

| CNTL RST ON       | Assert reset signal to SCSI bus.                              | CNTL RST OFF   | Deassert reset signal to SCSI bus.                                               |

| CNTL ATN ON       | Assert ATN signal to SCSI bus.                                | CNTL ATN OFF   | Deassert ATN signal to SCSI bus.                                                 |

| CNTL ENB SEL      | Enable selection.                                             | CNTL DIS SEL   | Disable selection.                                                               |

| CNTL ENB RESEL    | Enable reselection.                                           | CNTL DIS RESEL | Disable reselection.                                                             |

| CNTL ENB ADV      | Enable MCS auto advance.                                      | CNTL DIS ADV   | Disable MCS auto advance.                                                        |

| CNTL DATA PTM     | Receive MPU data<br>and send it to the<br>memory data bus.    | CNTL DATA MTP  | Receive data from<br>the memory data<br>bus and send it to<br>MPU.               |

| INITIATOR COMMAN  | IDS                                                           |                |                                                                                  |

| INIT SWOA SEQ     | Select target without attention sequence.                     | INIT SWA SEQ   | Select target with attention sequence.                                           |

| INIT SWOA CMD     | Select target without attention.                              | INIT SWA CMD   | Select target with attention.                                                    |

| INIT REC INFO     | Receive information.                                          | INIT DATA MTS  | Receive data from the<br>memory data bus and<br>send it to the SCSI<br>data bus. |

| INIT DATA PTS     | Receive data from<br>MPU and send it to<br>the SCSI data bus. | INIT DATA STM  | Receive data from<br>SCSI bus and send<br>it to the memory<br>data bus.          |

| INIT DATA STP     | Receive data from SCSI bus and send it to MPU's data bus.     | INIT SEND MSG  | Send message                                                                     |

| INIT SEND CMD     | Send multi-byte command.                                      | INIT XFER PAD  | Transfer filler data.                                                            |

| INIT XFER BYTE    | Transfer byte.                                                | INIT CMDC SEQ  | Perform COMMAND<br>COMPLETE/DIS-<br>CONNECT sequence                             |

| INIT WFR CMD      | Wait for reselect phase.                                      | INIT WFR SEQ   | Wait to be<br>reselected, then<br>reconnect.                                     |

Table 1-1.

F82C5087 Command Set (continued)

| TARGET COMMAND | os                                                               |               |                                                                 |

|----------------|------------------------------------------------------------------|---------------|-----------------------------------------------------------------|

| TGT SEND MSG   | Send message.                                                    | TGT SEND STAT | Send status to the initiator.                                   |

| TGT DATA MTS   | Receive data from<br>memory data bus and<br>send it to SCSI bus. | TGT DATA PTS  | Receive data from MPU bus and send it to the SCSI bus.          |

| TGT REC CMD    | Receive a multi-byte command.                                    | TGT REC MSG   | Receive a single-<br>byte or multi-byte<br>message.             |

| TGT DATA STM   | Receive data from<br>SCSI bus and send it<br>to memory data bus. | TGT DATA STP  | Receive data from<br>SCSI bus and send<br>it to MPU's data bus. |

| TGT CMDC SEQ   | Perform COMMAND COMPLETE sequence.                               | TGT XFER BYTE | Transfer byte.                                                  |

| TGT DISC CMD   | Disconnect from the SCSI bus.                                    | TGT DISC SEQ  | Perform DISCONNECT sequence.                                    |

| TGT RCNT SEQ   | Perform<br>RECONNECT<br>sequence.                                | TGT SEND BSY  | Wait for select, then<br>send busy response<br>and disconnect.  |

| TGT WFS CMD    | Wait for select.                                                 | TGT WFS SEQ   | Perform Wait for Select sequence.                               |

## **Memory Structure**

The first segment of F82C5087 memory, the 64-byte FIFO, is used in SCSI bus data transfers, and in data transfers between the MPU's data bus and the memory data bus. The second segment, the MCS, stores SCSI sequences and supports the F82C5087's command queuing capability.

## Performance Specifications

When the F82C5087 is operating in synchronous mode, a transfer rate of 5.3 megabytes/second at a clock rate of 33 MHz is supported. The transfer rate in asynchronous mode is 4 megabytes/second (over a 20 foot cable length). Command overhead is 25 microseconds.

This chapter is directed at hardware engineers intending to design the F82C5087 SCSI-bus interface controller into their systems. Physical and functional pin specifications, signal descriptions, timing specifications, and electrical specifications are provided.

## Physical Specifications

The F82C5087 device is available in a 80-pin PFP package. It supports the following functions:

- Asynchronous SCSI data transfers

- Synchronous, as well as faster asynchronous data transfers, are supported.

The asynchronous transfer rate with the F82C5087 is 4 megabytes per second. Synchronous data transfer rates at 5.3 megabytes per second are supported by the F82C5087.

- The F82C5087 has on-chip memory that enables up to four F82C5087 commands to be queued.

- The F82C5087 provides 64 bytes of data FIFO to even out data transfers and to increase system performance.

- The F82C5087 command set, which is comprised of 46 commands, performs the SCSI protocol for command, data, message and status flow.

This enables the firmware to manage system level activities.

- Supports non-differential, SCSI interface with 48 mA drive capability.

- Connection to MPUs that have non-multiplexed address/data buses, as well as connection to multiplexed MPUs

- Support of wide SCSI and wide memory data bus transfers of 16 or 32 bits, as well as 8-bit data transfers.

- AT host SCSI support through the following signals: -16BHAM,

-MPU\_ACK, and -MPU\_AEN.

### **Pin Descriptions**

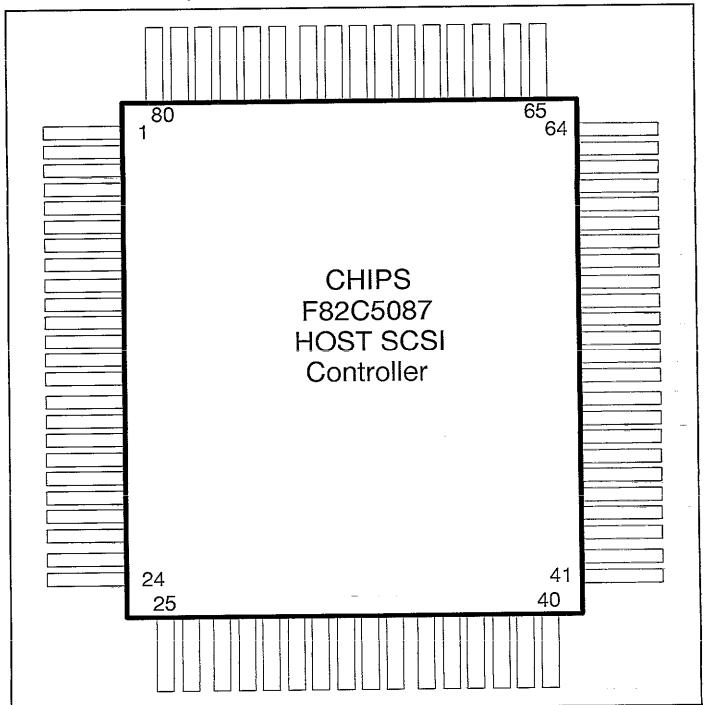

Refer to Figure 2-1 for a physical pin out of the 80-pin package. Table 2-1 provides a pin list for the 80-pin package. Note an active low polarity is indicated by a minus sign (-) prefix; a plus sign (+) prefix indicates high polarity. For information on this package's pin functions refer to the "Functional Chip Specifications" section later in this chapter.

Figure 2-1. Physical Pin-out of the 80-pin PFP Package

Table 2-1.

| A Pin List of the 80-pin Package |             |      |               |                  |              |  |

|----------------------------------|-------------|------|---------------|------------------|--------------|--|

| Pin<br>Number                    | Pin<br>Name | 1/0  | Pin<br>Number | Pin<br>Name      | ľO           |  |

| 1                                | +INTERRUPT  | 0    | 41            | -16BHAM          | 0            |  |

| 2                                | MPU_AEN     | I    | 42            | +INP1[3]/TERMPWR | Ī/O          |  |

| 3                                | -MPU_ACK    | I    | 43            | +INP1[4]         | I/O          |  |

| 4                                | -XOR[7](A2) | I    | 44            | +BUF_IN          | Ī            |  |

| 5                                | -XOR[6](A1) | Ĭ    | 45            | +IORDY           | <del>_</del> |  |

| 6                                | -XOR[5](A0) | I    | 46            | +FIFO_RDY        | 0            |  |

| 7                                | +CONFIG1    | I    | 47            | +A3              | Ĭ            |  |

| 8                                | +IO-MEMDM   | I    | 48            | -DMA_ACK         | Ţ            |  |

| 9                                | -IORDDS     | I    | 49            | -DMA_REQ         | 0            |  |

| 10                               | -IOWR_R-W   | I    | 50            | GND_2            | I            |  |

| 11                               | +ALEAS      | I    | _ 51          | +MEM_D[0]        | I/O          |  |

| 12                               | GND_0       | Ĭ    | 52            | +MEM_D[1]        | 1/0          |  |

| 13                               | +A_D[0]     | I/O  | 53            | +MEM_D[2]        | I/O          |  |

| 14                               | +A_D[1]     | I/O  | 54            | +MEM_D[3]        | 1/0          |  |

| 15                               | +A_D[2]     | I/O  | 55            | VDD_2            | Ī            |  |

| 16                               | +A_D[3]     | I/O  | 56            | +MEM_D[4]        | 1/0          |  |

| 17                               | VDD_0       | I    | .57           | +MEM_D[5]        | Ī/O          |  |

| 18                               | +A_D[4]     | I/O  | 58            | +MEM_D[6]        | 1/0          |  |

| 19                               | +A_D[5]     | I/O  | 59            | +MEM_D[7]        | I/O          |  |

| 20                               | +A_D[6]     | I/O  | 60            | GND_3            | Ī            |  |

| 21                               | +A_D[7]     | I/O  | - 61          | +CONFIG2         | I            |  |

| 22                               | GND_1       | I    | 62            | -WPAR            | <u> I/O</u>  |  |

| 23                               | -HOST_D_P   | I/O  | 63            | -DSYNC           | Ī/O          |  |

| 24                               | HOST_D[7]   | I/O  | 64            | -ATN             | ľÖ           |  |

| 25                               | DRV_GND_0   | 1    | 65            | -BSY             | I/O          |  |

| 26                               | -HOST_D[6]  | I/O  | 66            | DRV_GND_3        | <u> </u>     |  |

| 27                               | -HOST_D[5]  | I/O_ | 67            | -ACK             | Ī/Ô          |  |

| 28                               | -HOST_D[4]  | I/O  | 68            | -RESET_IN        | I/O          |  |

| 29                               | -HOST_D[3]  | I/O  | 69            | VDD_3            | I            |  |

|                                  | DRV_GND_1   | I    | 70            | -MSG             | I/Ô          |  |

|                                  | -HOST_D[2]  | I/O  | 71            | -SEL             | ΪΌ           |  |

|                                  | -SSYNC      | I/O  | 72            | DRV_GND_4        | I            |  |

|                                  | -HOST_D[1]  | I/O  | 73            | +A4              | Ī            |  |

| 34                               | VDD_1       | I    | 74            | -C_D             | J/O          |  |

| 35                               | -HOST_D[0]  | I/O  | 75            | -REQ             | I/O          |  |

|                                  | +BUF_OUT    | 0    | 76            | -I_O             | I/O          |  |

|                                  | DRV_GND_2   | I    | 77            | -RESET_CAP       | Ī            |  |

|                                  | +INP1[0]    | I    | 78            | DRV_GND_5        | Ī            |  |

|                                  | +INP1[1]    | I    | 79            | -RESET_OUT       | 0            |  |

| 40                               | +INP1[2]    | I    | 80            | +CLOCK           | I            |  |

|                                  |             |      |               |                  |              |  |

Note: +INP1[3] could be also configured as the terminator power control through Register 25, bit 1.

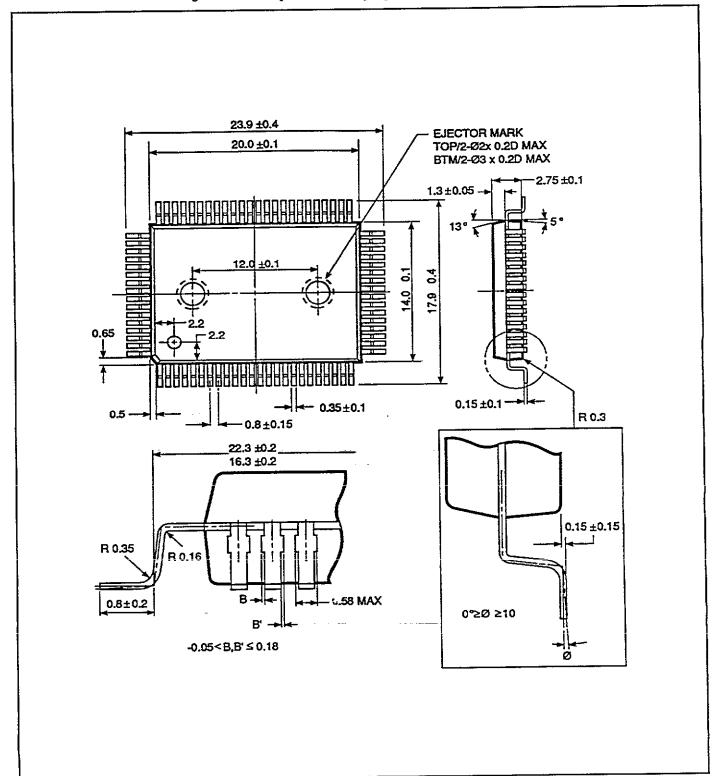

## **Package Specifications**

Figure 2-2 provides a diagram of the package specifications for the 80-pin PFP package.

Figure 2-2.

80-pin PFP Package Specification

# Functional Chip Specifications

The F82C5087 can be used as a host adapter or a device controller. When used as a host adapter, the F82C5087 connects an 8- or 16-bit, host computer data bus to an 8-bit SCSI data bus. As a device controller, the F82C5087 interfaces such peripheral equipment as a Winchester drive to the SCSI bus, and provides a data path between the MPU and memory data buses.

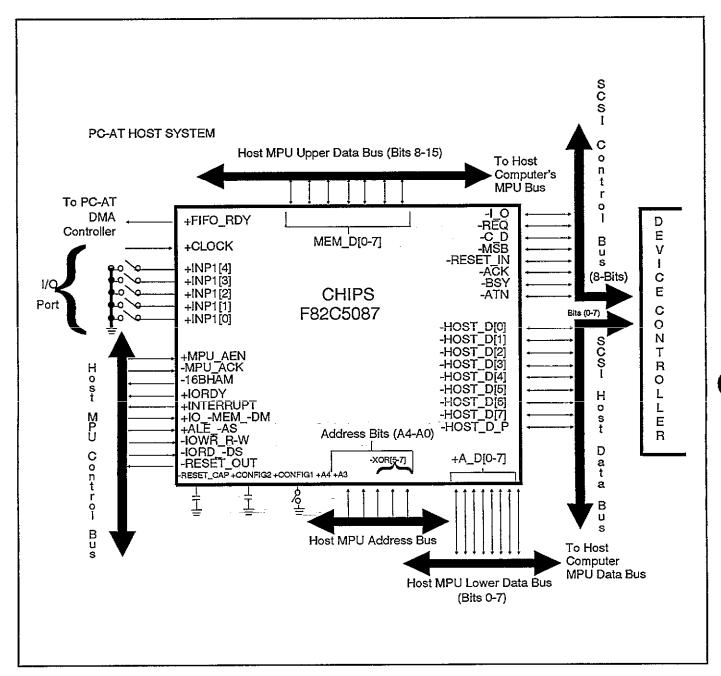

It is through its I/O interface, that the F82C5087 controller can receive/send signals, addresses, and data from/to the system's other components (e.g., DMA controller, MPU). Refer to the following two sections for annotated illustrations of the F82C5087 host adapter.

### Functionality of the F82C5087 Host Adapter

As a host adapter, the F82C5087 functions as a bridge between the host computer bus and the SCSI bus. Typically, the host computer requires information (e.g., status) and/or data from the devices connected to the SCSI bus. The F82C5087 host adapter can queue up these requests and send them to the appropriate device(s) via the SCSI bus. Consequently, a host adapter enables SCSI peripheral devices to communicate with host systems that do not directly support the SCSI interface (e.g., IBM PC AT).

For specifically the AT bus, and to use the DMA on board the AT system, the F82C5087 offers a more optimized host adapter solution. However, the F82C5087 can be used in a host adapter application with a bus master chip and/or bus interface chip for VME, MULTIBUS, MICROCHANNEL, NUBUS, etc.

Refer to Figure 2-3 for a functional pin out of a F82C5087 in an AT host adapter. The F82C5087 host adapter is configured for the following system: (1) the system is operating with 16 bits of MPU data and has an Intel 80286 with a non-multiplexed address/data bus; the bus has been de-multiplexed, and (2) the system has an 8-bit wide SCSI data bus.

As illustrated, the F82C5087 host adapter provides an interface with the following system components:

- SCSI control bus

- SCSI data bus

- Host computer's MPU address/control/data bus

- Host computer's DMA controller.

Figure 2-3. Functional Pin out of the F82C5087 in Host Adapter Mode

## Interfacing with the SCSI Control Bus

The SCSI control bus consists of nine bidirectional lines. Firmware can control these SCSI bus control signals (e.g., -BSY and -ATN) by means of the F82C5087 command set. For example, by issuing the CNTL ATN ON (Control Attention On) pipeline command, firmware can assert the -ATN signal on the SCSI bus. By reading the contents of certain F82C5087 internal registers, firmware can monitor the activities and contents of the SCSI bus.

## Interfacing with the SCSI Data Bus

SCSI data bus signals enable the F82C5087 host adapter to handle the device controller's requests for information transfers to/from the host computer's memory.

## Interfacing with the Host Computer's MPU

IORDY, MPU\_AEN, -MPU\_ACK, and -16BHAM are the four pins that enable the F82C5087 to interface with the PC-AT host MPU. Whenever the MPU accesses the MPU FIFO Buffer Register and data is not available to be read/written, the IORDY signal is deasserted. Using the IORDY pin is only one of several ways the MPU can check if data is available or if the FIFO is ready for another byte. (The description of MPU FIFO Buffer Register in Chapter 4 describes the other options.)

MPU\_AEN and -MPU\_ACK are used to override the MPU address bits, and force access to the MPU FIFO Buffer register. These signals enable the F82C5087 to send data to the host (AT) MPU without the host MPU generating a valid address to the MPU FIFO Buffer Register.

The -16BHAM AT host adapter signal enables 16-bit data transfers between the host computer's MPU and the SCSI data bus. This signal is asserted when the MPU read/writes 16 bits of data to/from the F82C5087 host adapter. Bits 0-7 are sent/received via pins A\_D[0-7] that comprise the lower MPU data bus. Bits 8-15 are transferred simultaneously via pins MEM\_D[0-7], the memory data bus.

CONFIG1 is the line that is pulled up internally, and used to select the MPU's strobe input. This signal is grounded when the system MPU is an Intel 80286, since it uses separate read/write signals.

CONFIG2 is also pulled up internally, and held low because the F82C5087 host adapter is configured to operate with the non-multiplexed MPU address/data bus.

INTERRUPT is a programmable pin that enables the firmware engineer to decide under what conditions (e.g., a parity error) the F82C5087 host adapter should generate an interrupt to the system MPU.

-RESET\_CAP is tied to an external capacitor for a reset pulse greater than 5 microseconds at power up. -RESET\_OUT is asserted any time the F82C5087 is reset. The F82C5087 can be reset by asserting the -RESET\_CAP or -RESET\_IN signals, or by a programmed reset.

## Interfacing with the Host Computer's DMA Controller

Typically, the FIFO\_RDY pin is connected to the host computer's DMA controller. When this pin is asserted, it indicates the F82C5087 is ready to process more data. When FIFO\_RDY is asserted, the host DMA controller will send a new byte to a F82C5087 internal register, the MPU FIFO Buffer Register 12. Thus this register can be used to pass data to/from the MPU and the F82C5087's internal FIFO.

Refer to Tables 2-2 through 2-5 later in this chapter for a complete list of the 82C5087's I/O signals and their functions.

# Signal Descriptions

Tables 2-1 lists the signals in sequential order. Tables 2-2 through 2-5 list signals in alphabetical order. Note that in all the tables an active low state is indicated by a negative sign (-) prefix. When the pin(s) can be configured for more than one function, such as A\_D[0]-A\_D[7], the other functions are listed as a subset. An N/A under a pin number indicates that the pin is not available on that particular version of the F82C5087.

Note that in all the signal descriptions, references to direction (e.g., MESSAGE OUT phase) is in reference to the initiator. For example, a MESSAGE OUT phase indicates the initiator wants to send a message to the target. Refer to Table 2-6 for pad drive capacity of the F82C5087's pins.

## I/O Signals

Table 2-2 lists the F82C5087 input/output signals and their functions.

| Ta | L. | <br>2 |

|----|----|-------|

|    |    |       |

| Signal<br>Symbol | Signal<br>Name      | 1/0 | Pin#           | Function                                                                                                                                                                                                                                                                                       |

|------------------|---------------------|-----|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A_D[0-7]         | Address/Data<br>Bus | I/O | 13-16<br>18-21 | These are active high, tri-state signals. When the active high CONFIG2 pin is high, these address/data lines interface with the MPU's lower 8-bit address/data bus. The addresses are latched into the internal address register by the falling edge of the ADDRESS LATCH ENABLE signal (ALE). |

|                  |                     |     |                | If the address is within the range of the internal chip select, the 8-bit data is written/read to/from a register, depending on the I/O write or I/O read input control lines.                                                                                                                 |

| D0-D7            | Data Bus            | I/O |                | When CONFIG2 is pulled low these lines carry only data.                                                                                                                                                                                                                                        |

| A3               | Address Bit 3       | I   | 47             | When the active high CONFIG2 signal is low, this active high line provides address bit 3 for internal register selection. Refer to Table 4-1 for 5087 register addresses.                                                                                                                      |

| A4               | Address Bit 4       | I   | 73 -           | When the active high CONFIG2 signal is low, this active high line provides address bit 4 for internal register selection. Refer to Table 4-1 for the addresses of the 5087 internal registers                                                                                                  |

| Signal<br>Symbol | Signal<br>Name       | 1/0 | Pin# | Function                                                                                                                                                                                                                                                                                                                             |

|------------------|----------------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -ACK             | SCSI<br>Acknowledge  | I/O | 67   | The initiator drives this active low signal to indicate acknowledgment of a REQ/ACK handshake for a SCSI data bus transfer. In target mode, the 5087 receives this bidirectional I/O line. In initiator mode, this line is driven by the 5087 in response to the target's request for data to be transferred over the SCSI data bus. |

| -ATN             | SCSI Attention       | I/O | 64   | Initiator asserts this active low, SCSI bus control signal to indicate the ATTENTION condition and to request a MESSAGE OUT phase.                                                                                                                                                                                                   |

| -BSY             | SCSI Busy            | I/O | 65   | This active low, SCSI bus control signal indicates the bus is currently in use.                                                                                                                                                                                                                                                      |

| +BUF_IN          | Buffer In            | 1   | 44   | This input signal provides direct control of the BUF_OUT signal if SCSI differential mode is disabled. Its value can be read by the MPU.                                                                                                                                                                                             |

| +BUF_OUT         | Buffer Out           | 0   | 36   | This open drain 48 mA output line can be driven from the BUF_IN signal in non-differential (single-ended drivers/receivers) SCSI mode. This signal provides the reset out signal to the SCSI bus when differential drivers (multiple-ended drivers) are connected.                                                                   |

| -C_D             | SCSI<br>Control/Data | ľO  | 74   | In target mode, the 5087 drives this bidirectional I/O line for all SCSI command and data transfers.                                                                                                                                                                                                                                 |

|                  |                      |     |      | In initiator mode, the 5087 receives this active low signal that indicates the target has SCSI command/data to transfer.                                                                                                                                                                                                             |

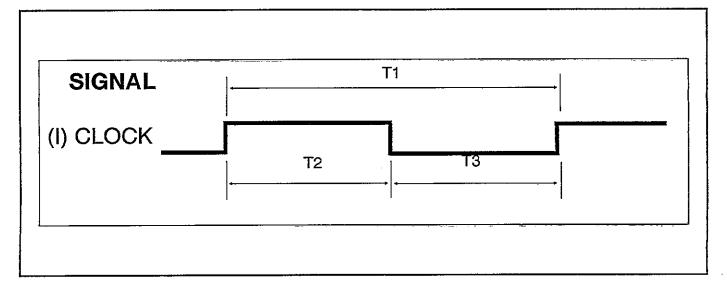

| CLOCK            | Clock                | ĭ   | 80   | This active high, input signal is for a free running clock used for all internal timing Recommended clock frequency is 24 to 32 MHz.                                                                                                                                                                                                 |

Input/Output Signals (continued)

| nals (continued)      |                                                                                                               |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal<br>Name        | I/O                                                                                                           | Pin#                                                                                                                     | Function                                                                                                                                                                                                                                                                                                                                                                                                              |

| Configuration1        | I                                                                                                             | 7                                                                                                                        | This line is pulled up internally and used to select the MPU's strobe inputs. When this active high, input signal is grounded, the 5087 chip is configured for an 8085/8051-type MPU that uses individual read and write strobes. When this signal is left open, the 5087 chip is configured for a Z8-type MPU that uses separate strobe and read/write signals.                                                      |

| Configuration2        | I .                                                                                                           | 61                                                                                                                       | When this active high signal is high, the 5087 chip is configured to operate with a multiplexed address and data MPU bus. When this line is low, pins A0-A4 (-XOR[5-7], A3, and A4) are used to select the internal registers. Refer to Table 4-1 for a list of the addresses of the 5087 internal registers. This signal is pulled up internally. Typically it will be pulled up by a resistance of 25 Kohms.        |

| DMA<br>Acknowledge    | I                                                                                                             | 48                                                                                                                       | This active low, input signal provides the 5087 with the acknowledge handshake signal from the memory data bus DMA controller. When this active low signal is asserted, the 5087 gates data onto the memory data bus (write), or clocks data into (read) the 5087 on the trailing edge of -DMA_ACK.                                                                                                                   |