recover from a protection violation condition. The coprocessor operation causing this condition is terminated.

# XGA Adapter Identification, Location and XGA Mode Setting

This section describes XGA subsystem identification and XGA mode setting. Information on VGA mode setting, and on switching from XGA mode to VGA mode, is described in "Switching the XGA subsystem from XGA to VGA Mode" on page 3-224.

An new mechanism for identifying XGA family subsystems has

been introduced with the XGA-NI adapter, which is described in

"XGA Display Mode Query and Set (DMQS)." DMQS will identify

XGA family adapters, provide information for Extended Graphics

Mode setting, and ensure migration for applications and drivers on

future XGA hardware and displays.

As the original XGA subsystem did not support DMQS, it is necessary for device drivers written to run on both XGA and XGA-NI subsystems to incorporate both mechanisms, attempting first to identify and locate the XGA-NI subsystem using DMQS, and failing that to use the original XGA specific mechanism described in "Locating and Initialising the XGA Subsystem without DMQS" on page 3-208.

DMQS may be implemented on original XGA level subsystems, so software should not assume that the existence of DMQS capability is proof of XGA-NI level of function.

In a system with multiple XGA subsystems, if any one XGA

subsystem has DMQS capability, it will provide DMQS services for

all XGA subsystems recognised. Software should not use the

original XGA identification procedure if DMQS BIOS Services are

supported (see "DMQS BIOS Interface" on page 3-194).

# XGA Display Mode Query and Set (DMQS)

3-192 XGA Function- May 7th 1992

## DMQS Architecture Overview

DMQS will identify XGA family adapters, provide information for Extended Graphics Mode setting, and ensure migration for applications and drivers on future hardware and displays.

DMQS is comprised of two types of data: DMQS primary data and

DMQS display information, contained in the display information

files.

| The primary data is returned to the software via an INT 10 Video | BIOS code point.

| The DMQS primary data contains the following information for | each XGA instance:

- XGA implementation level identifier

- · Location of XGA I/O registers or ports in I/O space

- Location of memory mapped XGA registers in system address space

- Location of 1 Meg memory mapped XGA aperture

- Location of 4 Meg memory mapped XGA aperture

- System address at which the XGA accesses video memory

- The composite ID of the attached display (see "Composite Display ID" on page 3-204)

- Amount of video memory available

The Adapter POST 'hooks' the INT 10 Video BIOS to point to two

new code points. One code point returns the total size of the

DMQS data array for all XGA instances. The other code point

returns the DMQS data to the caller's buffer.

Software accesses the new BIOS code points to obtain the DMQS data stored by POST. Using the information from the composite ID field in the DMQS data, the device driver generates the DMQS display information file name. The DMQS display file is stored in a reserved directory named XGA\$DMQS, or in the directory named in the DMQSPATH environment variable.

Note: In some operating systems, an alternative directory or path may be necessary.

Software should first look for the DMQSPATH environment variable

to locate the directory containing the DMQS display information

files. If the DMQSPATH environment does not exist, software

| should then look for a directory named XGA\$DMQS on the boot | disk.

| The DMQS display information file contains the following data:

- Display specific data

- Physical display dimensions

- Display type (color, mono, LCD, CRT etc.)

- The number of distinct Extended Graphics modes available on this display

- For each such mode available

- The mode dimensions

- The minimum level of XGA Adapter that supports this mode

- XGA Standard Register settings to place the XGA Adapter in that particular mode.

Using the data contained in both the XGA DMQS primary data and the DMQS display information file, the Device Driver/Application can determine:

- The capability and physical characteristics of the XGA family adapter and display

- XGA Implementation level

- Video memory size

- Physical display dimensions

- Color/Mono/LCD display information

- The location of all XGA registers and display buffers

- · List of the modes available on the adapter/display combination

- Mode setting data for each mode

With this information software can set the XGA and attached

display into any available Extended Graphics mode without any

hard-coded dependencies on displays or adapters.

If the DMQS display information file cannot be located, software

should revert to direct mode setting as described in "Locating and

Initialising the XGA Subsystem without DMQS" on page 3-208.

# | DMQS BIOS Interface

The following two Video Int 10h code points are required to pass DMQS data to the software.

3-194 XGA Function- May 7th 1992

| Video BIOS Int 10h Software Interrupt function

| (AH) = 1FH - XGA Display Mode Query and Set (DMQS)

| (AL) = 00H - Read DMQS Data Length

| On Return:

- (AL) = 1FH function supported (BX) = Number of bytes of DMQS data

| Video BIOS Int 10h Software Interrupt function | (AL) = 01H - Read DMQS Data (ES:DI) - User buffer pointer for return of information | On Return: User buffer contains DMQS data (AL) = 1FH - function supported As many as eight instances of XGA are possible. One copy of the following data structure exists for every instance: (DI+00H) word - Offset in bytes to DMQS data for next XGA instance (DI+02H) byte - Slot number (DI+03H) byte - XGA implementation function level identifier (DI+04H) byte - XGA implementation resolution level identifier (DI+05H) word - Vendor identifier - identifies card vendor (DI+07H) word - Vendor defined field (DI+09H) word - XGA Adapter I/O register base address (DI+0BH) word - XGA Coprocessor register base address - The location of memory mapped XGA coprocessor registers in system address space Multiply the value of this field by 10h to get the physical address (DI+0DH) word - 1 Megabyte System Video Memory Aperture - The location of 1 meg memory mapped XGA aperture in physical address space. A value of 0 indicates that the aperture is not allocated. Multiply the value of this field by 100000h to get the physical address (DI+0FH) word - 4 Megabyte System Video Memory Aperture - The location of 4 meg memory mapped XGA aperture in physical address space. A value of 0 indicates that the aperture is not allocated. Multiply the value of this field by 100000h to get the physical address (DI+11H) word - Video Memory Base Address - The location of video memory in XGA system address space. Multiply the value of this field by 100000h to get the physical address. (DI+13H) word - Composite ID of the attached display

3-196 XGA Function- May 7th 1992

| (DI+15H) | byte  | - | Amount of video memory available,                 |

|----------|-------|---|---------------------------------------------------|

|          |       |   | in multiples of 256K bytes                        |

| (DI+16h) | dword | - | Alternate XGA Coprocessor register base address - |

|          |       |   | The location of alternative memory mapped XGA     |

|          |       |   | coprocessor registers in protect mode system      |

|          |       |   | address space. A value of 0 indicates that the    |

|          |       |   | alternative register location does not exist. A   |

|          |       |   | non-zero value is the physical location in system |

|          |       |   | address space. If present, higher performance is  |

|          |       |   | available using the registers at this location.   |

|          |       |   |                                                   |

(DI+?? ) misc - DMQS Data for further XGA Instances

## | Notes:

- Although the bits per pixel information has been omitted from the BIOS interface, it can be inferred from the XGA level (current level has 16 bits per pixel maximum), the video memory size, and the number of pixels on the screen. Divide the video memory size in bits by the number of pixels on the screen in a particular mode (pixel height time pixel width) to get the maximum possible bits per pixel. Round off or down to the nearest supported bits per pixel value.

- 2. All fields will be coded in Intel format (low order byte first in word).

- These calls return DMQS primary data for all XGA subsystems present in the system, both XGA and XGA-NI. XGA-NI subsystems recognise and provide DMQS services for non DMQS capable XGA subsystems.

## | DMQS Display Information Files

Software should expect to find the DMQS display information files in the XGA\$DMQS directory on the boot disk, or alternatively in the directory specified in the DMQSPATH environment variable. This section on DMQS display information file installation is included for information only.

Adapter and System Diskettes: Configuration information for

future video subsystems must include a composite DMQS display

file. The composite file is made up of the individual DMQS display

information files for all displays available at that time. It is made

by merging the individual display information files into a composite

file. The individual files can be merged in any order.

The naming convention for the composite display file is the adapter ID followed by the letter M with an extension of DGS. For an adapter with a POS ID of hex 8FD9, the filename for the composite file is 8FD9M.DGS.

Future systems with the XGA subsystem integrated on the system

board will provide the composite file on the Reference Diskette.

Adapters will provide the file on the Option Diskette.

| **Display Diskette:** Future displays which support new function, will | ship with a display diskette to support the adapter in the extended | graphics modes. The display diskette contains the DMQS display | information file. The diskette will be a DOS format (FAT) diskette.

The naming convention for the display information file is the letters MON followed a 4 character alpha-numeric string which would typically be an ASCII representation of the composite Display ID. These files use the file extension DGS. For a display with an ID of hex 001C, the filename for the display information file is MON001C.DGS.

Information in the DMQS display information file helps identify levels of hardware support. The revision level for the DMQS display information file allows an update to the file to replace an earlier version. And within the individual mode table, a field identifies the minimum level of XGA hardware that must be present to use that mode.

DMQS Display Information Files Installation: The installation of

the display information files is operating system specific. The

display files may be installed during device driver installation.

Both the composite display file and any necessary individual

display information files would be copied to a subdirectory named

XGA\$DMQS. The DMQSPATH environment variable may also be

used to locate DMQS display information files in an alternative

directory. The path to the XGA\$DMQS directory and the means of

finding the path is operating system specific.

In a LAN Server environment using remote IPL, the boot disk for

such systems is on the server. Display information files are

included with the boot image for diagnostics. For other

environments, the location of the display files is operating system

specific.

**3-198** XGA Function– May 7th 1992

# | DMQS Display Information File Structure

*Overview:* The DMQS display information files are stored in the

XGA\$DMQS directory of the boot drive unless the user chooses to

store the XGA\$DMQS subdirectory on another path. These files

can be used by applications to determine the display

characteristics, the available modes and the register values to use

in setting modes.

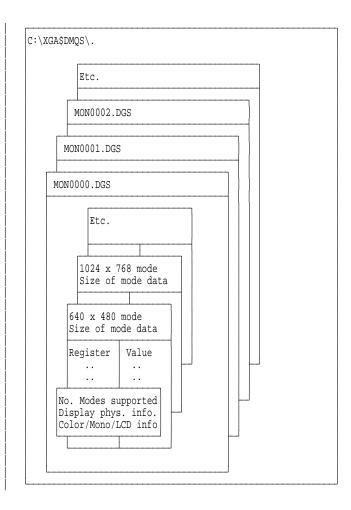

| The XGA\$DMQS directory contains a number of individual files, | one file for each display available.

As described in "DMQS Customisation File" on page 3-205, the composite ID returned in the DMQS primary Data Area may be over-ridden under user control.

If the DMQS display information file cannot be located, software

should revert to direct mode setting as described in "Locating and

Initialising the XGA Subsystem without DMQS" on page 3-208.

| The following figures show the structure of the directory and the | individual display information files.

| Figure 3-187. DMQS display information file structure

| **Details:** The following table (Figure 3-188) shows the detailed | layout of the DMQS display information file. All fields are in | hexadecimal, Intel format (low order byte first in word).

3-200 XGA Function- May 7th 1992

| Figure              | 3-188. D              | MQS display information file layout                                                                                                                                                                                                                                                                                  |

|---------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Offset              | Data<br>Type          | Description                                                                                                                                                                                                                                                                                                          |

| 00h                 | Bytes                 | DGS header data                                                                                                                                                                                                                                                                                                      |

|                     |                       | The header must be hardcoded in hex to the following value: EB1B 901D 0045 4453 5900 0000 0000 2020 2000 0022 00EB 0690 FE01 0101 00EB 0190 F8CB                                                                                                                                                                     |

| 22h                 | Word                  | This should be ignored by software.<br>Total length of data in the file (bytes)                                                                                                                                                                                                                                      |

| 24h                 | Word                  | This field is used to unpack multiple display information<br>files from a composite file<br>Composite ID - used for unpacking a composite display<br>file                                                                                                                                                            |

| 26h<br>27h<br>28h   | Byte<br>Byte<br>Word  | Revision Level - used to control file update<br>Number of modes supported by this display<br>Display Type                                                                                                                                                                                                            |

| 2Ah.<br>2Ch.<br>2Eh | Word<br>Word<br>Bytes | 00hMono CRT01hColor CRT02hMono LCD03hColor LCD04hMono Borderless capable05hColor Borderless capableWidth of Screen in millimetersHeight of Screen in millimetersHeight of Screen in millimetersNull terminated ASCII string which describes the displayin user friendly terms. The length of this field is 80 bytes. |

| 7Eh                 | Word                  | The string may be less than 80 bytes.<br>Offset of Individual Mode Data from the beginning of this<br>file                                                                                                                                                                                                           |

| 80h                 | Word                  | Length of first optional extension, including identifier.                                                                                                                                                                                                                                                            |

|                     |                       | A length value of 0 indicates no optional extensions exist.                                                                                                                                                                                                                                                          |

| 82h                 | Word                  | A non-zero value indicates that one or more optional<br>extensions are present. Each optional extension consists<br>of a length field, a 16 bit identifier, and the optional<br>extension data. A zero length field terminates the chain of<br>optional extensions.                                                  |

| 82n<br>84h<br>xxh   | Bytes                 | First optional extension identifier (if present)<br>First optional extension data (if present)<br>Il First of multiple tables of variable length mode specific<br>data, see Figure 3-189 on page 3-201 for layout.                                                                                                   |

The following table (Figure 3-189) shows the DMQS display data

for individual modes. Multiple instances of this data may exist

within the display file, one for each mode available on the

applicable display.

| Offset | Data<br>Type | Description                                                                                                                                                                                                                                                                                                         |

|--------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00h    | Word         | Length of Individual Mode Data (bytes in this table)                                                                                                                                                                                                                                                                |

| 02h    | Word         | Screen pixel Width of Mode                                                                                                                                                                                                                                                                                          |

| 04h    | Word<br>Word | Screen pixel Height of Mode                                                                                                                                                                                                                                                                                         |

| 06h    | word         | Minimum XGA implementation levels on which this mode<br>is supported.                                                                                                                                                                                                                                               |

| 08h    | Word         | A display may be capable of more modes than an earlie<br>adapter implementation may be capable of supporting.<br>See "XGA Level Identifier" on page 3-205.<br>Vendor ID                                                                                                                                             |

|        |              | For modes which are unique to a specific vendor, this field must be set. Currently, this field is reserved. It wi be set to zero.                                                                                                                                                                                   |

| 0Ah    | Word         | Reserved                                                                                                                                                                                                                                                                                                            |

| 0Ch    | Word         | This field is intended to be used as a vendor defined fie<br>This field will be activated when the Vendor ID (above)<br>field is set. This field may be defined by the vendor to<br>specify unique modes of operation.<br>Mode function type flags                                                                  |

|        |              | This field identifies special capability the mode may hav                                                                                                                                                                                                                                                           |

|        |              | Bit 00 =Normal, 1 =borderlessBit 10 =Interlaced, 1 =Non-InterlacedBits 2-15Reserved                                                                                                                                                                                                                                 |

| 0Eh    | Word         | N = Offset in bytes to mode set data from beginning of                                                                                                                                                                                                                                                              |

| 10h    | Word         | this table<br>Mode Pixel Rate                                                                                                                                                                                                                                                                                       |

| 12h    | Word         | This 16 bit value is 4 times the mode pixel rate in<br>megaHertz. For example, a value of 360 indicates a mo<br>pixel rate of 90 MHz.<br>Mode Line Rate                                                                                                                                                             |

| 14h    | Word         | This 16 bit value is 10 times the mode line rate in<br>KiloHertz. For example, a value of 315 indicates a mode<br>line rate of 31.5 kHz.<br>Mode Frame Rate                                                                                                                                                         |

|        | Word         | This 16 bit value is 10 times the mode frame rate in Her                                                                                                                                                                                                                                                            |

| 16h    | Word         | For example, a value of 750 indicates a frame refresh ra<br>of 75 Hz.<br>Length of first optional extension, including identifier                                                                                                                                                                                   |

| 1011   | word         | A length value of 0 indicates no optional extensions exis                                                                                                                                                                                                                                                           |

| 18h    | Word         | A non-zero value indicates that one or more optional<br>extensions are present. Each optional extension consist<br>of a length field, a 16 bit identifier, and the optional<br>extension data. A zero length field terminates the chain<br>optional extensions.<br>First optional extension identifier (if present) |

|   | N+00h,                   | Byte | Register Type                                                                                                                                                                                                                                                 |

|---|--------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | N+03h,<br>etc.           |      | 00hWrite to XGA Direct Access I/O Register01hWrite to XGA Indexed Access I/O Register02hOR with XGA Indexed Access I/O Register03hOR with XGA Direct Access I/O Register04hAND with XGA Indexed Access I/O Register05hAND with XGA Direct Access I/O Register |

| Ĺ | N+01h,                   | Byte | Register Offset from Base I/O                                                                                                                                                                                                                                 |

|   | N+04h,<br>etc.           |      | Direct 0-Fh<br>Indexed 0-FFh                                                                                                                                                                                                                                  |

|   | N+02h,<br>N+05h,<br>etc. | Byte | Register Value                                                                                                                                                                                                                                                |

#### | Notes:

1. The 'Mode set data' section is a sequence of register settings required to place the hardware in the desired mode.

# | Mode setting from the DMQS Display Information File

The "mode set data" section of the DMQS display information file

Individual Mode Data includes only the section of the mode setting

code that is Display specific, such as CRT Controller settings.

| The complete XGA subsystem DMQS mode set sequence consists | of

- 1. Initial XGA subsystem display-independent initialisation

- 2. Display-dependent mode specific initialisation, using the "mode set data" from the display information file

- 3. Final XGA subsystem display-independent initialisation

| The complete XGA subsystem mode set sequence is as shown in | Figure 3-190 on page 3-204.

| XGA<br>Reg.<br>ID | Value                                                                                                             | Comments                                                                                                                                                                                                                            |

|-------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21x4              | 00                                                                                                                | Initial Value                                                                                                                                                                                                                       |

| 21x5              | FF                                                                                                                |                                                                                                                                                                                                                                     |

| 21x0              | 04                                                                                                                | Set Extended Graphics Mode                                                                                                                                                                                                          |

| 64                | 00                                                                                                                | Blank Display                                                                                                                                                                                                                       |

| 21x1              | 00                                                                                                                | Initial Value                                                                                                                                                                                                                       |

| 21x8              | 00                                                                                                                | Initial Value                                                                                                                                                                                                                       |

| 21x6              | 00                                                                                                                | Initial Value                                                                                                                                                                                                                       |

| 21x9              | As<br>reqd.                                                                                                       | Mode depth (no. colors)                                                                                                                                                                                                             |

|                   | Reg.<br>ID           21x4           21x5           21x0           64           21x1           21x8           21x6 | Reg.<br>ID         00           21x4         00           21x5         FF           21x0         04           64         00           21x1         00           21x8         00           21x6         00           21x9         As |

Note:

- At this point XGA subsystem mode setting becomes display and mode specific, and the "mode set" register settings read from the Display Configuration file should be written to the appropriate XGA registers.

- 2. The initial palette should then be loaded, by writing to the appropriate XGA subsystem palette/sprite registers.

- 3. The video memory should also be initialized at this point, to avoid random data appearing when the palette mask is set to make the current display PEL map contents visible.

| Sprite Control  | 36 | 00 | Initial Value |

|-----------------|----|----|---------------|

| Start Addr Low  | 40 | 00 | Initial Value |

| Start Addr Me   | 41 | 00 | Initial Value |

| Start Addr High | 42 | 00 | Initial Value |

| Display Pel Map | 43 | A0 | As required   |

| Width Low       |    |    |               |

| Display Pel Map | 44 | 00 | As required   |

| Width High      |    |    |               |

| Display Mode 2  | 51 | 04 | As required   |

| Border Color    | 55 | 00 | Initial Value |

| Palette Mask    | 64 | FF | Make visible  |

|                 |    |    |               |

| Figure 3-190. DMQS Extended Graphics Mode Register Settings

#### | Composite Display ID

The composite ID of the attached display is derived during POST,

and is made available to the software in the DMQS primary data

Area, as described in "DMQS BIOS Interface" on page 3-194.

Each display with unique function or characteristics and therefore

a unique display information file has a unique display ID. The

display presents the display ID through pins on the display

connector. The details of its derivation are shown in "Display Type

Detection" on page 3-213.

3-204 XGA Function- May 7th 1992

## XGA Level Identifier

The XGA level identifier is returned as part of the BIOS Interface

as described in "DMQS BIOS Interface" on page 3-194. The XGA

level identifier field consists of two bytes. One is the functional

level identifier, which identifies the level of the Display Controller

chip. The next is the resolution level identifier, which identifies the

level of the Serializer Palette DAC chip.

Functional Level Identifier Identifies the level of the Display Controller chip

| '03'x | Base XGA implementation (XGA Display     |

|-------|------------------------------------------|

|       | Adapter/A)                               |

|       | VOA NIL implementation lovel of function |

**'05'x** XGA-NI implementation level of function

Resolution Level Identifier Identifies the level of the Serializer Palette DAC chip

| '00'x | Base XGA implementation (XGA Display                                                                |

|-------|-----------------------------------------------------------------------------------------------------|

| '03'x | Adapter/A) (Maximum 45 MHz Pel rate)<br>XGA-NI Serializer Palette DAC. (Maximum 90<br>MHz Pel rate) |

## | DMQS Customisation File

An additional file in the DMQS file directory should be consulted to

ascertain additional XGA customisation parameters, prior to

reading the DMQS display configuration file. This file, the name of

which is "XGASETUP.PRO," (if present) contains system

customisation information, as follows:

- Specifies a display ID alias for a particular slot. This overrides the display ID physically presented by the display, and specifies an alternate DMQS Display Configuration File name to be used instead.

- Identifies the slot to be used as the primary graphics display. In a multiple XGA system, the software normally chooses which XGA subsystem to use based on factors such as screen size, XGA subsystem functionality, etc.. This entry overrides the software default, and forces the nominated slot to be the primary XGA subsystem, rather than that chosen arbitrarily by the software.

| *DMQS Customisation File Example:* Below is an example DMQS | customisation file:

| l  | /**************************************                                      |

|----|------------------------------------------------------------------------------|

| İ  | /*                                                                           |

| ĺ  | /* FILENAME: XGASETUP.PRO                                                    |

|    | /*                                                                           |

|    | /* DESCRIPTION: Profile to set XGA DMQS preferences on current system.<br>/* |

| i. | /* LAST MODIFIED: 04/09/92 at 16:13:38<br>/*                                 |

| İ  | / " /**********************************                                      |

|    | /*************************************                                       |

|    | /*************************************                                       |

| I. | /*************************************                                       |

| The profile above does the following:

- 1. Informs the software that the display in slot 5 is a display of type F0FF and the display information file MONF0FF.DGS should be used to obtain information about the installed display.

- Informs the software that the display in slot 8 is a display of type "EXMP" and the display information file MONEXMP.DGS should be used to obtain information about the installed display.

- 3. Identifies the slot (5 in this example) which holds the XGA subsystem to be used as the primary graphics display.

- **Note:** If any of the slot numbers and/or display IDs are invalid when read then the tag will be ignored and it shall not have any affect on how the XGA subsystem hardware is initialized.

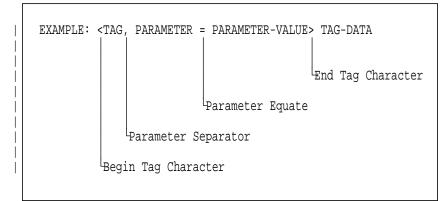

| *XGA Subsystem DMQS Customisation Tags:* The syntax for the | generalised DMQS Customisation tag is as follows:

3-206 XGA Function- May 7th 1992

| Figure 3-191. DMQS Customisation Tag Syntax

- Any number of blanks and/or new-lines can be used to separate the begin tag character, the end tag character, tags, parameters, and parameter values. So, you can flow a single tag with many parameter values over multiple lines and space the elements within the tag out for readability.

- The tag is the first text item following the begin tag character "<" and ending with the first comma "," or end tag character ">".

- If any parameters exist, then they are always separated by a comma ",". Otherwise, if no parameters exist for the tag, then the tag is immediately followed by an end tag character ">".

- Parameters are always assigned a value via the parameter equate character "=".

| Individual tags are defined as follows:

| **SLOT** Syntax Diagram:

<SLOT, NUMBER=[slot number],MONITOR\_ID=[display ID]>Text

- Parameters:

- NUMBER=[slot number] (REQUIRED) An integer value that indicates the system slot number that the XGA subsystem occupies. If this is an invalid number or there is no XGA subsystem in the specified slot, then this tag will be ignored.

| MONITOR_ID=[display ID] (REQUIRED) A four character   |

|-------------------------------------------------------|

| alpha-numeric string that will be used to construct   |

| the name of the DMQS Display Configuration file       |

| to be loaded in place of the default file. This value |

| will be used to generate a file name of the form      |

| MONXXXX.DGS where XXXX will be the display ID         |

| value specified in the tag.                           |

|                                                       |

**Text (OPTIONAL)** A comment field, that should be ignored by software.

**Description** This tag allows the user to specify a display ID override for display(s) attached to XGA subsystems with DMQS support. The display ID value in this customisation file will override the physical value read from the display by the XGA subsystem.

| **STARTUP** Syntax Diagram:

<STARTUP, NUMBER=[slot number]>Text

Parameters:

- NUMBER=[slot number] (REQUIRED) An integer value that indicates the system slot number that the XGA subsystem occupies. If this is an invalid number or there is no XGA subsystem in the specified slot, then this tag will be ignored.

- **Text (OPTIONAL)** A comment field, that should be ignored by software.

**Description** This tag allows the user to specify which particular XGA subsystem is to be used by an XGA mode application, where the default chosen by the application is inconvenient.

# Locating and Initialising the XGA Subsystem without

This section describes the original method for XGA subsystem identification and initialisation. Software should initially attempt to identify the XGA subsystem using DMQS, as described in "XGA Display Mode Query and Set (DMQS)" on page 3-192. Only when DMQS has been found to be not supported in the system, or if a

3-208 XGA Function- May 7th 1992

DMQS display information file cannot be found, should software resort to the method of XGA subsystem identification and mode setting described in this section.

| Software should not attempt to use this method in addition to | DMQS, as DMQS (if found) will provide support for both XGA and | XGA-NI subsystems.

| The procedure is as outlined here, and more detail is given later in | this section.

- 1. Identify if XGA subsystem is present by examining the system adapter's POS IDs one by one.

- 2. Locate the various I/O spaces of the XGA subsystem(s) spaces by decoding the XGA subsystem POS data.

- 3. Read the display ID to determine the attached Display type.

- 4. Determine the amount of VRAM installed on the XGA subsystem..

- 5. Determine the modes available on the attached display.

- 6. Set the XGA subsystem into the required XGA mode, either 640x480 or 1024x768 resolution.

- 7. Handle any VGA primary adapter considerations, as described in "VGA Primary Adapter Considerations" on page 3-219.

This procedure should be repeated, if necessary, until sufficient XGA subsystems in the system have been identified.

## | XGA Subsystem Identification

To identify all XGA subsystems, put every adapter in the system,

including the system board video subsystem, into setup mode in turn, and examine their POS IDs to locate any XGA adapters in the system.

For option cards, the procedure is described in System Services BIOS call INT 15h, AH=C4h Programmable Option Select in the IBM Personal System/2 and Personal Computer BIOS Interface Technical Reference.

For the system board video subsystem, a different procedure is necessary. To place the system board video subsystem in setup mode, write hex 0DF to port 94H; to enable it, write hex 0FF to port 94H.

Interrupts must be disabled for the entire period of time that each adapter is in setup mode.

The POS IDs for all adapters in the system must be read and examined to locate all the XGA adapters in the system.

The following POS IDs have been preallocated to the XGA subsystem and follow-on XGA register compatible subsystems:

- · 8FD8h to 8FDBh inclusive

- 8FD0h to 8FD3h inclusive

- VESA reserved IDs, as follows:

- 0240h to 027Fh inclusive

- 0830h to 0A7Fh inclusive

- 0A90h to 0BFFh inclusive

Check for these POS IDs when determining the existence of the XGA subsystem in the system.

After successfully matching POS IDs, read the remainder of the POS data bytes for that subsystem. This data is used to calculate the location of the XGA subsystem registers and display buffers in I/O and physical system memory address space. Descriptions of the POS data bit assignments are in "XGA POS Registers" on page 3-170. For future compatibility, mask out all reserved and unused POS data bits before using the data for these calculations.

#### | Location of XGA subsystem I/O Spaces

See "XGA POS Registers" on page 3-170 for the technical background to the following register and address space calculations.

**ROM Address:** Calculate the ROM address from POS data as follows:

ROM Address = (ROM Address field  $\times$  hex 2000) + hex 0C0000

The ROM Address field is read from POS Register 2, bits 4 to 7.

**XGA Coprocessor Registers:** The XGA coprocessor registers are referenced from a base address. This address depends on the Instance (0-7) of the XGA subsystem and the ROM address calculated as shown in "ROM Address." The Coprocessor register base address is calculated as follows:

(((128  $\times$  Instance) + hex 1C00) + ROM address)

**3-210** XGA Function– May 7th 1992

The Instance is read from POS Register 2, bits 1 to 3.

For example:

Assuming Instance = 6 and ROM address = hex 0C0000, the Coprocessor Base Address is hex 0C1F00.

*I/O Registers:* The XGA I/O registers are referenced from a base I/O address. The I/O address is calculated as follows:

Hex 21x0 (where x is the Instance)

The Instance is read from POS Register 2, bits 1 to 3.

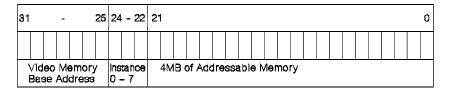

*The Video Memory Base Address:* The Video Memory Base Address is calculated from the Video Memory Base Address field in POS Register 4, and the Instance.

Figure 3-192 and Figure 3-193 on page 3-212 show how these two values combine to give the video memory base address.

Figure 3-192. XGA Video Memory Base Address

|   |            |        | ADDRESS (hex) | Viriusi Memory<br>Base Addrees |

|---|------------|--------|---------------|--------------------------------|

| Г |            | 4096MB | FFFFFFF       | 127                            |

|   |            |        | $\langle$     | $\langle$                      |

|   |            | 72MB   | 04800000      | 2                              |

|   | INSTANCE 1 | 68MB   | 04400000      | 2                              |

|   | INSTANCE 0 | 64MB   | 04000000      | 2                              |

|   | INSTANCE 7 | 60MB   | 03C00000      | 1                              |

|   | INSTANCE 6 | 56MB   | 03800000      | 1                              |

|   | INSTANCE 5 | 52MB   | 03400000      | -                              |

|   | INSTANCE 4 | 48MB   | 03000000      | -                              |

|   | INSTANCE 3 | 44MB   | 02C00000      | 1                              |

|   | INSTANCE 2 | 40MB   | 02800000      | 1                              |

|   | INSTANCE 1 | 36MB   | 02400000      | 1                              |

|   | INSTANCE 0 | 32MB   | 02000000      | 1                              |

|   |            | 16MB   | 0200000       | ľ                              |

|   |            |        |               | 0                              |

|   | ROM        | 1MB    |               |                                |

| ŀ |            |        |               |                                |

|   | SYSTEM RAM | OMB    | 0000000       | 0                              |

Figure 3-193. The XGA Video Memory Base Address Diagram

The Video Memory Base Address field defines a 32MB address range and the Instance defines a 4MB address range within the 32MB range.

3-212 XGA Function- May 7th 1992

#### For example:

Assuming Instance = 6 and the Video Memory Base Address field = 1, the Video Memory Base Address is hex 03800000.

The video memory base address, when calculated, serves two separate purposes:

4MB System Video Memory Aperture: If enabled (read from bit 0 in POS Register 4 to determine if the aperture is enabled), the 4MB system video memory aperture is located at this address in physical system address space. If virtual addressability to this range of physical address space can be achieved, the entire video memory can be accessed through this aperture at this address.

*Video Memory Location in XGA Address Space:* This address is used to identify video memory to the XGA coprocessor. It significance and use is described in "Video Memory Address Range" on page 3-235.

**1MB Aperture Base Address:** The 1MB aperture base address is calculated from the 1MB Aperture Base Address field in POS Register 5, bits 0 to 3.

- If (1MB Base field ≠ 0)

1MB Aperture Base Address = 1MB Base field × hex 100000

- If (1MB Base field = 0) 1MB Aperture is disabled.

## Display Type Detection

In order to determine what type of display is attached to the Video

Subsystem, it is necessary to read the display's identification

number, or ID. This ID is used to obtain information about the

display such as: the resolutions supported, whether it is

monochrome or color, and possibly the size of the screen.

The ID for each display is a 16 bit number, and usually uniquely

identifies the display type. Some displays that have similar

characteristics but are not the same model, have the same ID.

| The recommended method of obtaining the display ID is by use of | a BIOS call, Int 10h, (AH) = 1Fh - XGA Display Mode Query and Set | (DMQS). See "XGA Display Mode Query and Set (DMQS)" on | page 3-192. If it is necessary to read the display ID explicitly then | the following procedure must be followed.

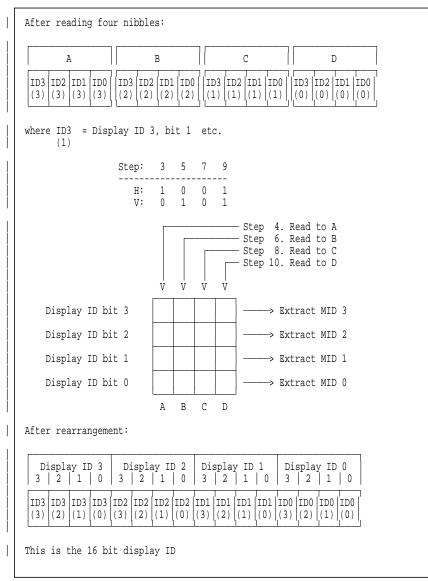

The display ID is read from the "Display ID and Comparator" register, which returns four ID bits at a time. Four reads must be performed in order to obtain all sixteen bits. The components of the ID are selected by manipulating the values of Horizontal Sync and Vertical Sync that are output to the display. Therefore, the ID may only be read when disruption of these signals may be tolerated, such as power-on time, or when changing display modes.

After setting the required "Sync Polarity" (SP field in Display Control 1 Register) to any of the various combinations of Horizontal and Vertical Sync listed below, it is necessary to wait for 15 micro-seconds for this change to take effect before display ID may be read. This is best achieved by doing five consecutive reads or writes to any byte wide XGA I/O port.

| The display ID Reading sequence is as follows:

- Prepare the CRTC for reset (Display Control 1 Register Index 50 - DB field = '01'b)

- 2. Reset the CRTC (Display Control 1 Register DB field = '00'b)

- 3. Set "Sync Polarity" (SP field in Display Control 1 Register) to '01'b This sets VSYNC to '0'b and HSYNC to '1'b.

- 4. After a 15 microsec. wait, read the display ID bits from Display ID and Comparator Register (Index 52). Place them in a hex variable A.

- 5. Set SP to '10'b This sets VSYNC to '1'b and HSYNC to '0'b.

- 6. After a 15 microsec. wait, read the display ID bits again. Place them in a hex variable B.

- 7. Set SP to '00'b This sets VSYNC to '0'b and HSYNC to '0'b.

- 8. After a 15 microsec. wait, read the display ID bits again. Place them in a hex variable C.

- 9. Set SP to '11'b This sets VSYNC to '1'b and HSYNC to '1'b.

- 10. After a 15 microsec. wait, read the display ID bits again. Placethem in a hex variable D.

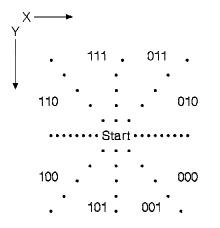

Assemble the 16 bits into four nibbles, one for each MID pin, from MSB to LSB, as shown in Figure 3-194 on page 3-215. The resulting four-hex-digit number (from MID bit 3 to bit 0) is the display ID.

3-214 XGA Function- May 7th 1992

| Figure 3-194. Reading the Display ID.

$\mid$  Figure 3-196 on page 3-217 shows a list of displays and their  $\mid$  associated IDs.

#### | Video Memory Size Determination

There are two ways to determine the size of video memory installed. Both rely on a write-readback-check, in which a particular value is written to a key location. This value is then read to determine whether the written value has persisted.

Use the system processor to write a value through an aperture to the word at offset 768KB into video memory. This technique assumes that the system video memory real mode aperture is available. See the sample code in the following figure.

```

;* Assume GS points to start of A0000 Real mode aperture

;* and VGA adapter is in text mode so A0000 Real mode

;* aperture is available for this operation.

;* Where registers are shown as (for instance 21x0h), this should

;* be filled in with the appropriate IO port address after determining

;* the location of the XGA subsystem in IO space

;*

;* First put the adapter PARTIALLY in extended graphics mode

;* to allow use of the system video memory Aperture

mov al,0

mov

dx,21x4h

; disable XGA interrupts

out dx,al

;

ax,0064h

mov

dx,21xAh

; Blank palette

mov

; indexed XGA register 64h

out

dx.ax

ax,04h

mov

dx,21x0h

; Set adapter in Extended Graphics Mode

mov

out dx,al

;

mov

al,01h

mov dx,21x1h

; Locate video memory Aperture at A0000

out dx,al

dx,21x8h

; System video memory indx req.

mov

al,0ch

; Offset 768K

mov

out dx.al

;

mov byte ptr qs:[0],0A5h ; Set byte to A5h

mov byte ptr gs:[1],0h ; Avoid shadows on data lines

byte ptr gs:[0],0A5h ; Test against value written

CMD

jne vram_512k

; 512K video memory only

mov

byte ptr gs:[0],5Ah ; Set byte to 5Ah

byte ptr qs:[1],0h ; Avoid shadows on data lines

mov

;

byte ptr gs:[0],0A5h ; Test against value written

cmp

; 1 Meg if still matches

vram_1Meg

ie

jmp

vram_512k

; Otherwise 1/2 meg found

```

```

Figure 3-195. Video Memory Size Determination

```

3-216 XGA Function- May 7th 1992

• Use the XGA subsystem PxBlt capability to perform a test similar to the previous example. Transfer a constant color to the location in video memory, then transfer that value back from video memory to system memory using busmastership.

This technique works regardless of the availability of a system video memory aperture. However, it requires physical addressability to a location in system memory for the busmastership operation.

# **Extended Graphics Modes Available**

The following figure shows the list of modes available according to the display type and size of video memory configured on the XGA subsystem.

| l | Composite    | DisEpitanyn (bDe (b) é | sq)lSijzse | (in <b>G</b> olor | Max Addr | ess512 KB Memory                         | 1MB Memory                                                                              |

|---|--------------|------------------------|------------|-------------------|----------|------------------------------------------|-----------------------------------------------------------------------------------------|

|   | FFFF<br>FF0F | None<br>8503           | 12         | Mono              | 640x480  | None<br>640x480x64 Grays                 | None<br>640x480x64 Grays                                                                |

|   | FFF0         | 8513<br>8512<br>8518   | 12<br>14   | Color             | 640x480  | 640x480x256 Colors                       | 640x480x256 Colors<br>640x480x65536 Colors                                              |

|   | F0FF         | 8515<br>8516           | 14         | Color             | 1024x768 | 640x480x256 Colors<br>1024x768x16 Colors | 640x480x256 Colors<br>640x480x65536 Colors<br>1024x768x16 Colors<br>1024x768x256 Colors |

|   | F00F         | 8604<br>8507           | 15<br>19   | Mono              | 1024x768 | 640x480x64 Grays<br>1024x768x16 Grays    | 640x480x64 Grays<br>1024x768x16 Grays<br>1024x768x64 Grays                              |

|   | F0F0         | 8514                   | 16         | Color             | 1024x768 | 640x480x256 Colors<br>1024x768x16 Colors | 640x480x256 Colors<br>640x480x65536 Colors<br>1024x768x16 Colors<br>1024x768x256 Colors |

|   | 90F0         | 8517                   | 17         | Color             | 1024x768 | 640x480x256 Colors<br>1024x768x16 Colors | 640x480x256 Colors<br>640x480x65536 Colors<br>1024x768x16 Colors<br>1024x768x256 Colors |

Figure 3-196. Availability of Extended Graphics Modes

# | Extended Graphics Mode Setting Procedure

To set the XGA subsystem into Extended Graphics mode, the configuration must be capable of supporting the required mode as listed in "Extended Graphics Modes Available" on page 3-217.

| XGA<br>Reg.XGA<br>Reg.Interrupt Enable<br>Interrupt Status21x4<br>21x5Operating Mode<br>Palette Mask21x0<br>Palette MaskCtl21x1Video Mem Aperture<br>Index21x1Video Mem Aperture<br>Index21x8Vitt Mem Ctl21x8Vitt Mem Ctl21x8Vitt Mem Ctl21x9Disp Mode 150Disp Mode 150Horiz Total Low10Horiz Total Low10Horiz Total Low11Horiz Siplay End Low12Horiz Siplay End Low16Horiz Sync Start Low18Horiz Sync End High17Horiz Sync Start Low18Horiz Sync Start Low18Horiz Sync Start Low12Vert Total Low20Vert Total Low20Vert Total Low20Vert Total Low24Vert Blank Start Ligh25Vert Blank End High27Vert Blank End High27Vert Blank End Low26Vert Blank End High27Vert Sync Start Low28Vert Sync Start High29Vert Sync Start High29Vert Sync Start High20Vert Line Comp Low20Vert Line Comp Low20Vert Line Comp Low20Vert Line Comp Low24                                                                                                                            | Color Mode Value (hex) |                      |                     |                     |                       |                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------|---------------------|---------------------|-----------------------|--------------------------------|

| Interrupt Status21x5Operating Mode21x0Palette Mask64Video Mem Aperture21x1Video Mem Aperture21x1Index21x8Virt Mem Ctl21x8Virt Mem Ctl21x6Memory Access Mode21x9Disp Mode 150Disp Mode 150Horiz Total Low10Horiz Total High11Horiz Display End Low12Horiz Blank Start Low14Horiz Sync Start Low16Horiz Sync Start Low18Horiz Sync Start High19Horiz Sync End High18Horiz Sync End High18Horiz Sync End High12Vert Total High12Vert Total High12Vert Total High23Vert Total High23Vert Blank Start Low24Vert Blank Start Low24Vert Blank Start Low26Vert Sync Start Low28Vert Sync Start Low28Vert Sync Start Low28Vert Sync Start High29Vert Sync Start High29Vert Sync Start High29Vert Sync Start High20Vert Sync Start High21Vert Sync Start High29Vert Sync Start High29Vert Sync Start High29Vert Sync Start High20Sprite Control36Start Addr Me41Start Addr Me41Start Addr Me41 <th>Oper</th> <th>1024x<br/>768x<br/>256</th> <th>1024x<br/>768x<br/>16</th> <th>640x<br/>480x<br/>256</th> <th>640x<br/>480x<br/>65536</th> <th>Comments</th> | Oper                   | 1024x<br>768x<br>256 | 1024x<br>768x<br>16 | 640x<br>480x<br>256 | 640x<br>480x<br>65536 | Comments                       |

| Operating Mode<br>Palette Mask21x0<br>64Video Mem Aperture<br>Ctl21x1Video Mem Aperture<br>Index21x8Vite Mem Ctl21x8Vitr Mem Ctl21x8Vitr Mem Ctl21x9Disp Mode 150Disp Mode 150Horiz Total Low10Horiz Total Low11Horiz Display End Low14Horiz Blank Start High13Horiz Blank Start High15Horiz Sync Start High16Horiz Sync Start High17Horiz Sync Start Low18Horiz Sync End Low16Horiz Sync End High17Horiz Sync End High18Horiz Sync End High18Horiz Sync End High12Vert Total Low20Vert Total Low21Vert Total Low22Vert Total Low24Vert Blank Start High23Vert Blank Start High23Vert Blank Start High25Vert Blank Start High25Vert Blank Start High29Vert Sync Start High29Vert Sync Start High29Vert Sync Start High20Vert Line Comp High20Vert Line Comp High20                                                                                                                        | =                      | 00                   | 00                  | 00                  | 00                    | Initial Value                  |

| Palette Mask64Video Mem Aperture21x1Video Mem Aperture21x1Index21x8Virt Mem Ctl21x6Memory Access Mode21x9Disp Mode 150Disp Mode 150Horiz Total Low10Horiz Total High11Horiz Display End Low12Horiz Blank Start High13Horiz Sync Start Low14Horiz Sync Start Low16Horiz Sync Start Low18Horiz Sync Start Low18Horiz Sync Start High19Horiz Sync Start High18Horiz Sync Posn1CHoriz Sync Posn11Vert Total High21Vert Blank Start Low24Vert Blank Start Low24Vert Blank Start Low26Vert Sync Start Low28Vert Sync Start Low28Vert Sync Start High29Vert Sync Start High29Vert Sync Start High29Vert Sync Start High20Vert Sync Start High20Vert Sync Start High21Vert Sync Start High29Vert Sync Start High29Vert Sync Start High29Vert Sync Start High20Sprite Control36Start Addr Me41Start Addr Me41Start                                                                                                                                               | =                      | FF                   | FF                  | FF                  | FF                    |                                |

| Palette Mask64Video Mem Aperture21x1Video Mem Aperture21x1Index21x8Virt Mem Ctl21x6Memory Access Mode21x9Disp Mode 150Disp Mode 150Horiz Total Low10Horiz Total High11Horiz Display End Low12Horiz Blank Start High13Horiz Sync Start Low14Horiz Sync Start Low16Horiz Sync Start Low18Horiz Sync Start Low18Horiz Sync Start High19Horiz Sync Start High18Horiz Sync Posn1CHoriz Sync Posn11Vert Total High21Vert Blank Start Low24Vert Blank Start Low24Vert Blank Start Low26Vert Sync Start Low28Vert Sync Start Low28Vert Sync Start High29Vert Sync Start High29Vert Sync Start High29Vert Sync Start High20Vert Sync Start High20Vert Sync Start High21Vert Sync Start High29Vert Sync Start High29Vert Sync Start High29Vert Sync Start High20Sprite Control36Start Addr Me41Start Addr Me41Start                                                                                                                                               | _                      | 04                   | 04                  | 04                  | 04                    | Set Extended                   |

| Video Mem Aperture<br>Ctil21x1Video Mem Aperture<br>Index21x8Virt Mem Ctil21x8Virt Mem Ctil21x8Disp Mode 150Disp Mode 150Horiz Total Low10Horiz Total High11Horiz Display End Low12Horiz Blank Start Low14Horiz Sync Start High15Horiz Sync Start High16Horiz Sync Start Low18Horiz Sync End Low16Horiz Sync Start High17Horiz Sync End High18Horiz Sync End Low16Horiz Sync End High17Horiz Sync End High18Horiz Sync End Low16Horiz Sync End High17Horiz Sync End High12Vert Total Low20Vert Total Low21Vert Total Low22Vert Total High23Vert Blank Start High23Vert Blank Start High25Vert Blank Start High25Vert Blank Start High29Vert Sync Start Low28Vert Sync Start High29Vert Line Comp Low20Vert Line Comp High2DSprite Control36Start Addr Me41Start Addr High42Buffer Pitch Low43Buffer Pitch Low44Clock Sel70Display Mode 251Ext Clock Sel70Display Mode 150Note:Initial Pale                                                                                                                                                          | =                      | 04                   | 04                  | 04                  | 04                    | Graphics Mode<br>Blank Display |

| Ctl21x1Video Mem Aperture<br>Index21x8Virt Mem Ctl21x6Memory Access Mode21x9Disp Mode 150Disp Mode 150Horiz Total Low10Horiz Total High11Horiz Display End Low12Horiz Display End Low16Horiz Blank Start Low16Horiz Blank Start High15Horiz Sync Start Low16Horiz Sync Start Low18Horiz Sync Start Low18Horiz Sync Start Low10Horiz Sync Start Low18Horiz Sync Start Low18Horiz Sync Start Low10Horiz Sync Start Low20Vert Total Low20Vert Disp End High21Vert Disp End Low22Vert Blank Start High25Vert Blank Start Low24Vert Blank Start Low26Vert Sync Start Low26Vert Sync Start High29Vert Sync Start High29Vert Sync Start High20Sprite Control36Start Addr Me41Start Addr Me41                                                                                                                                                              | -                      | 00                   | 00                  | 00                  | 00                    | Dialik Display                 |

| Index21x8Virt Mem Ctl21x6Memory Access Mode21x9Disp Mode 150Disp Mode 150Horiz Total Low10Horiz Total High11Horiz Display End Low12Horiz Display End Low14Horiz Display End Low16Horiz Stank Start Low16Horiz Sync Start High17Horiz Sync Start Low18Horiz Sync Start Low18Horiz Sync End Low10Horiz Sync Start High19Horiz Sync End High17Horiz Sync End High18Horiz Sync End High18Horiz Sync End High21Vert Total Low20Vert Total High21Vert Total High23Vert Blank End High23Vert Blank Start Low24Vert Blank Start High29Vert Sync Start Low28Vert Sync End High27Vert Sync Start High29Vert Sync End High20Vert Sync Start High29Vert Sync End2AVert Line Comp High2DSprite Control36Start Addr Me41Start Addr High42Buffer Pitch Low43Buffer Pitch Low43Buffer Pitch High44Clock Sel70Display Mode 251Ext Clock Sel70Display Mode 150                                                                                                                                                                                                        | =                      | 00                   | 00                  | 00                  | 00                    | Initial Value                  |

| Virt Mem Ctl21x6Memory Access Mode21x9Disp Mode 150Disp Mode 150Horiz Total Low10Horiz Total High11Horiz Total High13Horiz Display End Low12Horiz Display End Low14Horiz Blank Start Low16Horiz Blank Kart High17Horiz Sync Start Low18Horiz Sync Start Low16Horiz Sync Start Low18Horiz Sync Start Low18Horiz Sync Start Low10Horiz Sync Start Low10Horiz Sync Start Low10Horiz Sync Posn1CHoriz Sync Posn12Vert Total High21Vert Disp End Low22Vert Disp End High23Vert Blank Start Low24Vert Blank Start Low26Vert Sync Start Low26Vert Sync Start High29Vert Sync End2AVert Line Comp Low2CVert Line Comp High2DSprite Control36Start Addr Me41Start Addr Me41Start Addr Me41Start Addr Me41Start Addr Me41Start Addr Me41Display Mode 251Ext Clock Sel70Display Mode 150Note:Initial Palette loading must be                                                                                                                                                                                                                                   |                        |                      |                     |                     |                       |                                |

| Memory Access Mode21x9Disp Mode 150Disp Mode 150Horiz Total Low10Horiz Total Low10Horiz Total Ligh11Horiz Display End Low12Horiz Display End High13Horiz Blank Start High15Horiz Blank Start Low16Horiz Sync Start Low18Horiz Sync Start Low18Horiz Sync End Low10Horiz Sync End High17Horiz Sync End High18Horiz Sync Posn1CHoriz Sync Posn11Vert Total Low20Vert Total High21Vert Disp End Low22Vert Disp End Low24Vert Blank Start High25Vert Blank Start High25Vert Blank Start High26Vert Sync Start Low28Vert Sync Start Low24Vert Sync Start High29Vert Sync Start High29Vert Sync Start High20Vert Line Comp Low20Vert Line Comp High2DSprite Control36Start Addr Me41Start Addr High42Buffer Pitch Low43Buffer Pitch Low43Buffer Pitch Low43Buffer Pitch Low51Ext Clock Sel70Display Mode 150Note:Initial Palette loading must be                                                                                                                                                                                                          | =                      | 00<br>00             | 00<br>00            | 00<br>00            | 00                    | Initial Value<br>Initial Value |

| Disp Mode 150Disp Mode 150Horiz Total Low10Horiz Total Ligh11Horiz Display End Low12Horiz Display End High13Horiz Biank Start Low14Horiz Biank Start Low14Horiz Biank Start Low16Horiz Biank Start Low18Horiz Sync Start High19Horiz Sync End Low1AHoriz Sync Start High19Horiz Sync End High18Horiz Sync End High18Horiz Sync End High18Horiz Sync End High21Vert Total Low20Vert Total Low20Vert Total High21Vert Disp End Low22Vert Blank Start Low24Vert Blank Start Low24Vert Blank Start High25Vert Blank Start High25Vert Sync Start High29Vert Sync Start High20Vert Line Comp Low22Vert Line Comp High2DSprite Control36Start Addr High42Buffer Pitch Low43Buffer Pitch Low43Buffer Pitch Low44Clock Sel50Display Mode 251Ext Clock Sel70Display Mode 150                                                                                                                                                                                                                                                                                  | =                      | 00                   | 00                  | 00                  | 00                    | Initial Value                  |

| DispMode 150HorizTotal Low10HorizTotal High11HorizTotal High13HorizDisplay End Low12HorizBiank Start Low14HorizBlank Start High15HorizBlank Start High17HorizBlank End High17HorizSync Start Low18HorizSync Start Low18HorizSync End High18HorizSync Ross1CHorizSync Posn1CHorizSync Posn1CHorizSync Posn12Vert Total High23Vert Disp End Low24Vert Blank Start Low24Vert Blank Start Low26Vert Sync Start Low28Vert Sync Start High29Vert Sync End2AVert Line Comp Low2CVert Line Comp High2DSprite Control36Start Addr Me41Start Addr Me41Start Addr Me41Start Addr Me41Start Addr Me41Start Addr Me41Display Mode 251Ext Clock Sel70Display Mode 150Note:Initial Palette loading must be                                                                                                                                                                                                                                                                                                                                                         | =                      | 01                   | 01                  | 01                  | 01                    | Prepare for reset              |

| HorizTotal Low10HorizTotal High11HorizDisplay End Low12HorizDisplay End High13HorizBlank Start Low14HorizBlank Start High15HorizBlank End Low16HorizBlank End High17Horiz Sync Start Low18Horiz Sync End Low10Horiz Sync End High19Horiz Sync End High18Horiz Sync Posn11Horiz Sync Posn11Vert Total Low20Vert Total High21Vert Disp End High23Vert Disp End High23Vert Blank Start High25Vert Blank Start High29Vert Sync Start High29Vert Sync Start High29Vert Sync End2AVert Line Comp Low2CVert Line Comp High2DSprite Control36Start Addr Me41Start Addr High42Buffer Pitch Low43Buffer Pitch Low43Buffer Pitch Low44Clock Sel50Display Mode 251Ext Clock Sel70Display Mode 150                                                                                                                                                                                                                                                                                                                                                               | =                      | 00                   | 00                  | 00                  | 00                    | Reset CRT Ctrl                 |

| Horiz Display End Low12Horiz Display End High13Horiz Blank Start Low14Horiz Blank Start High15Horiz Blank End Low16Horiz Blank End High17Horiz Sync Start Low18Horiz Sync Start Low18Horiz Sync End Low14Horiz Sync End Low14Horiz Sync End High19Horiz Sync Posn1CHoriz Sync Posn12Vert Total Low20Vert Total High21Vert Disp End Low22Vert Disp End Low24Vert Blank Start Low26Vert Blank Start Low26Vert Sync Start Low28Vert Sync Start Low26Vert Sync Start High29Vert Sync Start High29Vert Sync End2AVert Line Comp Low20Vert Line Comp High20Sprite Control36Start Addr High41Start Addr High42Buffer Pitch High44Clock Sel50Display Mode 251Ext Clock Sel70Display Mode 150                                                                                                                                                                                                                                                                                                                                                                | =                      | 9D                   | 9D                  | 63                  | 63                    | )                              |

| Horiz Display End High13Horiz Blank Start Low14Horiz Blank Start High15Horiz Blank Start High15Horiz Blank End Low16Horiz Sync Start Low18Horiz Sync Start Low18Horiz Sync End Low14Horiz Sync End Low18Horiz Sync End High19Horiz Sync End High18Horiz Sync End High18Horiz Sync Posn11Vert Total Low20Vert Total High21Vert Disp End Low22Vert Disp End Low22Vert Blank Start High25Vert Blank Start High25Vert Blank Start High29Vert Sync Start High29Vert Sync End2AVert Line Comp Low2CVert Line Comp High2DSprite Control36Start Addr High42Buffer Pitch Low43Buffer Pitch Low44Clock Sel54Display Mode 251Ext Clock Sel70Display Mode 150                                                                                                                                                                                                                                                                                                                                                                                                   | =                      | 00                   | 00                  | 00                  | 00                    | j                              |

| Horiz Blank Start Low14Horiz Blank Start High15Horiz Blank End Low16Horiz Blank End High17Horiz Sync Start Low18Horiz Sync Start High19Horiz Sync End Low18Horiz Sync End High18Horiz Sync Cart High18Horiz Sync Posn1CHoriz Sync Posn1CHoriz Sync Posn12Vert Total Low20Vert Total High21Vert Disp End Low22Vert Disp End Low24Vert Blank Start Low26Vert Blank End High27Vert Sync Start High29Vert Sync End High28Vert Sync End High24Vert Blank End High27Vert Sync Start High29Vert Sync End2AVert Line Comp High2DSprite Control36Start Addr Low40Start Addr Low43Buffer Pitch Low43Buffer Pitch High44Clock Sel50Display Mode 251Ext Clock Sel70Display Mode 150                                                                                                                                                                                                                                                                                                                                                                             | =                      | 7F                   | 7F                  | 4F                  | 4F                    | )                              |

| Horiz Blank Start High15Horiz Blank End Low16Horiz Blank End High17Horiz Sync Start Low18Horiz Sync Start Low18Horiz Sync End Low14Horiz Sync End Low14Horiz Sync End High18Horiz Sync Posn1CHoriz Sync Posn12Vert Total High21Vert Total High23Vert Disp End High23Vert Blank Start Low24Vert Blank Start Low26Vert Sync Start Low28Vert Sync Start High29Vert Sync End2AVert Line Comp Low2CVert Line Comp High2DSprite Control36Start Addr High41Start Addr High42Buffer Pitch Low43Buffer Pitch High44Clock Sel50Display Mode 251Ext Clock Sel70Display Mode 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | =                      | 00                   | 00                  | 00                  | 00                    |                                |

| Horiz Blank End Low16Horiz Sync Start Low18Horiz Sync Start Low18Horiz Sync End Low14Horiz Sync End Low14Horiz Sync End Low18Horiz Sync End High18Horiz Sync Posn1CHoriz Sync Posn11Vert Total Low20Vert Total High21Vert Disp End Low22Vert Disp End Low22Vert Blank Start Low24Vert Blank Start High25Vert Blank End Low26Vert Sync Start Low28Vert Sync Start Low28Vert Sync End2AVert Line Comp Low2CVert Line Comp High2DSprite Control36Start Addr High42Buffer Pitch Low43Buffer Pitch Low43Buffer Pitch Low54Display Mode 251Ext Clock Sel70Display Mode 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | =                      | 7F<br>00             | 7F                  | 4F                  | 4F<br>00              |                                |