# **Microprocessors and Instruction Sets**

| 80286 Microprocessor                          | . 1  |

|-----------------------------------------------|------|

| Real-Address Mode                             | . 1  |

| Protected Virtual Address Mode                | . 1  |

| 80287 Math Coprocessor                        | . 2  |

| Programming Interface                         | . 2  |

| Hardware Interface                            | . 3  |

| 80386 Microprocessor                          | 4    |

| Real Address Mode                             |      |

| Protected Virtual Address Mode                | 5    |

| Virtual 8086 Mode                             |      |

| 80386 Paging Mechanism                        |      |

| 80387 Math Coprocessor                        |      |

| 80387 To 80486 Math Coprocessor Compatibility | 10   |

| Programming Interface                         | 10   |

| Hardware Interface                            | 11   |

| 80486 Microprocessor                          |      |

|                                               |      |

|                                               |      |

| Cache Paging Control                          | 14   |

| Page Protection Feature                       | 15   |

| New Alignment Check                           | 16   |

| New Instructions                              | 16   |

| 80286 Microprocessor Instruction Set          | 17   |

| Data Transfer                                 | . 17 |

| Arithmetic                                    |      |

|                                               |      |

| String Manipulation                           | 27   |

| Control Transfer                              | 29   |

| Processor Control                             | . 33 |

| Protection Control                            | . 35 |

| 80287 Math Coprocessor Instruction Set        |      |

| Data Transfer                                 | 38   |

| Comparison                                    | 40   |

| Constants                                     | 41   |

| Arithmetic                                    | 42   |

| Transcendental                                | 43   |

| Processor Control                             |      |

| Introduction to the 80386 Instruction Set     | 45   |

| Code and Data Segment Descriptors             |      |

| Prefixes                                      |      |

| Instruction Format                            | 48   |

| Encoding                                      | 50   |

| Address Mode                                  | 50   |

| ······································        |      |

| Operand Length (w) Field                     | 53  |

|----------------------------------------------|-----|

| Segment Register (sreg) Field                | 54  |

| General Register (reg) Field                 | 54  |

| Operation Direction (d) Field                | 55  |

| Sign-Extend (s) Field                        | 55  |

| Conditional Test (tttn) Field                | 55  |

| Control, Debug, or Test Register (eee) Field | 56  |

| 80386 Microprocessor Instruction Set         | 57  |

| Data Transfer                                | 57  |

| Segment Control                              | 60  |

| Flag Control                                 | 61  |

| Arithmetic                                   | 62  |

| Logic                                        | 67  |

| String Manipulation                          | 71  |

| Repeated String Manipulation                 | 72  |

| Bit Manipulation                             | 74  |

| Control Transfer                             | 75  |

| Conditional Jumps                            | 76  |

| Conditional Byte Set                         | 81  |

| Interrupt Instructions                       | 83  |

| Processor Control                            | 84  |

| Processor Extension                          | 85  |

| Prefix Bytes                                 | 85  |

| Protection Control                           | 86  |

| Introduction to the 80387 Instruction Set    | 89  |

| 80387 Usage of the Scale-Index-Base Byte     | 89  |

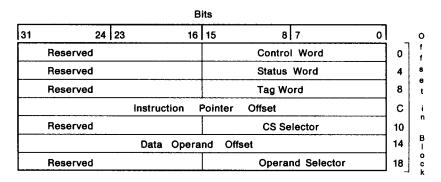

| Instruction and Data Pointers                | 89  |

| New Instructions                             | 92  |

| 80387 Math Coprocessor Instruction Set       | 93  |

| Data Transfer                                | 93  |

| Comparison                                   | 94  |

| Constants                                    | 95  |

| Arithmetic                                   | 96  |

| Transcendental                               | 98  |

| Processor Control                            | 98  |

| 80486 Microprocessor Instruction Set         | 100 |

# Figures

| 1.  | 80287 Data Types                                         | . 3 |

|-----|----------------------------------------------------------|-----|

| 2.  | 80386 Addressing                                         | . 6 |

| 3.  | Paging Mechanism                                         | . 8 |

| 4.  | Data Type Classifications and Instructions               | . 9 |

| 5.  | 80387 Data Types                                         | 11  |

| 6.  | Control Register 0                                       | 13  |

| 7.  | 80386 Compatible Operation                               |     |

| 8.  | 80486 Protection Operation                               | 15  |

| 9.  | 2-Bit Register Field                                     | 37  |

| 10. | 3-Bit Register Field                                     |     |

| 11. | 80287 Encoding Field Summary                             | 38  |

| 12. | 80386 Code and Data Segment Descriptor Format            | 46  |

| 13. | Instruction Format                                       |     |

| 14. | 80386 Instruction Set Encoding Field Summary             | 49  |

| 15. | Effective Address (16-Bit and 32-Bit Address Modes)      | 50  |

| 16. | Scale Factor (s-i-b Byte Present)                        | 51  |

| 17. | Index Registers (s-i-b Byte Present)                     | 51  |

| 18. | Base Registers (s-i-b Byte Present)                      | 52  |

| 19. | Effective Address (32-Bit Address Mode – s-i-b Byte      |     |

|     | Present)                                                 |     |

| 20. | Operand Length Field Encoding                            | 53  |

| 21. | Segment Register Field Encoding                          | 54  |

| 22. | General Register Field Encoding                          |     |

| 23. | Operand Direction Field Encoding                         |     |

| 24. | Sign-Extend Field Encoding                               |     |

| 25. | Conditional Test Field Encoding                          |     |

| 26. | Control, Debug, and Test Register Field Encoding         |     |

| 27. | 80387 Encoding Field Summary                             |     |

| 28. | Instruction and Pointer Image (16-Bit Real Address Mode) |     |

| 29. | Instruction and Pointer Image (16-Bit Protected Mode)    | 91  |

| 30. | Instruction and Pointer Image (32-Bit Real Address Mode) | 91  |

| 31. | Instruction and Pointer Image (32-Bit Protected Mode)    | 91  |

# Notes:

# 80286 Microprocessor

The 80286 microprocessor subsystem has the following:

- 24-bit address

- 16-bit data interface

- Extensive instruction set, including string I/O

- · Hardware fixed-point multiply and divide

- Two operational modes:

- 8086-compatible Real Address

- Protected Virtual Address.

- 16MB (MB equals 1,048,576 or 2<sup>20</sup> bytes) of physical address space

- 1GB (GB equals 1,073,741,824 or 2<sup>30</sup> bytes) of virtual address space.

# **Real-Address Mode**

In the real-address mode, the address space of the system microprocessor is a contiguous array of up to 1MB. The system microprocessor generates 20-bit physical addresses to address memory.

The segment portion of the pointer is interpreted as the upper 16 bits of a 20-bit segment address; the lower 4 bits are always 0. Therefore, segment addresses begin on multiples of 16 bytes.

All segments in the real-address mode are 64KB (KB equals 1024 bytes) and can be read, written, or executed. An exception or interrupt can occur if data operands or instructions attempt to wrap around the end of a segment (for example, a word with its low-order byte at offset hex FFFF and its high-order byte at hex 0000). If, in the real-address mode, the information contained in the segment does not use the full 64KB, the unused end of the segment can be overlaid by another segment to reduce physical memory requirements.

# **Protected Virtual Address Mode**

The protected virtual address mode (hereafter called protected mode) offers extended physical and virtual memory address space, memory protection mechanisms, and new operations to support operating systems and virtual memory.

The protected mode provides a virtual address space of 1GB for each task mapped into a 16MB physical address space. The virtual

address space may be larger than the physical address space, because any use of an address that does not map to a physical memory location will cause a restartable exception.

Like the real-address mode, the protected mode uses 32-bit pointers, consisting of 16-bit selector and offset components. The selector specifies an index into a memory-resident table rather than the upper 16 bits of a real address. The 24-bit base address of the desired segment is obtained from a table in memory. The 16-bit offset is added to the segment base address to form the physical address. The system microprocessor automatically refers to the tables whenever a segment register is loaded with a selector. All instructions that load a segment register refer to the table without additional program support. Each entry in a table is 8-bytes wide.

# 80287 Math Coprocessor

The optional 80287 Math Coprocessor enables the system to perform high-speed arithmetic, logarithmic, and trigonometric operations. The coprocessor works in parallel with the microprocessor. The parallel operation decreases operating time by allowing the coprocessor to do mathematical calculations while the microprocessor continues to do other functions.

The coprocessor works with seven numeric data types, which are divided into the following three classes:

- Binary integers (three types)

- Decimal integers (one type)

- Real numbers (three types).

# **Programming Interface**

The coprocessor offers extended data types, registers, and instructions to the microprocessor. The coprocessor has eight 80-bit registers, which provide the equivalent capacity of forty 16-bit registers. This register space allows constants and temporary results to be held in registers during calculations, thus reducing memory access, improving speed, and increasing bus availability. The register space can be used as a stack or as a fixed register set. When used as a stack, only the top two stack elements are operated on.

| Data Type                                     | Bits       | Significant<br>Digits<br>(Decimal) | Approximate Range (Decimal)                                 |

|-----------------------------------------------|------------|------------------------------------|-------------------------------------------------------------|

| Word Integer                                  | 16         | 4                                  | $-32,768 \le x \le +32,767$                                 |

| Short Integer                                 | 32         | 9                                  | -2 x 10 <sup>9</sup> ≤ x ≤ +2 x 10 <sup>9</sup>             |

| Long Integer                                  | 64         | 19                                 | $-9 \times 10^{18} \le x \le +9 \times 10^{18}$             |

| Packed Decimal                                | 80         | 18                                 | -999 ≤ x ≤ +999 (18 digits)                                 |

| Short Real *                                  | 32         | 6 - 7                              | 8.43 x 10 <sup>-37</sup> ≤ x ≤ 3.37 x 10 <sup>38</sup>      |

| Long Real *                                   | 64         | 15 - 16                            | 4.19 x 10 <sup>-307</sup> ≤ x ≤ 1.67 x<br>10 <sup>308</sup> |

| Temporary Real **                             | 80         | 19                                 | 3.4 x 10 <sup>-4932</sup> ≤ x ≤ 1.2 x<br>10 <sup>4932</sup> |

| * The short-real and<br>double-precision data | -          | data types corre                   | espond to the single-precision and                          |

| ** The temporary-rea<br>Type.                 | l data typ | e corresponds to                   | the extended-precision data                                 |

The following figure shows representations of large and small numbers in each data type.

Figure 1. 80287 Data Types

### **Hardware Interface**

The coprocessor uses the same clock generator as the microprocessor and operates in the asynchronous mode. The coprocessor is wired so that it functions as an I/O device through I/O port addresses hex 00F8, 00FA, and 00FC. The microprocessor sends opcodes and operands through these I/O ports. It also receives and stores results through the same I/O ports. The coprocessor 'busy' signal informs the microprocessor that it is executing; the microprocessor Wait instruction forces the microprocessor to wait until the coprocessor is finished executing.

The coprocessor detects six different exception conditions that can occur during instruction execution:

- Invalid operation

- Denormal operand

- Zero-divide

- Overflow

- Underflow

- Precision.

If the appropriate exception-mask bit within the coprocessor is not set, the coprocessor activates the 'error' signal. The 'error' signal generates a hardware interrupt (IRQ 13) causing the 'busy' signal to be held in the busy state. The 'busy' signal may be cleared by an 8-bit I/O Write command to address hex 00F0, with D7 through D0 equal to 0. This action also clears IRQ 13.

The power-on self-test code in the system ROM enables IRQ 13 and sets up its vector to point to a routine in ROM. The ROM routine clears the 'busy' signal latch and then transfers control to the address pointed to by the nonmaskable interrupt (NMI) vector. This maintains code compatibility across the IBM Personal Computer and Personal System/2 product lines. The NMI handler reads the coprocessor status to determine if the coprocessor generated the NMI. If it was not generated by the coprocessor, control is passed to the original NMI handler.

The coprocessor has two operating modes: real-address mode and protected mode. They are similar to the two modes of the microprocessor. The coprocessor is in the real-address mode if reset by a power-on reset, system reset, or I/O write operation to port hex 00F1. This mode is compatible with the 8087 Math Coprocessor used in IBM Personal Computers. The coprocessor is placed in the protected mode by executing the SETPM ESC instruction. It is placed back in the real-address mode by an I/O write operation to port hex 00F1, with D7 through D0 equal to 0.

Detailed information for the internal functions of the 80287 Math Coprocessor is in the books listed in the Bibliography. Also see "Compatibility" for more information.

# 80386 Microprocessor

The 80386 microprocessor subsystem has the following:

- 32-bit address

- 32-bit data interface

- Extensive instruction set, including string I/O

- Hardware fixed-point multiply and divide

- Three operational modes:

- Real Address

- Protected Virtual Address

- Virtual 8086.

- 4GB of physical address space

- 8 general-purpose 32-bit registers

- 64TB (TB equals 1,099,511,627,776 or 2<sup>40</sup> bytes) of total virtual-address space.

## **Real Address Mode**

In the real-address mode, the address space of the system microprocessor is a contiguous array of up to 1MB. The system microprocessor generates 20-bit physical addresses to address memory.

The segment portion of the pointer is interpreted as the upper 16 bits of a 20-bit segment address; the lower 4 bits are always 0. Therefore, segment addresses begin on multiples of 16 bytes.

All segments in the real-address mode are 64KB and can be read, written, or executed. An exception or interrupt can occur if data operands or instructions attempt to wrap around the end of a segment (for example, a word with its low-order byte at offset hex FFFF and its high-order byte at hex 0000). If, in the real-address mode, the information contained in the segment does not use the full 64KB, the unused end of the segment can be overlaid by another segment to reduce physical memory requirements.

# **Protected Virtual Address Mode**

The protected virtual-address mode offers extended physical and virtual memory address space, memory protection mechanisms, and new operations to support operating systems and virtual memory.

The protected mode provides up to 64TB of virtual address space for each task mapped into a 4GB physical address space.

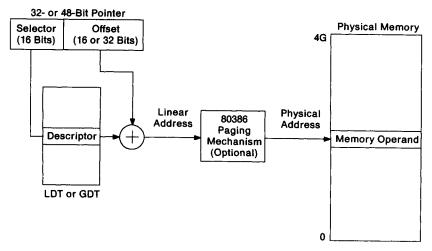

From a programmer's point of view, the main difference between the real-address mode and protected mode is the increased address space and the method of calculating the base address. The protected mode uses 32- or 48-bit pointers, consisting of 16-bit selector and 16-or 32-bit offset components. The selector specifies an index into one of two memory-resident tables, the global descriptor table (GDT) or the local descriptor table (LDT). These tables contain the 32-bit base address of a given segment. The 32-bit effective offset is added to the segment base address to form the physical address. The system microprocessor automatically refers to the tables whenever a segment register is loaded with a selector. All instructions that load

a segment register refer to the memory-resident tables without additional program support. The memory-resident tables contain 8-byte values called descriptors.

The paging option provides an additional way of managing memory in the very large segments of the 80386. Paging operates in the protected mode only, beneath segmentation. The paging mechanism translates the protected linear address (which comes from the segmentation unit) into a physical address. When paging is not enabled, the physical address is the same as the linear address. The following figure shows the 80386 addressing mechanism.

Figure 2. 80386 Addressing

# Virtual 8086 Mode

The virtual-8086 mode ensures compatibility of programs written for 8086- and 8088-based systems by establishing a protected 8086 environment within the 80386 multitasking framework.

Since the address space of an 8086 is limited to 1MB, the logical addresses generated by the virtual-8086 mode lie within the first 1MB of the 80386 linear address space. To support multiple virtual-8086 tasks, paging can be used to give each virtual-8086 task a 1MB address space anywhere in the 80386 physical address space.

On a task-by-task basis, the value of the virtual-8086 flag (VM86 flag in the Flags register) determines whether the 80386 behaves as an 80386 or as an 8086. Some instructions, such as Clear Interrupt Flag, can disrupt all operations in a multitasking environment. The 80386 raises an exception when a virtual-8086 mode task attempts to execute an I/O instruction, interrupt-related instruction, or other sensitive instruction. Anytime an exception or interrupt occurs, the 80386 leaves the virtual 8086 mode, making the full resources of the 80386 available to an interrupt handler or exception handler. These handlers can determine if the source of the exception was a virtual-8086 mode task by inspecting the VM86 flag in the Flags image on the stack. If the source is a virtual-8086 mode task, the handler calls on a routine in the operating system to simulate an 8086 instruction and return to the virtual-8086 mode.<sup>1</sup>

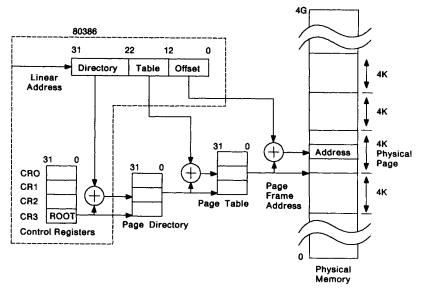

# 80386 Paging Mechanism

The 80386 uses two levels of tables to translate the linear address from the segmentation unit into a physical address. There are three components to the paging mechanism:

- Page directory

- Page tables

- Page frame (the page itself).

The figure on the following page shows how the two-level paging mechanism works.

<sup>1</sup> The routine in the operating system, called a virtual machine monitor, simulates a limited number of 8086 instructions.

Figure 3. Paging Mechanism

CR2 is the Page-Fault Linear-Address register. It holds the 32-bit linear address that caused the last detected page fault.

CR3 is the Page Directory Physical Base Address register. It contains the physical starting address of the page directory.

The page directory is 4KB and allows up to 1024 page-directory entries. Each page-directory entry contains the address of the next level of tables, the page tables, and information about the page tables. The upper 10 bits of the linear address (A22 through A31) are used as an index to select the correct page-directory entry.

Each page table is 4KB and holds up to 1024 page-table entries. Page-table entries contain the starting address of the page frame and statistical information about the page. Address bits A12 through A21 are used as an index to select one of the 1024 page-table entries. The upper 20 bits of the page-frame address (from the page-table entry) are linked with the lower 12 bits of the linear address to form the physical address. The page-frame address bits become the most-significant bits; the linear-address bits become the least-significant bits.

# 80387 Math Coprocessor

The optional 80387 Math Coprocessor enables the system to perform high-speed arithmetic, logarithmic, and trigonometric operations. The 80387 effectively extends the 80386 register and instruction set for existing data types and also adds several new data types. The following figure shows the four data type classifications and the instructions associated with each.

| Classification    | Size            | Instructions                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Integer           | 16, 32, 64 Bits | Load, Store, Compare, Add, Subtract,<br>Multiply, Divide                                                                                                                                                                                                                                                                                           |

| Packed BCD*       | 80 Bits         | Load, Store                                                                                                                                                                                                                                                                                                                                        |

| Real              | 32, 64 Bits     | Load, Store, Compare, Add, Subtract,<br>Multiply, Divide                                                                                                                                                                                                                                                                                           |

| Temporary Real    | 80 Bits         | Add, Subtract, Multiply, Divide, Square<br>Root, Scale, Remainder, Integer Part,<br>Change Sign, Absolute Value, Extract<br>Exponent and Significand, Compare,<br>Examine, Test, Exchange Tangent,<br>Arctangent, $2^{x} - 1$ , $Y^{*}Log_{2}$ (X+1),<br>$Y^{*}Log_{2}$ (X), Load Constant (0.0, $\pi$ , etc.),<br>Sine, Cosine, Unordered Compare |

| * BCD = Binary-co | oded decimal    |                                                                                                                                                                                                                                                                                                                                                    |

Figure 4. Data Type Classifications and Instructions

The 80386/80387 configuration fully conforms to the ANSI<sup>2</sup> and IEEE<sup>3</sup> floating-point standard and are upward, object-code compatible from 80286/80287- and 8086/8087-based systems.

<sup>2</sup> American National Standards Institute

<sup>3</sup> Institute of Electrical and Electronics Engineers

# 80387 To 80486 Math Coprocessor Compatibility

The 80387 floating-point coprocessor is integrated into the 80486 microprocessor. All numeric 80387 instructions are fully compatible with the 80486 floating-point unit. The 80486 microprocessor supports the 80486 floating-point error reporting modes to ensure DOS compatibility with 80386/80387 systems.

The coprocessor presence test will always show the presence of a coprocessor in the 80486.

Programs for the 80386/80387 systems that explicitly reset the

coprocessor by writing to hex 00F1 will no longer function because

the coprocessor is an integral part of the microprocessor.

Coprocessor reset or initialization must be accomplished through

FINIT/FSAVE.

| For DOS compatibility, the numeric exception bit Control Register 0 | must be set to 0.

### **Programming Interface**

The 80387 is not sensitive to the processing mode of the 80386. The 80387 functions the same whether the 80386 is executing in real-address mode, protected mode, or virtual-8086 mode. All memory access is handled by the 80386; the 80387 merely operates on instructions and values passed to it by the 80386.

All communication between the 80386 and 80387 is transparent to application programs. The 80386 automatically controls the 80387 whenever a numeric instruction is executed. All physical and virtual memory is available for storage of instructions and operands of programs that use the 80387. All memory address modes, including use of displacement, base register, index register, and scaling are available for addressing numeric operands.

The coprocessor has eight 80-bit registers. The total capacity of these eight registers is equivalent to twenty 32-bit registers. This register space allows constants and temporary results to be held in registers during calculations, thus reducing memory access, improving speed, and increasing bus availability. The register space can be used as a stack or as a fixed register set. When it is used as a stack, only the top two stack elements are operated on.

The following figure shows the seven data types supported by the 80387 Math Coprocessor.

| Data Type                              | Range               | Precision                      |

|----------------------------------------|---------------------|--------------------------------|

| Word Integer                           | 104                 | 16 Bits                        |

| Short Integer                          | 10 <sup>9</sup>     | 32 Bits                        |

| Long Integer                           | 10 <sup>19</sup>    | 64 Bits                        |

| Packed BCD                             | 10 <sup>18</sup>    | 18 Digits ( 2 digits per byte) |

| Single Precision<br>(Short Real)       | 10 <sup>±38</sup>   | 24 Bits                        |

| Double Precision<br>(Long Real)        | 10 <sup>±308</sup>  | 53 Bits                        |

| Extended Precision<br>(Temporary Real) | 10 <sup>±4932</sup> | 64 Bits                        |

Figure 5. 80387 Data Types

# **Hardware Interface**

The 80387 Math Coprocessor uses the same clock generator as the 80386 system microprocessor. The coprocessor is wired so that it functions as an I/O device through I/O port addresses hex 00F8, 00FA, and 00FC. The system microprocessor sends opcodes and operands through these I/O ports. The coprocessor 'busy' signal informs the system microprocessor that it is executing an instruction; the system microprocessor to wait instruction forces the system microprocessor to wait until the coprocessor is finished executing the instruction.

The coprocessor detects six different exception conditions that can occur during instruction execution:

- Invalid operation

- Denormal operand

- Zero-divide

- Overflow

- Underflow

- Precision.

If the appropriate exception mask bit within the coprocessor is not set, the coprocessor activates the 'error' signal. The 'error' signal generates a hardware interrupt (IRQ 13) causing the 'busy' signal to be held in the busy state. The 'busy' signal can be cleared by an 8-bit I/O Write command to address hex 00F0, with D7 through D0 equal to 0. This action also clears IRQ 13.

The power-on self-test code in the system ROM enables IRQ 13 and sets up its vector to point to a routine in ROM. The ROM routine clears the 'busy' signal latch and then transfers control to the address pointed to by the (NMI) vector. This maintains code compatibility across the IBM Personal Computer and Personal System/2 product lines. The NMI handler reads the status of the coprocessor to determine if the coprocessor generated the NMI. If it was not generated by the coprocessor, control is passed to the original NMI handler.

Detailed information about the internal functions of the 80387 Math Coprocessor is in the books listed in the Bibliography. Also see "Compatibility" for more information.

# 80486 Microprocessor

| The 80486 microprocessor subsystem has the following:

- 32-bit address

- 32-bit data interface

- Extensive instruction set, including string I/O

- Hardware fixed-point multiply and divide

- Three operational modes:

- Real Address

- Protected Virtual Address

- Virtual 8086

1

- 4GB of physical address space

- 8 general-purpose 32-bit registers

- 64TB of total virtual-address space

- Internal 8KB, set-associative cache with controller

- Internal 80387 coprocessor.

| The 80486 microprocessor is compatible with the 80386 in the | following areas:

- Real Address Mode

- Protected Virtual Address Mode

- Virtual 8086 Mode

- 80386 Paging Mechanism

- All published 80386 instructions

- All published 80387 instructions.

The complete 80387 Math Coprocessor instruction set and register set have been included in the 80486 as a floating-point unit. No I/O cycles are executed during floating-point instructions. The 80486 microprocessor is 80386/80387 compatible except for resets to the floating-point unit. Software must use FINIT/FSAVE to reset the floating-point unit (math coprocessor). The instruction and data pointers are set to zero after FINIT/FSAVE.

# Cache Control

The 80486 microprocessor contains an 8KB integrated cache for code and data. The cache is managed in two ways, and the operation of the cache has no effect on the operation of any program.

| The cache is managed by bit 30 - Cache Disable (CD) and bit 29 - I Not Write Through (NW) in Control Register 0 (CR0):

| Bit 30<br>CD | Bit 29<br>NW | Operating Mode                                                                       |

|--------------|--------------|--------------------------------------------------------------------------------------|

| 1            | 1            | Cache fills disabled, write-through and invalidate disabled                          |

| 1            | 0            | Cache fills disabled, write-through and invalidate enabled                           |

| 0            | 1            | Reserved                                                                             |

| 0            | 0            | Cache fills enabled, write-through and invalidate<br>enabled (Normal operating mode) |

| Figure 6. Control Register 0

# Cache Paging Control

The page-write-through (PWT) bit and the page-cache-disabled (PCD) bit are two new bits defined in entries in both levels of the page table structure, the page-directory table and the page-table entry, and in Control Register 3.

The PWT bit (bit 4) controls cache write policy. When this bit is set to 1, a write-through policy for the current 4KB page is defined. When this bit is set to 0, it allows the possibility of write-back policy. This bit is ignored internally because the 80486 microprocessor has a write-through-only cache. The PWT bit can be used to control the write policy of a second-level (external) cache.

The PCD bit (bit 3),in conjunction with the KEN# (cache enabled) input

signal and the cache-enable and write-transparent bits in Control

Register 0 (CR0), controls the ability of cache. When this bit is set to

1, caching is disabled for the 4KB page regardless of the KEN#,

cache-enable bit, and write-through bit. These two bits are also

driven external to the processor during memory access to manage a

second-level cache, if one exists.

The page-write-through and page-cache-disable bits for a bus cycle

are obtained either from Control Register 3, the page-directory entry,

or the page-table entry, depending on the type of cycle performed.

# Page Protection Feature

The 80486 microprocessor has a new protection feature. The

write-protect (WP) bit in CR0 has been added to the 80486

microprocessor to protect read-only pages from supervisor write

accesses. The 80386 microprocessor allows a read-only page to be

written from protection level 0, 1, or 2. When the WP bit is set to 0,

the 80486 microprocessor is in the 80386-compatible mode. When the

WP bit is set to 0, the supervisor write access to a read-only page

(Read/Write is set to 0) causes a page fault (exception 14).

The write-protect bit has a new feature. This feature involves the use of three new bits in CR0:

- User/Supervisor U/S

- Read/Write R/W

- Write/Protect WP.

The compatible protection feature is described by the following table.

| U/S | R/W | WP | User Access        | Supervisor Access  |

|-----|-----|----|--------------------|--------------------|

| 0   | 0   | 0  | None               | Read/Write/Execute |

| 0   | 1   | 0  | None               | Read/Write/Execute |

| 1   | 0   | 0  | Read/Execute       | Read/Write/Execute |

| 1   | 1   | 0  | Read/Write/Execute | Read/Write/Execute |

Figure 7. 80386 Compatible Operation

The new protection feature is given by the following table.

| U/S | R/W | WP | User Access        | Supervisor Access  |

|-----|-----|----|--------------------|--------------------|

| 0   | 0   | 1  | None               | Read/Execute       |

| 0   | 1   | 1  | None               | Read/Write/Execute |

| 1   | 0   | 1  | Read/Execute       | Read/Execute       |

| 1   | 1   | 1  | Read/Write/Execute | Read/Write/Execute |

| Figure 8. 80486 Protection Operation

## New Alignment Check

| The Flag register in the 80486 microprocessor contains a new bit not | available in the 80386. The new bit, alignment check, is bit 18 of the | Flag register and enables fault reporting on accesses to misaligned | data (through interrupt 17 with an error code 0).

When alignment check is set to 1, it enables fault reporting if memory

reference is to a misaligned address. A misaligned address is a

word access to an odd address, a doubleword access to an address

not on a doubleword boundary, or an 8-byte reference to an address

that is not on a 64-bit boundary.

| Alignment faults are generated only by a program running at | privilege level 3. The alignment-check bit is ignored at privilege | levels 0, 1, and 2.

The alignment-check bit is conditioned by a new alignment mask bit, defined as bit 18 in Control Register 0. The alignment-mask bit controls whether the alignment-check bit in the Flag register can allow an alignment fault. When the alignment-mask bit is set to 0, the alignment-check bit is disabled and compatible with the 80386 microprocessor. When the alignment-mask bit is set to 1, the alignment-check bit is enabled.

### New Instructions

l

In addition, the 80486 has six unique instructions that control cache operation:

- Byte Swap (BSWAP)

- Compare and Exchange (CMPXCHG)

- Exchange-and-Add (XADD)

- Invalidate Data Cache (INVD)

- Invalidate TLBN Entry (INVLPG).

- Write-Back and Invalidate Data Cache (WBINVD).

# **80286 Microprocessor Instruction Set**

### **Data Transfer**

### MOV = Move

**Register to Register/Memory**

| 1000100w | mod reg r/m |

|----------|-------------|

|          |             |

#### Register/Memory to Register

1000101w mod reg r/m

#### Immediate to Register/Memory

| 1100011w | mod 0 0 0 r/m | data | data if w = 1 |  |

|----------|---------------|------|---------------|--|

|          |               |      |               |  |

#### Immediate to Register

| 1011 wreg data data if w = 1 | 1011 wreg data data if w | = 1 |

|------------------------------|--------------------------|-----|

|------------------------------|--------------------------|-----|

#### Memory to Accumulator

| 101000w | addr-low | addr-high |

|---------|----------|-----------|

|         |          |           |

#### Accumulator to Memory

| 1010001w | addr-low | addr-high |

|----------|----------|-----------|

|          |          |           |

#### **Register/Memory to Segment Register**

| 10001110 | mod 0 reg r/m |

|----------|---------------|

|          |               |

#### Segment Register to Register/Memory

| 10001100 | mod 0 reg r/m |

|----------|---------------|

|          |               |

### PUSH = Push

Memory

| 11111111 | mod 1 1 0 r/w |

|----------|---------------|

Register

01010 reg

#### Segment Register

000 reg 110

#### Immediate

| 011010s0 | data | data if s = 0 |

|----------|------|---------------|

| 01101080 | uala | data in o o   |

### PUSHA = Push All

01100000

#### POP = Pop

Register/Memory

| 10001111 | mod 0 0 0 r/m |

|----------|---------------|

|          |               |

Register

01011 reg

#### Segment Register

| 000 reg 111 | reg ≠ 0 1 |

|-------------|-----------|

|             |           |

### POPA = Pop All

01100001

### XCHG = Exchange

### Register/Memory with Register

| 1000011w | mod reg r/m   |

|----------|---------------|

| 1000011₩ | inioa reg r/m |

### **Register with Accumulator**

10010 reg

### IN = Input From

Fixed Port

| 1110010w | port |

|----------|------|

|          |      |

Variable Port

1110110w

### OUT = Output To

Fixed Port

1110011w port

Variable Port

1110111w

### XLAT = Translate Byte to AL

11010111

### LEA - Load EA to Register

10001101 mod reg r/m

### LDS = Load Pointer to DS

11000101 mod reg r/m mod ≠ 11

### LES = Load Pointer to ES

11000100 mod reg r/m mod ≠ 11

### LAHF = Load AH with Flags

### SAHF = Store AH with Flags

10011110

#### **PUSHF** = **Push** Flags

10011100

### POPF = Pop Flags

10011101

# Arithmetic

### ADD = Add

#### Register/Memory with Register to Either

000000 dw mod reg r/m

#### Immediate to Register/Memory

|          | ······································ |      | · · · · · · · · · · · · · · · · · · · |

|----------|----------------------------------------|------|---------------------------------------|

| 100000sw | mod 0 0 0 r/m                          | data | data if sw = 0 1                      |

Immediate to Accumulator

| 0000010w data data if w = | 1 |

|---------------------------|---|

|---------------------------|---|

### ADC = Add with Carry

#### **Register/Memory with Register to Either**

| 000100dw | mod reg r/m |

|----------|-------------|

|----------|-------------|

#### Immediate to Register/Memory

| 100000sw mod 010r/m data data if sv | = 0 1 |

|-------------------------------------|-------|

|-------------------------------------|-------|

#### Immediate to Accumulator

| 0001010w | data | data if w = 1 |

|----------|------|---------------|

|----------|------|---------------|

#### **INC = Increment**

#### **Register/Memory**

Register

01000 reg

### SUB = Subtract

### Register/Memory with Register to Either

001010dw mod reg r/m

#### Immediate from Register/Memory

| 100000sw |               |      |                 | Ē |

|----------|---------------|------|-----------------|---|

| 1000005w | mod 1 0 1 r/m | data | data if sw = 01 | Ĺ |

### Immediate from Accumulator

| 0010110w | data | data if w = 1 |

|----------|------|---------------|

|----------|------|---------------|

### SBB = Subtract with Borrow

### Register/Memory with Register to Either

000110dw mod reg r/m

#### Immediate from Register/Memory

| 100000sw | mod 0 1 1 r/m | data | data if sw = 0 1 |

|----------|---------------|------|------------------|

|          |               |      |                  |

### Immediate from Accumulator

| 0001110w | data | data if w = 1 |

|----------|------|---------------|

|          |      |               |

### DEC = Decrement

Register/Memory

1111111 mod 0 0 1 r/m

Register

01001 reg

### CMP - Compare

#### Register/Memory with Register

| 0011101w | mod reg r/m |

|----------|-------------|

#### Register with Register/Memory

| 0011100w | mod reg r/m |

|----------|-------------|

#### Immediate with Register/Memory

| 100000sw | mod 1 1 1 r/m | data | data if sw = 01 |

|----------|---------------|------|-----------------|

| 1000003# |               |      | dala non o .    |

#### Immediate with Accumulator

| 0011110w | data | data if w = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      | And a second sec |

### NEG = Change Sign

| 1111011w | mod 0 1 1 r/m |

|----------|---------------|

|          |               |

### AAA - ASCII Adjust for Add

00110111

### DAA = Decimal Adjust for Add

### AAS = ASCII Adjust for Subtract

### DAS = Decimal Adjust for Subtract

### MUL = Multiply (Unsigned)

| 1111011w | mod 1 0 0 r/m |

|----------|---------------|

|          |               |

### IMUL = Integer Multiply (Signed)

| 1111011  |               |

|----------|---------------|

| 1111011w | mod 1 0 1 r/m |

### IIMUL = Integer Immediate Multiply (Signed)

| 011010s1 | mod reg r/m | data | data if s = 0 |

|----------|-------------|------|---------------|

|          |             |      |               |

### DIV = Divide (Unsigned)

| 1111011w | mod 1 1 0 r/m |

|----------|---------------|

|          |               |

### IDIV = Integer Divide (Signed)

| 1111011w | mod 1 1 1 r/m |

|----------|---------------|

|          |               |

# AAM = ASCII Adjust for Multiply

| 11010100 | 00001010 |

|----------|----------|

### AAD = ASCII Adjust for Divide

11010101 00001010

### CBW = Convert Byte to Word

10011000

### CWD = Convert Word to Doubleword

# Logic

### Shift/Rotate Instructions

#### Register/Memory by 1

| 1101000w | mod T T T r/m |

|----------|---------------|

|          | 1             |

#### Register/Memory by CL

| 1101001w | mod T T T r/m |

|----------|---------------|

|          |               |

### Register/Memory by Count

| 1100000w | modiTTTr/m | count |

|----------|------------|-------|

|----------|------------|-------|

| TTT | Instruction |  |

|-----|-------------|--|

| 000 | ROL         |  |

| 001 | ROR         |  |

| 010 | RCL         |  |

| 011 | RCR         |  |

| 100 | SHL/SAL     |  |

| 101 | SHR         |  |

| 111 | SAR         |  |

### AND = And

#### Register/Memory and Register to Either

| 001000dw | mod reg r/m |

|----------|-------------|

|          |             |

#### Immediate to Register/Memory

| 100000w | mod 100 r/m | data | data if w = 1 |

|---------|-------------|------|---------------|

|         |             |      |               |

#### Immediate to Accumulator

|  | 0010010w | data | data if w = 1 |

|--|----------|------|---------------|

|--|----------|------|---------------|

# TEST = AND Function to Flags; No Result

### Register/Memory and Register

| -        |             |

|----------|-------------|

| 1000010w | mod reg r/m |

#### Immediate Data and Register/Memory

| 1111011w | mod 0 0 0 r/m | data | data if w = 1 |

|----------|---------------|------|---------------|

|          |               |      | data ii w = 1 |

#### Immediate Data and Accumulator

| 1010100w | data | data if w = 1 |

|----------|------|---------------|

|          |      |               |

### Or = Or

#### **Register/Memory and Register to Either**

| 000010dw | mod reg r/m |

|----------|-------------|

|          |             |

#### Immediate to Register/Memory

| 1000000w | mod 0 0 1 r/m | data |               |

|----------|---------------|------|---------------|

|          |               | uala | data if w = 1 |

|          |               |      |               |

#### Immediate to Accumulator

| 0000110w | data | data if w = 1 |

|----------|------|---------------|

|          |      |               |

### XOR = Exclusive OR

#### **Register/Memory and Register to Either**

001100dw

mod reg r/m

### Immediate to Register/Memory

| 100000w | mod 1 1 0 r/m | data | data if w = 1 |

|---------|---------------|------|---------------|

|         |               |      |               |

#### Immediate to Accumulator

| 0011010w data data if w = 1 | 0011010w |

|-----------------------------|----------|

|-----------------------------|----------|

### NOT = Invert Register/Memory

1111011w mod010r/m

### **String Manipulation**

### MOVS - Move Byte Word

1010010w

### CMPS B/W = Compare Byte/Word

### SCAS = Scan Byte/Word

### LODS - Load Byte/Word to AL/AX

### STOS = Store Byte/Word from AL/AX

1010101w

### INS = Input Byte/Word from DX Port

0110110w

### OUTS = Output Byte/Word to DX Port

### **REP/REPNE, REPZ/REPNZ = Repeat String**

### Repeat Move String

| 11110011 | 1010010w |

|----------|----------|

### Repeat Compare String (z/Not z)

| 1111001z | 1010011w |

|----------|----------|

|          | 10100111 |

### Repeat Scan String (z/Not z)

| 1111001z | 1010111w |

|----------|----------|

|          |          |

#### Repeat Load String

| 11110011 | 1010110w |

|----------|----------|

|          |          |

#### **Repeat Store String**

| 11110011 | 1010101w |

|----------|----------|

|          |          |

### Repeat Input String

| 11110011 | 0110110w |

|----------|----------|

|          | 0110110₩ |

### **Repeat Output String**

| 11110011 | 0110111w |

|----------|----------|

|          | 0110111₩ |

# **Control Transfer**

### CALL = Call

**Direct within Segment**

| 11101000 | disp-low | disp-high |

|----------|----------|-----------|

|          |          |           |

#### **Register/Memory Indirect within Segment**

| 11111111 | mod 0 1 0 r/m |

|----------|---------------|

|          |               |

#### Direct Intersegment

| 10011010 | Segment Offset | Segment<br>Selector |

|----------|----------------|---------------------|

|          |                |                     |

### Indirect Intersegment

| 11111111 | mod 0 1 1 r/m (mod ≠ 11) |

|----------|--------------------------|

### JMP = Unconditional Jump

Short/Long

| 11101011 | disp-low |

|----------|----------|

|          |          |

Direct within Segment

| 11101001 | disp-low | disp-high |

|----------|----------|-----------|

|          |          |           |

#### **Register/Memory Indirect within Segment**

| 1111111 | mod 100 r/m |

|---------|-------------|

|         |             |

#### **Direct Intersegment**

| 11101010 | Segment Offset | Segment<br>Selector |

|----------|----------------|---------------------|

|----------|----------------|---------------------|

Indirect Intersegment

| 11111111 |                          |

|----------|--------------------------|

|          | mod 1 0 1 r/m (mod ≠ 11) |

|          |                          |

|          |                          |

### **RET = Return from Call**

#### Within Segment

11000011

#### Within Segment Adding Immediate to SP

| 11000010 | data-low | data-high |

|----------|----------|-----------|

|          |          |           |

Intersegment

11001011

#### Intersegment Adding Immediate to SP

| data-high data-bigh | 11001010 | data-low | data-high |

|---------------------|----------|----------|-----------|

|---------------------|----------|----------|-----------|

### JE/JZ = Jump on Equal/Zero

| 01110100 | disp |

|----------|------|

|          | ulop |

### JL/JNGE = Jump on Less/Not Greater, or Equal

| 01111100 | disp |

|----------|------|

|          |      |

|          |      |

### JLE/JNG = Jump on Less, or Equal/Not Greater

01111110 disp

### JB/JNAE = Jump on Below/Not Above, or Equal

| 01110010 | disp |

|----------|------|

|          | F    |

### JBE/JNA = Jump on Below, or Equal/Not Above

| 01110110 | disp |

|----------|------|

|          |      |

### JP/JPE = Jump on Parity/Parity Even

| 01111010 | disp  |

|----------|-------|

| 01111010 | laish |

#### **JO** = Jump on Overflow

|      |     |     | - í |      |  |  |

|------|-----|-----|-----|------|--|--|

| 1 01 | 110 | ոոո | - 1 | disp |  |  |

|      |     |     |     | ulop |  |  |

|      |     |     |     |      |  |  |

#### JS = Jump on Sign

#### JNE/JNZ = Jump on Not Equal/Not Zero

| 0111 | 0101 | disp |  | 1 |

|------|------|------|--|---|

|      |      |      |  |   |

#### JNL/JGE = Jump on Not Less/Greater, or Equal

| 01111101 | disp |

|----------|------|

|          |      |

#### JNLE/JG = Jump on Not Less, or Equal/Greater

01111111 disp

### JNB/JAE = Jump on Not Below/Above, or Equal

01110011 disp

#### JNBE/JA = Jump on Not Below, or Equal/Above

01110111 disp

### JNP/JPO = Jump on Not Parity/Parity Odd

01111011 disp

### JNO = Jump on Not Overflow

01110001 disp

### JNS = Jump on Not Sign

01111001 disp

### LOOP = Loop CX Times

11100010 disp

### LOOPZ/LOOPE = Loop while Zero/Equal

11100001 disp

### LOOPNZ/LOOPNE = Loop while Not Zero/Not Equal

11100000 disp

### JCXZ = Jump on CX Zero

11100011 disp

### ENTER = Enter Procedure

| 11001000 | data-low | data-high | ] |

|----------|----------|-----------|---|

|----------|----------|-----------|---|

### LEAVE = Leave Procedure

11001001

## INT = Interrupt

**Type Specified**

| 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 |  |  |

|---|---|---|---|---|---|---|---|--|--|

Туре 3

11001100

## INTO = Interrupt on Overflow

11001110

## **IRET = Interrupt Return**

11001111

# BOUND = Detect Value Out of Range

01100010 mod reg r/m

# **Processor Control**

## CLC = Clear Carry

## **CMC** = Complement Carry

11110101

## STC = Set Carry

11111001

## CLD = Clear Direction

11111100

## STD = Set Direction

## CLI = Clear Interrupt

11111010

# STI = Set Interrupt Enable Flag

| <br>_ |   | _ | _ | _ | _ | _ |   |  |

|-------|---|---|---|---|---|---|---|--|

| 1     | 1 | 1 | 1 | 1 | 0 | 1 | 1 |  |

|       |   |   |   |   |   |   |   |  |

HLT = Halt

11110100

WAIT = Wait

10011011

# LOCK = Bus Lock Prefix

11110000

## CTS = Clear Task Switched Flag

00001111 00000110

# ESC = Processor Extension Escape

| 11011TTT | mod LLL r/m |

|----------|-------------|

|          |             |

# **Protection Control**

## LGDT = Load Global Descriptor Table Register

| 00001111 | 00000001 | mod 0 1 0 r/m |

|----------|----------|---------------|

|          |          |               |

## SGDT = Store Global Descriptor Table Register

| 00001111 | 00000001 | mod 0 0 0 r/m |

|----------|----------|---------------|

|          |          |               |

## LIDT = Load Interrupt Descriptor Table Register

|          | · · · · · · · · · · · · · · · · · · · |               |

|----------|---------------------------------------|---------------|

| 00001111 | 00000001                              | mod 0 1 1 r/m |

## SIDT = Store Interrupt Descriptor Table Register

| 00001111 | 00000001 | mod 0 0 1 r/m |

|----------|----------|---------------|

|          |          |               |

## LLDT = Load Local Descriptor Table Register from Register/Memory

| 00001111 | 00000000 | mod 0 1 0 r/m |

|----------|----------|---------------|

|          |          |               |

## SLDT = Store Local Descriptor Table Register from Register/Memory

| 00004444 |          |               |   |

|----------|----------|---------------|---|

| 00001111 | 00000000 | mod 0 0 0 r/m | l |

## LTR = Load Task Register from Register/Memory

| 00001111 | 00000000 | mod 0 1 1 r/m |

|----------|----------|---------------|

|          |          |               |

## STR = Store Task Register to Register/Memory

| 00001111 | 00000000 | mod 0 0 1 r/m |

|----------|----------|---------------|

## LMSW = Load Machine Status Word from Register/Memory

| 00001111 | 00000001 | mod 1 1 0 r/m |

|----------|----------|---------------|

|          |          |               |

## SMSW = Store Machine Status Word

| 00001111 | 00000001 | mod 1 0 0 r/m |

|----------|----------|---------------|

|----------|----------|---------------|

# LAR = Load Access Rights from Register/Memory

| 00001111 | 00000010 | mod reg r/m |

|----------|----------|-------------|

|          | 0000010  | mou reg i/m |

# LSL = Load Segment Limit from Register/Memory

| 00001111 | 00000011 | mod reg r/m |

|----------|----------|-------------|

|----------|----------|-------------|

# ARPL = Adjust Requested Privilege Level from Register/Memory

| 01100011 | mod reg r/m |

|----------|-------------|

|          | mourey min  |

# VERR = Verify Read Access; Register/Memory

| 00001111 00000000 mod 10 | 0 r/m |

|--------------------------|-------|

|--------------------------|-------|

### VERW = Verify Write Access

| 00001111 0000000 mod 101r/ | n |

|----------------------------|---|

|----------------------------|---|

The effective address (EA) of the memory operand is computed according to the mod and r/m fields:

If mod = 11, then r/m is treated as a reg field. If mod = 00, then disp = 0, disp-low and disp-high are absent. If mod = 01, then disp = disp-low sign-extended to 16 bits, disp-high is absent. If mod = 10, then disp = disp-high:disp-low. If r/m = 000, then EA = (BX) + (SI) + DISP If r/m = 001, then EA = (BX) + (DI) + DISP If r/m = 010, then EA = (BP) + (SI) + DISP If r/m = 011, then EA = (BP) + (DI) + DISP If r/m = 100, then EA = (BP) + (DI) + DISP If r/m = 100, then EA = (BP) + (DI) + DISP If r/m = 101, then EA = (BP) + DISP If r/m = 110, then EA = (BP) + DISP If r/m = 111, then EA = (BX) + DISP If r/m = 111, then EA = (BX) + DISP The disp field follows the second byte of the instruction (before data if required).

Note: An exception to the above statements occurs when mod = 00and r/m = 110, in which case EA = disp-high; disp-low.

## Segment Override Prefix

The 2-bit and 3-bit reg fields are defined in the following figures.

| Reg | Segment<br>Register | Reg | Segment<br>Register |  |

|-----|---------------------|-----|---------------------|--|

| 00  | ES                  | 10  | SS                  |  |

| 01  | CS                  | 11  | DS                  |  |

Figure 9. 2-Bit Register Field

| Figure 10. 3-E | Bit Register Field |  |

|----------------|--------------------|--|

| 16-Bit (w = 1) | 8-Bit (w = 0)      |  |

| 000 AX         | 000 AL             |  |

| 001 CX         | 001 CL             |  |

| 010 DX         | 010 DL             |  |

| 011 BX         | 011 BL             |  |

| 100 SP         | 100 AH             |  |

| 101 BP         | 101 CH             |  |

| 110 SI         | 110 DH             |  |

| 111 DI         | 111 BH             |  |

The physical addresses of all operands addressed by the BP register are computed using the SS Segment register. The physical addresses of the destination operands of the string primitive operations (those addressed by the DI register) are computed using the ES segment, which may not be overridden.

# 80287 Math Coprocessor Instruction Set

The following is an instruction-set summary for the 80287 Math Coprocessor.

The following figure shows abbreviations used in the summary.

| Field      | Description                  | Bit Information             |

|------------|------------------------------|-----------------------------|

| escape     | 80286 Extension Escape       | Bit Pattern = 11011         |

| MF         | Memory Format                | 00 = 32-Bit Real            |

|            |                              | 01 = 32-Bit Integer         |

|            |                              | 10 = 64-Bit Real            |

|            |                              | 11 = 16-Bit Integer         |

| ST(0)      | Current Stack Top            |                             |

| ST(i)      | ith Register Below the Stack |                             |

|            | Тор                          |                             |

| d          | Destination                  | 0 = Destination is ST(0)    |

|            |                              | 1 = Destination is ST(i)    |

| Р          | Рор                          | 0 = Nopop                   |

|            |                              | 1 = Pop ST(0)               |

| R          | Reverse*                     | 0 = Destination (op) source |

|            |                              | 1 = Source (op) destination |

| * When d = | 1, reverse the sense of R.   | . , , =======               |

Figure 11. 80287 Encoding Field Summary

# Data Transfer

## FLD = Load

Integer/Real Memory to ST(0)

escape MF 1

Long Integer Memory to ST(0)

| escape 1 1 1 | mod 1 0 1 r/m |

|--------------|---------------|

|              |               |

#### **Temporary Real Memory to ST(0)**

| escape 0 1 1 | mod 101r/m |

|--------------|------------|

|              |            |

#### BCD Memory to ST(0)

| escape 1 1 1 | mod 1 0 0 r/m |

|--------------|---------------|

|              |               |

ST(i) to ST(0)

| escape 0 0 1 | 11000ST(i) |

|--------------|------------|

| 030ap0 0 0 1 | 1100001(1) |

## FST = Store

#### ST(0) to Integer/Real Memory

| escape MF 1 | mod 0 1 0 r/m |

|-------------|---------------|

|             |               |

ST(0) to ST(i)

| escape 101 | 1 1 0 1 0 ST(i) |

|------------|-----------------|

|            |                 |

## FSTP = Store and Pop

ST(0) to Integer/Real Memory

| escape MF 1 | mod 0 1 1 r/m |

|-------------|---------------|

|             |               |

## ST(0) to Long Integer Memory

# ST(0) to Temporary Real Memory

| escape 0 1 1 | mod 1 1 1 r/m |

|--------------|---------------|

|              |               |

#### ST(0) to BCD Memory

| escape 1 1 1 | mod 1 1 0 r/m |

|--------------|---------------|

| ·            |               |

ST(0) to ST(i)

l

|  | escape 1 0 1 | 1 1 0 1 1 ST(i) |

|--|--------------|-----------------|

|--|--------------|-----------------|

# FXCH = Exchange ST(i) and ST(0)

| escape 0 0 1 | 11001ST(i) |

|--------------|------------|

|              |            |

# Comparison

## FCOM = Compare

Integer/Real Memory to ST(0)

| escape MF 0 | mod 0 1 0 r/m |

|-------------|---------------|

|             |               |

ST(i) to ST(0)

escape 0 0 0

11010ST(i)

# FCOMP = Compare and Pop

#### Integer/Real Memory to ST(0)

| escape MF 0 | mod 0 1 1 r/m |

|-------------|---------------|

ST(i) to ST(0)

| escape 0 0 0 | 1 1 0 1 1 ST(i) |

|--------------|-----------------|

|              |                 |

# FCOMPP = Compare ST(1) to ST(0) and Pop Twice

| 000000 110 | 44044004 |

|------------|----------|

| escape 110 | 11011001 |

|            |          |

|            |          |

# FTST = Test ST(0)

| escape 0 0 1 | 11100100 |

|--------------|----------|

# FXAM = Examine ST(0)

| escape 0 0 1 | 11100101 |

|--------------|----------|

## Constants

## FLDZ = Load + 0.0 into ST(0)

| escape 0 0 1 | 11101110 |

|--------------|----------|

| escape 0 0 1 |          |

# FLD1 = Load + 1.0 into ST(0)

| escape 0 0 1 | 11101000 |

|--------------|----------|

|              | 11101000 |

## **FLDPi** = Load $\pi$ into ST(0)

| escape 0 0 1 | 11101011 |

|--------------|----------|

# FLDL2T = Load log<sub>2</sub> 10 into ST(0)

escape 0 0 1 1 1 1 0 1 0 0 1

# FLDL2E = Load log<sub>2</sub> e into ST(0)

escape 0 0 1 1 1 1 0 1 0 1 0

## $FLDLG2 = Load log_{10} 2 into ST(0)$

| escape | 0.0.1 | 11101100        |

|--------|-------|-----------------|

| oscape | 001   | 1 1 1 0 1 1 0 0 |

# FLDLN2 = Load log<sub>e</sub> 2 into ST(0)

| escape | 001 | 11101101 |

|--------|-----|----------|

# Arithmetic

## FADD = Addition

Integer/Real Memory with ST(0)

| 1      |      |               |

|--------|------|---------------|

| escape | MF 0 | mod 0 0 0 r/m |

ST(i) and ST(0)

| escape dP0 | 1 1 0 0 0 ST(i) |

|------------|-----------------|

|            |                 |

## **FSUB = Subtraction**

Integer/Real Memory with ST(0)

| escape MF 0 | mod 10 R r/m |

|-------------|--------------|

|             |              |

ST(i) and ST(0)

| · · · · · · · · · · · · · · · · · · · |           |

|---------------------------------------|-----------|

| escape dP 0                           | 1110R r/m |

|                                       |           |

# FMUL = Multiplication

| Integer/Real Memory with ST(0) |               |

|--------------------------------|---------------|

| escape MF 0                    | mod 0 0 1 r/m |

ST(i) and ST(0)

| escape dP 0 | 11001r/m |

|-------------|----------|

## FDIV = Division

Integer/Real Memory with ST(0)

| escape MF 0 | mod 1 1 B r/m |

|-------------|---------------|

|             |               |

ST(i) and ST(0)

| escape dP 0 | 1111Rr/m |

|-------------|----------|

| eacape ur u |          |

|             |          |

# FSQRT = Square Root of ST(0)

| escape 0 0 1 | 11111010 |

|--------------|----------|

|              |          |

# FSCALE = Scale ST(0) by ST(1)

| escape 0 0 1 | 11111101 |

|--------------|----------|

# FPREM = Partial Remainder of ST(0) ÷ ST(1)

| escape 0 0 1 | 11111000 |

|--------------|----------|

| escape u u i |          |

## FRNDINT = Round ST(0) to Integer

| escape 0 0 1 | 11111100 |

|--------------|----------|

## FXTRACT = Extract Components of ST(0)

| escape 0 0 1 | 11110100 |

|--------------|----------|

### FABS = Absolute Value of ST(0)

| escape 0 0 1 | 11100001 |

|--------------|----------|

## FCHS = Change Sign of ST(0)

|  | escape 0 0 1 | 11100000 |

|--|--------------|----------|

|--|--------------|----------|

# **Transcendental**

### FPTAN = Partial Tangent of ST(0)

escape 0 0 1 1 1 1 1 0 0 1 0

## **FPATAN** = Partial Arctangent of ST(1) $\div$ ST(0)

escape 0 0 1 1 1 1 1 0 0 1 1

### $F2XM1 = 2^{ST(0)} -1$

| escape 0 0 1 | 11110000 |

|--------------|----------|

|              |          |

# $FYL2X = ST(1) \times Log_2 [ST(0)]$

escape 0 0 1 1 1 1 1 0 0 0 1

# $FYL2XP1 = ST(1) \times Log_2 [ST(0) + 1]$

| escape 0 0 1 | 11111001 |

|--------------|----------|

# **Processor Control**

## FINIT = Initialize NPX

| escape 0 1 1 | 11100011 |

|--------------|----------|

## **FSETPM = Enter Protected Mode**

| escape 0 1 1 | 11100100 |

|--------------|----------|

# FSTSW AX = Store Control Word

| escape 111 | 11100000 |

|------------|----------|

## FLDCW = Load Control Word

escape 0 0 1 mod 1 0 1 r/m

### **FSTCW = Store Control Word**

| escape 0 0 1 | mod 1 1 1 r/m |

|--------------|---------------|

|              |               |

## **FSTSW = Store Status Word**

escape 101 mod 111 r/m

## FCLEX = Clear Exceptions

| escape 0 1 1 | 11100010 |

|--------------|----------|

## **FSTENV = Store Environment**

| escape 0 0 1 | mod 110 r/m |

|--------------|-------------|

|--------------|-------------|

# FLDENV = Load Environment

| escape 0 0 1 | mod 1 0 0 r/m |

|--------------|---------------|

## FSAVE = Save State

| escape 101 | mod 1 1 0 r/m |

|------------|---------------|

## FRSTOR = Restore State

| escape 101 | mod 100 r/m   |

|------------|---------------|

| 0000000101 | mod i o o i/m |

### FINCSTP = Increment Stack Pointer

| escape 0 0 1 | 11110111 |

|--------------|----------|

## FDECSTP = Decrement Stack Pointer

| escape 0 0 1 | 11110110 |

|--------------|----------|

## FFREE = Free ST(I)

| escape 1 0 1 | 11000ST(i) |

|--------------|------------|

## **FNOP** = No Operation

escape 0 0 1 1 1 0 1 0 0 0 0

# Introduction to the 80386 Instruction Set

The 80386 instruction set is an extended version of the 8086 and 80286 instruction sets. The instruction sets have been extended in two ways:

- The instructions have extensions that allow operations on 32-bit operands, registers, and memory.

- A 32-bit addressing mode allows flexible selection of registers for base and index as well as index scaling capabilities (x2, x4, x8) for computing a 32-bit effective address. The 32-bit effective address yields a 4GB address range.

Note: The effective address size must be less than 64KB in the real-address or virtual-address modes to avoid an exception.

# **Code and Data Segment Descriptors**

Although the 80386 supports all 80286 Code and Data segment descriptors, there are some differences in the format. The 80286 segment descriptors contain a 24-bit base address and a 16-bit limit field, while the 80386 segment descriptors have a 32-bit base address, a 20-bit limit field, a default bit, and a granularity bit.

| 31 | 24           | 23     |        |      | 16    | 15            | 08   | 07               | 00 |   | 0           |

|----|--------------|--------|--------|------|-------|---------------|------|------------------|----|---|-------------|

|    | Segment Base | ə (SB) | ) Bits | 15-0 | )     | Segment       | Limi | t (SL) Bits 15-0 |    | 0 |             |

| s  | B Bits 31-24 | G D    | 0 0    | SL   | 19-16 | Access Rights | Byte | SB Bits 23-      | 16 | 4 | 8<br>0<br>t |

Figure 12. 80386 Code and Data Segment Descriptor Format

Note: Bits 31 through 16 shown at offset 4 are set to 0 for all 80286 segment descriptors.

The default (D) bit of the code segment register is used to determine whether the instruction is carried out as a 16-bit or 32-bit instruction. Code segment descriptors are not used in either the real-address mode or the virtual-8086 mode. When the system microprocessor is operating in either of these modes, a D-bit value of 0 is assumed and operations default to a 16-bit length compatible with 8086 and 80286 programs.

The granularity (G) bit is used to determine the granularity of the segment length (1 = page granular, 0 = byte granular). If the value of the 20 segment-limit bits is defined as *N*, a G-bit value of 1 defines the segment size as follows:

Segment size =  $(N + 1) \times 4KB$

4KB represents the size of a page.

# Prefixes

Two prefixes have been added to the instruction set. The Operand Size prefix overrides the default selection of the operand size; the Effective Address Size prefix overrides the effective address size. The presence of either prefix toggles the default setting to its opposite condition. For example:

- If the operand size defaults to 32-bit data operations, the presence of the Operand Size prefix sets it for 16-bit data operations.

- If the effective address size is 16-bits, the presence of the Effective Address Size prefix toggles the instruction to use 32-bit effective address computations.

The prefixes are available in all 80386 modes, including the real-address mode and the virtual-8086 mode. Since the default of these modes is always 16 bits, the prefixes are used to specify 32-bit operations. If needed, either or both of the prefixes may precede any opcode bytes and affect only the instruction they precede.

# **Instruction Format**

# The instructions are presented in this format:

| Opcode             | Mode Specifier                 | Address<br>Displacement                                                                         | Immediate Data                                |

|--------------------|--------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Term               | Description                    | I                                                                                               |                                               |

| Opcode             |                                | may be one or two b<br>smaller encoding field                                                   | oytes in length. Within<br>ds may be defined. |

| Mode Specifier     |                                | the "mod r/m" byte a<br>x-base" (s-i-b) byte.                                                   | ind the                                       |

|                    |                                | m byte specifies the a<br>nat: mod T T T r/m                                                    | address mode to be                            |

|                    | 32-bit addre<br>fully specify  | byte is optional and o<br>ess modes. It follows<br>y the manner in which<br>computed. Format: s | the mod r/m byte to<br>the effective          |

| Address Displaceme | nt Follows the<br>8, 16, or 32 |                                                                                                 | s-i-b" byte. It may be                        |