### US005375084A

# United States Patent [19]

# Begun et al.

[11] Patent Number:

5,375,084

[45] Date of Patent:

Dec. 20, 1994

[54] SELECTABLE INTERFACE BETWEEN

MEMORY CONTROLLER AND MEMORY

SIMMS

No. BC9-90-044 rega:

Processing Apparatus fi

in a Dynamic Memory

[75] Inventors: Ralph M. Begun, Raleigh, N.C.; Christopher M. Herring; Mark W.

Kellogg, both of Essex Junction, Vt.

[73] Assignee: International Business Machines Corporation, Armonk, N.Y.

[21] Appl. No.: 148,955

[22] Filed: Nov. 8, 1993

[56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,797,850   | 1/1989  | Amitai             | 364/900  |

|-------------|---------|--------------------|----------|

| 5,157,384 1 | 10/1992 | Greanias et al     | 340/706  |

| 5,212,666   | 5/1993  | Takeda             | 365/63 X |

| 5,270,964 1 | 12/1993 | Bechtolsheim et al | 365/63 X |

| 5,272,664 1 | 12/1993 | Alexander et al    | 365/63 X |

#### FOREIGN PATENT DOCUMENTS

479428 4/1992 European Pat. Off. . WO9314455 7/1993 WIPO .

#### OTHER PUBLICATIONS

IBM Docket Dossier dated Jan. 10, 1990 re their ref.

No. BC9-90-044 regarding invention entitled "Data Processing Apparatus for Dynamically Setting Timing in a Dynamic Memory System".

IBM Technical Disclosure Bulletin, vol. 34, No. 10B, dated Mar., 1992 (pp. 91-94).

Primary Examiner—Do Hyun Yoo Attorney, Agent, or Firm—Calfee, Halter & Griswold

#### [57] ABSTRACT

A computer system is provided which includes a CPU having a memory controller interconnecting the CPU to a bus. The bus has card receptacles having pin receiving sockets electrically connected to the bus to receive the pins of memory cards. The memory controller is connected to logic which will identify the type of memory card which is inserted in the pin sockets. From this identification combinational logic is provided that, in response to the identification of the type of card, will direct the appropriate signals from the memory controller to the appropriate sockets depending upon which type of card is plugged into the socket. In this way, a given socket configuration can accept different types of memory cards having different pin signal configurations without physical modification of the sockets.

# 7 Claims, 2 Drawing Sheets

# SELECTABLE INTERFACE BETWEEN MEMORY CONTROLLER AND MEMORY SIMMS

# FIELD OF THE INVENTION

This invention relates generally to add-on memory systems for personal computers, and more particularly to a system and method for utilizing various types of add-on memory in a PC having a CPU which allows the CPU to utilize various types of memory cards without physically reconfiguring the CPU for each type of memory card.

# **BACKGROUND ART**

Personal computer systems are well known in the art. Personal computer systems in general, and IBM Personal Computers in particular, have attained widespread use for providing computer power to many segments of today's modern society. Personal computers can typically be defined as a desktop, floor-standing, or portable microcomputer that is comprised of a system unit having a single central processing unit (CPU) and associated volatile and non-volatile memory, including all RAM and BIOS ROE, a system monitor, a keyboard, one or more flexible diskette drives, a fixed disk storage device, and an optional printer. One of the distinguishing characteristics of these systems is the use of a motherboard or system planar to electrically connect these components together. These systems are designed  $_{30}$ primarily to give independent computing power to a single user and are inexpensively priced for purchase by individuals or small business. Examples of such personal computer systems are IBM's PERSONAL COM-PUTER AT and IBM's PERSONAL SYSTEM/2.

In computer systems, the components communicate via electrical signals. These electrical signals are typically carried by electrical connections between the system components. Typical types of electrical connections include metal traces on a printed circuit board, 40 vias, plated through holes, plugs, and individual wires wrapped from pin to pin of system components. Typically groups of electrical signals and groups of electrical connections that carry the electrical signals are referred to as a "bus." Thus, a reference to a "bus" can indicate 45 a reference to a group of electrical signals, a group of electrical connections that carry the electrical signals, or a reference to both a group of electrical signals that form a protocol and a group of electrical connections that carry the electrical signals. Systems can be said to 50 have a variety of buses. A "local bus" is a bus that is, in general, synchronous with the CPU and designed to optimize the performance of the CPU. Most systems also have a "peripheral bus," which is either synchronous or asynchronous, and may transfer data at a slower 55 frequency than the local bus. Peripheral buses typically have a number of interface slots, which are connectors that allow peripheral device cards to be pluggably connected to the peripheral bus. Typically the peripheral bus is interfaced to the system local bus with a bus 60 interface circuit (BIC). The BIC interfaces between the system local bus and the peripheral bus, handling any differences in bus bandwidths, managing control of the buses between busmasters, etc.

Personal computer systems are typically used to exe-65 cute software to perform such diverse activities as word processing, manipulation of data via spread-sheets, collection and relation of data in databases, displays of

graphics, design of electrical or mechanical systems using system design software, etc.

Most personal computer systems employ dynamic random access memory (DRAM) for main storage. DRAM memory is fabricated on silicon chips of various sizes. Most personal computers require many (e.g., 4–128 or more) of these silicon chips to provide a full main memory array of the desired size. Moreover, it is convenient to assemble multiple DRAM chips onto small card sub-assemblies and then employ these sub-assemblies in a personal computer system.

In the past, memory solutions for most low cost personal computers utilized only one of two possible mem-15 ory packaging solutions, i.e., 30-pin (1 Byte) or 72-pin (4 Byte) Single Inline Memory Modules (SIMM). While other more sophisticated solutions are in existence, they were used in a small percentage of the systems produced. The solution for memory packaging these prod-20 ucts was reasonably straightforward with the 30-pin SIMM, as the 30-pin standard was quite narrow in scope. However, this has changed with the increasing complexity of the 72-pin SIMM with various types of options on the 72-pin SIMM, as well as the proliferation of more advanced SIMMs, e.g., 88-pin SIMMs and 168-pin SIMMs. In fact, within these different size SIMMs, there has developed several different standards such as industry standard as opposed to IBM standard, and additionally some of these SIMMs were ECC SIMMs, i.e., they were error correction code (ECC) optimized; i.e., they were designed with 36 or 40 data bits and no byte write capability.

However, other problems arise, especially with respect to ECC versus parity SIMMs. For example, several particular pins are used for one particular signal on 72-pin parity SIMMs, and are used for another signal on 72-pin ECC SIMMs. Thus, the signals being delivered from the CPU by the memory controller if used for one 40 configuration will not work for the other. In the past, it was necessary to either limit the type of SIMMs that can be added on, or the planar had to be rewired for each particular type of SIMM, and thus a given system could only use a particular SIMM depending upon how it was hard wired. This presented a problem for adaptability or flexibility for a given system design to use multiple different types of SIMM memory cards.

# SUMMARY OF THE INVENTION

According to the present invention, a personal computer system is provided which includes a CPU having a memory controller interconnecting the CPU to a bus, wherein a plurality of card receptacles are provided having pin receiving sockets electrically connected to the bus to receive the pins of at least one memory card having a plurality of pins. The memory controller is connected to logic which will identify the type of memory card which is inserted in the pin sockets and from this identification provide combinational logic that, in response to the identification of the type of card, will direct the appropriate signals from the memory controller to the appropriate pins depending upon which type of card is plugged into the socket. In this way, a given socket configuration can accept different types of memory cards having different pin signal configurations without physical modification of the sockets or the memory controller, or the system.

#### **DESCRIPTION OF THE FIGURES**

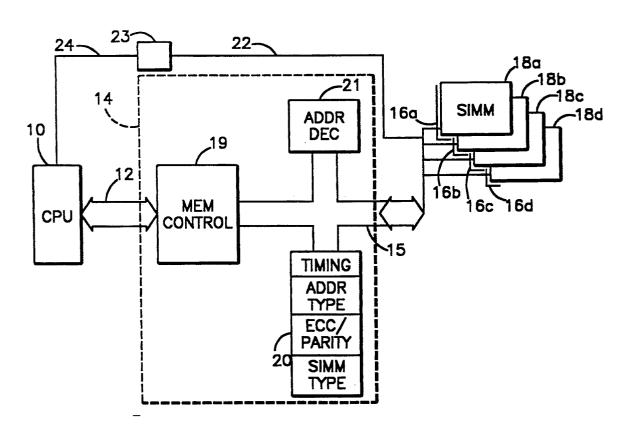

FIG. 1 is a high level block diagram of the interconnection between the CPU, the memory controller and the SIMM sockets of the present invention;

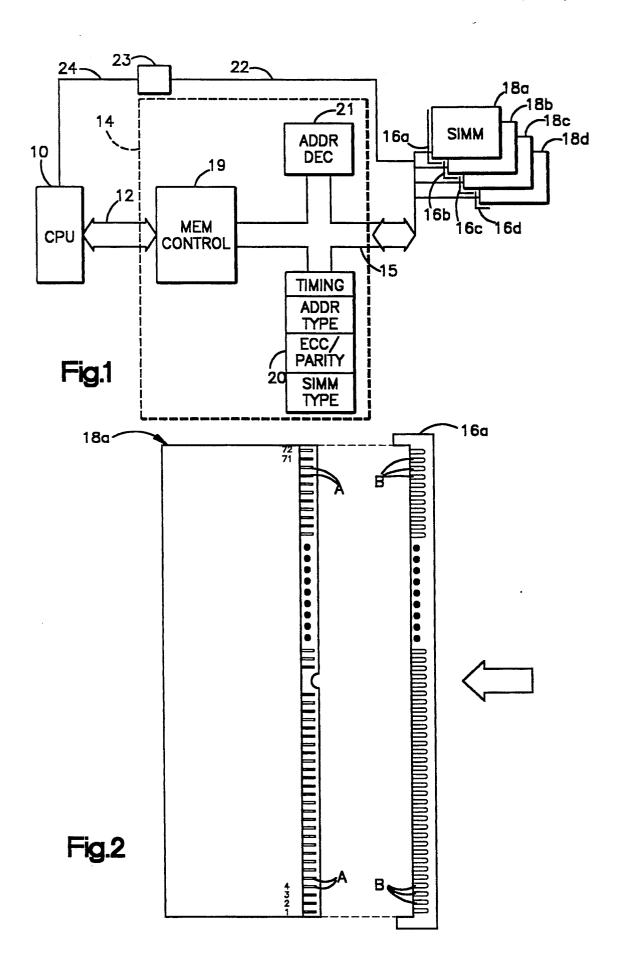

FIG. 2 is a somewhat diagrammatic view showing the pin configuration of a 72-pin SIMM and socket for receiving the SIMM; and

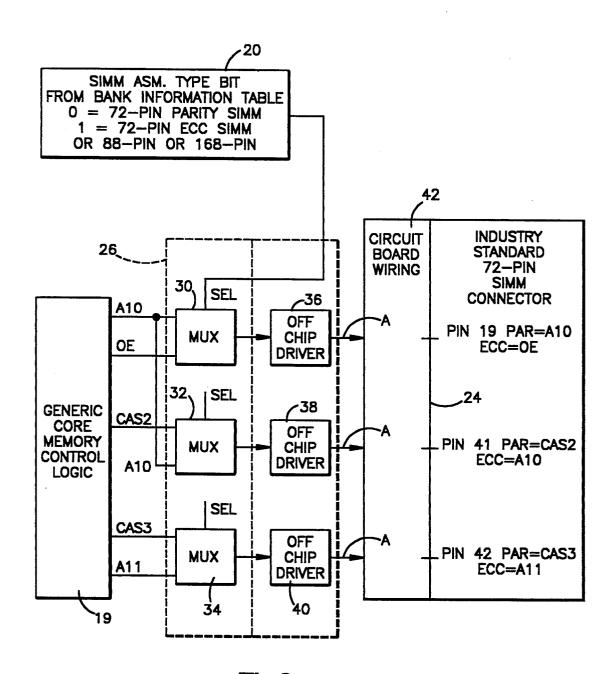

FIG. 3 is the memory select logic for 72-pin SIMMs to select the proper pin configuration between parity <sup>10</sup> and ECC SIMM for three different pins.

# DESCRIPTION OF THE PREFERRED EMBODIMENT(S)

Referring now to the drawings and for the present 15 FIG. 1, a high level diagram of the present invention as embodied in a computer system, including a CPU, is shown. As indicated above, the present invention is directed specifically to the family of personal computers which has a CPU and add-on memory cards avail- 20 able, the access to the memory cards being controlled by a memory controller and which computer has programing to allow access to add-on memory cards which have various configurations, e.g., different pin numbers and different standards which require different memory actuation signals such as ECC SIMMs, as well as standard parity SIMMs. The system will be described using 72-pin industry standard SIMMs, and showing how both parity and ECC SIMMs can be used in the same 30 socket.

As can be seen in FIG. 1, the computer system includes a CPU 10 which includes a local bus 12 connected to a memory controller 14. Memory controller 14 is connected by an expansion bus 15 to a plurality of 35 sockets 16a through 16d, each adapted to receive a memory card, the memory cards being designated 18a through 18d. In the described embodiment, the cards are 72-pin ECC or parity industry standard SIMMs. The SIMMs are shown as being arranged in a group of 40 four, although more or less cards can be accommodated to form the system memory. The memory controller 14 includes generic core memory control logic 19, a bank information table 20, and an address decoder 21. A line 22 connects the sockets 16a-16d to SIMM defining 45 logic 23 which in turn is connected by line 24 to the CPU 10. This is conventional prior art structure and allows the CPU to be programmed with information relating to the type of SIMMs selected.

FIG. 2 depicts, somewhat diagrammatically, the connection of a 72-pin SIMM 18a into a socket 16a formed on the bus 15. The various pins are shown and designated by the reference character A. The pins mate with corresponding electrical connections B in the sockets 16a. This is a conventional card and socket configuration.

In order for the CPU to operate with different types of cards, it is necessary to do two things. First, it is necessary to determine which type of cards are present, e.g., 72 pin, 68 pin, 88 pin, etc., and whether the assembly is ECC or parity. Once this determination has been made, it is necessary to provide the necessary memory actuation signals to access the memory through the pins on the card. Through the use of lines 22, 24 and logic 23, and presence detect pins (which on industry standard 65 SIMMs or pins number 67–70, the memory controller 14 is programmed with the SIMM type information which is conventional practice. The pin number is used

herein to denote the specific pin using the standard pin numbering system of industry standard SIMMs.

The address decoder 21 can function using either one of two techniques. One technique is to compare the starting and ending address regions in preprogrammed registers with the input address in question; alternatively, a preprogrammable look-up with the input address as a pointer to the table can be used. This is the input to the address decoder, with the output from the address decoder 21 to the bank information table 20.

When table 20 has been apprised of the address, and hence the type of card or cards being used, it will provide an output to the logic 19 which will provide the signal timing information to this type of SIMM. This is conventional prior art technique.

However, merely adjusting the timing and other parameters to accommodate a particular type of SIMM card will not in and of itself allow various SIMMs to be inserted in a given set of sockets. The reason for this is that with various different types of SIMMs the pins may have, and in fact do have in most cases, different "pinout" configurations; i.e. a particular I/O signal on certain pins for a 72-pin ECC SIMM will be different than the I/O signals on the same pins for a 72-pin parity SIMM. This difference is compounded when it is realized that there are many different types of cards all with different pin-out configurations. Some of these types of cards are as follows: (a) 72-pin industry standard parity SIMM; (b) 72-pin industry standard ECC SIMM; (c) 88-pin IC DRAM cards (parity with buffered inputs); (d) 88-pin IC DRAM cards (ECC with buffered inputs); (e) 168-pin 8-Byte parity SIMMs (with buffered inputs); and (f) 168-pin 8-Byte ECC SIMMs (with buffered inputs). Each of these cards will have a different I/O configuration on certain of its pins. Therefore, the memory controller 14 needs to not only have the proper signal timing, but arrangements must be made so that, depending upon which type of memory card is inserted, the proper signals with the proper actuation control sequence will be supplied to the appropriate pins.

This is accomplished by a logic circuit contained within the memory controller 14. Used as an example here is the pin-out or I/O signal configuration of the 72-pin industry standard ECC SIMM as compared with the 72-pin industry standard parity SIMM, each of which SIMMS have the same pin geometry, but different signal configuration for some of the pins. The signal configurations for the 72-pins are shown for the parity SIMMs in Table I, and for the ECC SIMMs in Table II.

TABLE I

| PIN | SYMBOL                                                                                 |

|-----|----------------------------------------------------------------------------------------|

| 1   | GND                                                                                    |

| 2   | $DQ_0$                                                                                 |

| 3   | DQ <sub>18</sub>                                                                       |

| 4   | DO <sub>1</sub>                                                                        |

| 5   | DQ19<br>DQ2<br>DQ20<br>DQ3<br>DQ21<br>V cc                                             |

| 6   | $DQ_2$                                                                                 |

| 7   | $DQ_{20}$                                                                              |

| 8   | DQ <sub>3</sub>                                                                        |

| 9   | $DQ_{21}$                                                                              |

| 10  | $V_{cc}$                                                                               |

| 11  | NC                                                                                     |

| 12  | $A_0$                                                                                  |

| 13  | $A_1$                                                                                  |

| 14  | A <sub>2</sub>                                                                         |

| 15  | A <sub>3</sub>                                                                         |

| 16  | A4                                                                                     |

| 17  | A <sub>2</sub><br>A <sub>3</sub><br>A <sub>4</sub><br>A <sub>5</sub><br>A <sub>6</sub> |

| 18  | A <sub>6</sub>                                                                         |

|     |                                                                                        |

| TABLE I-continued                      |                                         |              |                  |                                    |                                                      | _                                                     |                     | TABLE II-continued |                     |                 |                                        |                        |       |       |

|----------------------------------------|-----------------------------------------|--------------|------------------|------------------------------------|------------------------------------------------------|-------------------------------------------------------|---------------------|--------------------|---------------------|-----------------|----------------------------------------|------------------------|-------|-------|

|                                        |                                         | 19           |                  | A <sub>10</sub>                    |                                                      |                                                       |                     |                    |                     | 13              |                                        | Aı                     |       |       |

|                                        |                                         | 20<br>21     |                  | DQ <sub>4</sub>                    |                                                      |                                                       |                     |                    |                     | 14              |                                        | $A_2$                  |       |       |

|                                        |                                         | 22           |                  | DQ <sub>2</sub><br>DQ <sub>5</sub> |                                                      |                                                       | 5                   |                    |                     | 15<br>16        |                                        | A3                     |       |       |

|                                        | 22 DQ5<br>23 DQ <sub>23</sub>           |              |                  |                                    | ,                                                    |                                                       |                     | 17                 |                     | $A_4$ $A_5$     |                                        |                        |       |       |

|                                        |                                         | 24           |                  | DQ <sub>6</sub>                    |                                                      |                                                       |                     |                    |                     | 18              |                                        | A <sub>6</sub>         |       |       |

|                                        |                                         | 25           |                  | $DQ_2$                             |                                                      |                                                       |                     |                    |                     | 19              |                                        | OË                     |       |       |

|                                        | 26 DQ <sub>7</sub>                      |              |                  |                                    |                                                      |                                                       | 20 DQ8              |                    |                     |                 |                                        |                        |       |       |

|                                        | 27 DQ <sub>25</sub>                     |              |                  |                                    |                                                      |                                                       | 21 DQ9              |                    |                     |                 |                                        |                        |       |       |

|                                        |                                         | 28<br>29     |                  | A <sub>7</sub>                     |                                                      |                                                       | 10                  |                    |                     | 22              |                                        | $DQ_1$                 |       |       |

|                                        |                                         | 30           |                  | NC<br>V                            |                                                      |                                                       |                     |                    |                     | 23<br>24        |                                        | DQ <sub>1</sub>        |       |       |

|                                        | 30 V <sub>cc</sub><br>31 A <sub>8</sub> |              |                  |                                    |                                                      |                                                       |                     |                    | 25                  |                 | $rac{	extbf{DQ}_{1}}{	extbf{DQ}_{1}}$ |                        |       |       |

|                                        | 32 A <sub>9</sub>                       |              |                  |                                    |                                                      |                                                       |                     |                    | 26                  |                 | $\overline{DQ_1}$                      |                        |       |       |

|                                        | 33 RAS <sub>3</sub>                     |              |                  |                                    |                                                      |                                                       |                     |                    |                     | 27              |                                        | DQ <sub>1</sub>        |       |       |

|                                        | $RAS_2$                                 |              |                  |                                    |                                                      |                                                       | 15                  |                    |                     | 28              |                                        | $A_7$                  |       |       |

|                                        |                                         | 35<br>26     |                  | DQ <sub>2</sub>                    |                                                      |                                                       |                     |                    | 29 DQ <sub>16</sub> |                 |                                        |                        |       |       |

|                                        |                                         | 36<br>37     |                  | DQ <sub>8</sub><br>DQ <sub>1</sub> |                                                      |                                                       |                     |                    |                     | 30<br>31        |                                        | $\mathbf{V}_{cc}$      |       |       |

|                                        |                                         | 38           | ,                | DQ <sub>1</sub><br>DQ <sub>3</sub> | /<br>c                                               |                                                       |                     |                    |                     | 32              |                                        | A8<br>A9               |       |       |

|                                        |                                         | 39           |                  | GNI                                |                                                      |                                                       |                     |                    |                     | 33              |                                        | NC                     |       |       |

|                                        |                                         | 40           |                  | CAS                                |                                                      |                                                       | 20                  |                    | 34 NC               |                 |                                        |                        |       |       |

|                                        |                                         | 41           |                  | CAS                                | 2                                                    |                                                       | 20                  |                    |                     | 35              |                                        | $DQ_1$                 | 7     |       |

|                                        |                                         | 42           |                  | CAS                                |                                                      |                                                       |                     |                    |                     | 36              |                                        | DQ                     |       |       |

|                                        |                                         | 43<br>44     |                  | CAS                                |                                                      |                                                       |                     |                    |                     | 37<br>38        |                                        | DQ <sub>1</sub>        |       |       |

|                                        |                                         | 45           |                  | RAS<br>RAS                         |                                                      |                                                       |                     |                    |                     | 39              |                                        | DQ <sub>2</sub><br>GNI |       |       |

|                                        |                                         | 46           |                  | NC.                                | 1                                                    |                                                       |                     |                    |                     | 40              |                                        | CAS                    |       |       |

|                                        |                                         | 47           |                  | WE                                 |                                                      |                                                       | 25                  |                    |                     | 41              |                                        | A <sub>10</sub>        | U     |       |

|                                        |                                         | 48           |                  | NC                                 |                                                      |                                                       |                     |                    |                     | 42              |                                        | $A_{11}$               |       |       |

|                                        |                                         | 49           |                  | DQ <sub>9</sub>                    |                                                      |                                                       |                     |                    |                     | 43              |                                        | CAS                    |       |       |

|                                        |                                         | 50           |                  | DQ <sub>2</sub>                    |                                                      |                                                       |                     |                    |                     | 44              |                                        | RAS                    | -     |       |

|                                        |                                         | 51<br>52     |                  | DQ <sub>10</sub>                   |                                                      |                                                       |                     |                    |                     | 45<br>46        |                                        | RAS<br>DQ <sub>2</sub> |       |       |

|                                        |                                         | 53           |                  | $DQ_2$<br>$DQ_1$                   |                                                      |                                                       | 30                  |                    |                     | 47              |                                        | WE                     | l     |       |

|                                        |                                         | 54           |                  | $\widetilde{DQ}_{29}$              | 1<br>2                                               |                                                       | •                   |                    |                     | 48              |                                        | GNI                    | )     |       |

|                                        | 55 DQ <sub>12</sub>                     |              |                  |                                    |                                                      | 49 DQ <sub>22</sub>                                   |                     |                    |                     |                 |                                        |                        |       |       |

|                                        |                                         | 56           |                  | $DQ_{30}$                          |                                                      |                                                       |                     |                    | 50 DQ               |                 |                                        |                        |       |       |

|                                        | $DQ_{13}$                               |              |                  |                                    |                                                      |                                                       |                     | 51<br>52           |                     | DQ <sub>2</sub> | 1                                      |                        |       |       |

|                                        |                                         | 58<br>59     |                  | DQ <sub>3</sub>                    | i                                                    |                                                       | 25                  |                    |                     | 52<br>53        |                                        | DQ <sub>2</sub>        |       |       |

|                                        | 59 V <sub>cc</sub> 60 DQ <sub>32</sub>  |              |                  |                                    | 35                                                   | 53 DQ <sub>26</sub><br>54 DQ <sub>27</sub>            |                     |                    |                     |                 |                                        |                        |       |       |

|                                        | 61 DQ <sub>14</sub>                     |              |                  |                                    |                                                      | $DQ_{28}$                                             |                     |                    |                     |                 |                                        |                        |       |       |

|                                        | 62 DQ <sub>33</sub>                     |              |                  |                                    |                                                      |                                                       | 56 DQ <sub>29</sub> |                    |                     |                 |                                        |                        |       |       |

|                                        | $\mathbf{DQ}_{15}$                      |              |                  |                                    |                                                      |                                                       |                     | 57                 |                     | $DQ_3$          | 3                                      |                        |       |       |

|                                        | 64 DQ <sub>34</sub>                     |              |                  |                                    |                                                      |                                                       |                     | 58                 |                     | DQ <sub>3</sub> | 1                                      |                        |       |       |

|                                        | 65 DQ <sub>16</sub>                     |              |                  |                                    | 40                                                   | 59 V <sub>cc</sub><br>60 DQ <sub>32</sub>             |                     |                    |                     |                 |                                        |                        |       |       |

|                                        | 66 NC<br>67 Note 1                      |              |                  |                                    |                                                      | 61 DQ32                                               |                     |                    |                     |                 |                                        |                        |       |       |

|                                        | 68 Note 1                               |              |                  |                                    |                                                      | 62 DQ <sub>34</sub>                                   |                     |                    |                     |                 |                                        |                        |       |       |

|                                        | 69 Note 1                               |              |                  |                                    |                                                      | 63 DQ <sub>35</sub>                                   |                     |                    |                     |                 |                                        |                        |       |       |

|                                        | 70 Note 1                               |              |                  |                                    |                                                      | 64 DQ36                                               |                     |                    |                     |                 |                                        |                        |       |       |

| 71 NC                                  |                                         |              |                  | 45                                 | 65 DQ <sub>37</sub><br>66 DQ <sub>38</sub>           |                                                       |                     |                    |                     |                 |                                        |                        |       |       |

| 72 GND                                 |                                         |              |                  | _ ~                                |                                                      | 66 DQ <sub>38</sub><br>67 Note 1                      |                     |                    |                     |                 |                                        |                        |       |       |

| DENSITY                                |                                         |              |                  |                                    |                                                      | 68 Note 1                                             |                     |                    |                     |                 |                                        |                        |       |       |

|                                        | 1 MB                                    | 2 MB         | 4 MB             | 8 MB                               | 16 MB                                                | 32 MB                                                 |                     |                    |                     | 69              |                                        | Note                   |       |       |

| 67                                     | GND                                     | NC           | GND              | NC                                 | GND                                                  | NC                                                    | _                   |                    |                     | 70              |                                        | Note                   |       |       |

| 68                                     | NC                                      | GND          | GND              | NC                                 | NC                                                   | GND                                                   |                     |                    |                     | 71<br>72        |                                        | DQ <sub>3</sub>        |       |       |

|                                        |                                         |              | SPEE             | <u>D</u>                           |                                                      |                                                       | 50                  |                    |                     | 72              |                                        | GNI                    | )     |       |

|                                        | PINS                                    | 60 ns        | 70 ns            | 80                                 | ns                                                   | 100 ns                                                | _                   |                    |                     |                 | _ DENS                                 |                        |       |       |

|                                        | 69                                      | NC           | GND              | NO                                 |                                                      | GND                                                   |                     |                    | 1 MB                | 2 MB            | 4 MB                                   | 8 MB                   | 16 MB | 32 MB |

|                                        | 70                                      | NC           | NC               |                                    | ND O                                                 | GND                                                   | _                   | 67                 | GND                 | NC              | GND                                    | NC                     | GND   | NC    |

| Note                                   | 1: Pins 67-7                            | 0 define SIM | M density ar     | d speed.                           |                                                      |                                                       |                     | <b>6</b> 8         | NC                  | GND             | GND                                    | NC                     | NC    | GND   |

|                                        |                                         |              |                  | 55                                 |                                                      | DDIO                                                  | <b>(0</b>           | SPEE               |                     |                 |                                        |                        |       |       |

| TABLE II                               |                                         |              |                  |                                    |                                                      | PINS                                                  | 60 ns               | 70 ns              | 80                  |                 | 100 ns                                 |                        |       |       |

|                                        |                                         | DDZ          | 171010           |                                    |                                                      |                                                       | _                   |                    | 69                  | NC              | GND                                    | NO                     |       | GND   |

| PIN SYMBOL                             |                                         | _            | 70 NC NC GND GND |                                    |                                                      |                                                       |                     |                    |                     |                 |                                        |                        |       |       |

| 1 GND<br>2 DQ <sub>0</sub>             |                                         |              |                  | 4٥                                 | Note 1: Pins 67-70 define SIMM density and speed.    |                                                       |                     |                    |                     |                 |                                        |                        |       |       |

| 3 DQ <sub>1</sub>                      |                                         |              |                  |                                    | 60                                                   |                                                       |                     |                    |                     | C               |                                        |                        |       |       |

| 4 $\overrightarrow{DQ_2}$              |                                         |              |                  |                                    | A<br>T/C                                             | s can be                                              | e seen, a m         | najority           | of the p            | ıns utıli       | ze the same                            |                        |       |       |

| 5 $DQ_3$                               |                                         |              |                  |                                    |                                                      | I/O                                                   | signal              | on the same        | me pın.             | Howev           | er, in a                               | significant            |       |       |

| 6 $\overline{DQ_4}$                    |                                         |              |                  |                                    |                                                      | nun                                                   | nber of             | cases, diff        | erent sig           | gnals ar        | e used                                 | on different           |       |       |

| 7 DQ <sub>5</sub><br>8 DO <sub>6</sub> |                                         |              |                  |                                    | pins. For example, pin 19 on the parity SIMM has the |                                                       |                     |                    |                     |                 |                                        |                        |       |       |

| 8 DQ <sub>6</sub><br>9 DQ <sub>7</sub> |                                         |              |                  |                                    | 65                                                   | A10 signal and on the ECC SIMM has the output en-     |                     |                    |                     |                 |                                        |                        |       |       |

| $V_{cc}$                               |                                         |              |                  |                                    |                                                      | able signal; pin 41 on the parity SIMM has the CAS2   |                     |                    |                     |                 |                                        |                        |       |       |

|                                        | 11 PO <sub>5</sub>                      |              |                  |                                    |                                                      | signal, whereas on the ECC SIMM it is the A10 signal; |                     |                    |                     |                 |                                        |                        |       |       |

| 12 A <sub>0</sub>                      |                                         |              |                  |                                    |                                                      |                                                       |                     |                    |                     |                 | AS3 signal.                            |                        |       |       |

whereas on the ECC SIPS4 it is the All signal. Thus, it is necessary to properly provide for these different configurations depending upon which SIMM is inserted. To this end, the memory control logic includes logic to select the necessary pin configuration depending upon 5 the SIMM inserted.

This logic selection is shown in FIG. 3, it being understood that similar logic can be used for the other pins where different I/O signals are to be used. The logic includes three multiplexors 30, 32 and 34, connected 10 respectively to off-chip drivers 36, 38 and 40. As input to the multiplexor 30 are the A10 and the output enable (OE) signals as input to the multiplexor 32 are the CAS2 and A10 signals, and as input to the multiplexor 34 are CAS3 and A11 signals. These signals are all supplied by 15 the memory controller 14 to generate the various signals to the respective pins. A signal which defines the type of SIMM is received from the bank information table 20, which in turn has received a signal from the address decoder 21 as to the type of SIMM, i.e., ECC or 20

The multiplexors 30, 32 and 34 each have a select line which determines the type of pin. For example, in the present embodiment, a "0" indicates a 72-pin parity SIMM, while a "1" indicates a 72-pin ECC SIMM. The 25 various signals inputted to the multiplexors 30, 32 and 34, together with the chip select also inputted to the multiplexor 34, provides an output signal to the off-chip drivers 36, 38 and 40 which, depending upon the chip select, the chip driver 36 will at pin 19 provide either an 30 A10 or an output enable signal, at pin 41 provide either a CAS2 or an A10 signal, and at pin 42 provide either a CAS3 or an A11 signal. Other pins having different functions can be similarly driven.

Thus, it can be seen that with any given socket-pin 35 configuration wherein the pins may have different I/O signals depending upon the type of card, e.g., parity SIMMs and ECC SIMMs, the logic on the memory controller chip will provide the necessary I/O signals to the required pins once the SIMM type has been deter- 40 mined by the logic contained within the CPU, and the internal logic within the memory controller and CPU will be modified to perform the various I/O signal functions required. This allows a single CPU and memory controller system to be utilized with different SIMM 45 socket configurations, and even within the same socket configuration with different pin I/O configurations without the necessity of any external glue logic or any logic external to the controller and CPU.

shown and described, various adaptations and modifications can be made without departing from the scope of the invention as defined in the appended claims.

What is claimed:

device to generate electrical signal, a bus, a memory controller connected to said bus and said CPU, a plurality of pin accessing sockets electrically connected to said bus to receive at least one memory card having a plurality of pins with a given pin geometry, and 60 wherein said at least one memory card is selected from at least two different types of cards having the same pin geometry and wherein a plurality of pins at a given

location of each of said two different cards are configured to receive different memory actuation signals from said memory controller, said memory controller including a logic circuit having identification logic responsive to a signal from said at least one card to identify which of said at least two different types of cards is inserted in said pin accessing sockets; and system combinational logic responsive to said identification logic and said memory controller to direct a plurality of appropriate signals from the memory controller to a plurality of appropriate pin accessing sockets depending on which of said at least two different cards is plugged into the pin accessing sockets; whereby a given pin accessing socket can use different types of memory cards having different pin signal configurations without physical modification of the pin accessing socket or memory controller, or the system.

- 2. The computer system as defined in claim 1 wherein said at least one memory card of said two different cards is a parity SIMM and the other is an ECC SIMM.

- 3. The computer system as defined in claim 2 wherein a plurality of pins on the ECC SIMM have a different signal configuration than corresponding pins of said plurality of pins on the parity SIMM.

- 4. The computer system as defined in claim 1 wherein said combinational logic is included at least in part in said memory controller.

- 5. A method of utilizing first and second types of memory SIMMs having a plurality of pins with a same pin geometry but different operating signals on at least one of said plurality of pins, and which SIMMs are connected to a computer system having a CPU, including a device to generate electrical signals, a bus, a memory controller connecting said bus and said CPU, a plurality of pin accessing sockets electrically connected to said bus to receive said plurality of pins of each of said first and second memory SIMMs and said plurality of pins corresponding to the pin access sockets, said method comprising the steps of: providing an identification signal from a SIMM inserted in at least one of said plurality of pin access sockets to identify which of said first and second types of memory SIMMs is inserted in said at least one of said plurality of pin access sockets; directing appropriate signals from the memory controller to at least one of a plurality of appropriate pin accessing sockets responsive to the first and second types of memory SIMMS which is connected to the at least one of said plurality of pin access sockets; whereby a While one embodiment of this invention has been 50 given pin accessing socket can use different types of memory cards having different pin signal configurations without physical modification of the pin accessing socket or memory controller, or the system.

- 6. The method as defined in claim 5 wherein there are 1. A computer system comprising a CPU, including a 55 a plurality of pins having different operating signals between said first and second types of memory SIMMs.

- 7. The method as defined in claim 6, wherein said first type of memory SIMM is one selected from a group consisting of a parity SIMM and an ECC SIMM and said second type of memory SIMM is one selected from a group consisting of a parity SIMM and an ECC SIMM.