TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC.

# CMOS GATE ARRAY TC110G SERIES GATE ARRAY

Toshiba introduces the new generation gate arrays

— The TC110G series—capable of integrating

5X more than the TC17G series.

Uses Toshiba's proprietary HC2MOS/VLSI technologies. State of the art processing with high packing densities which produced a 4Mbit Dynamic RAM

## TC110G Series — 50K gates/0.6ns. Compact and powerful!

### General

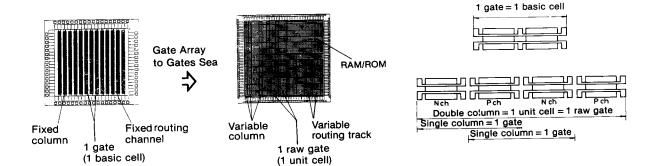

Toshiba CMOS Gate Array family, TC110G Series, with interconnect routing which is not confined to "routing channels". This technique increases silicon efficiency (functions/mm²).

Higher density and Toshiba HC<sup>2</sup>MOS process provide subnanosecond speeds of 0.6ns typical gate delays (2-input NAND gate, fanout = 2, tpd.). TC110G Series is introduced as 14 base arrays with 1.4K to 50K estimated usable gates.

Gate Array design using TC110G Series is supported by the TOSHIBA MAINFRAME CAD SYSTEM. Hierarchical designs with large macro capabilities.

## **Product Specifications**

|                               | TC110G series                                  |

|-------------------------------|------------------------------------------------|

| Process technology            | HC <sup>2</sup> MOS Si-gate double layer metal |

|                               | 1.5μm                                          |

| Gate speed (inner gate, typ.) | 0.6ns                                          |

| Maximum toggle frequency      | 150MHz                                         |

| Supply voltage                | 5V                                             |

| Application                   | ASTTL/ECL                                      |

#### **Product Lines**

| Part Number | Gate <sup>(1)</sup><br>Complexity | Estimated <sup>(2)</sup><br>Usable Gates | Maximum Pads <sup>(3)</sup> | Maximum I/C<br>Pads <sup>(3)(4)</sup> |

|-------------|-----------------------------------|------------------------------------------|-----------------------------|---------------------------------------|

| TC110G C9   | 129,042                           | 50,000                                   | 368                         | 256                                   |

| TC110G A0   | 100,182                           | 40,000                                   | 326                         | 256                                   |

| TC110G 75   | 74,970                            | 30,000                                   | 282                         | 256                                   |

| TC110G 51   | 50,904                            | 20,000                                   | 234                         | 226                                   |

| TC110G 38   | 37,932                            | 15,000                                   | 204                         | 196                                   |

| TC110G 32   | 32,000                            | 13,000                                   | 188                         | 180                                   |

| TC110G 26   | 25,740                            | 10,000                                   | 168                         | 160                                   |

| TC110G 21   | 21,060                            | 8,400                                    | 154                         | 146                                   |

| TC110G 17   | 17,082                            | 6,800                                    | 140                         | 132                                   |

| TC110G 14   | 14,204                            | 5,600                                    | 128                         | 120                                   |

| TC110G 11   | 11,092                            | 4,400                                    | 114                         | 106                                   |

| TC110G 08   | 8,000                             | 3,200                                    | 100                         | 92                                    |

| TC110G 05   | 5,120                             | 2,000                                    | 80                          | 72                                    |

| TC110G 03   | 3,498                             | 1,400                                    | 68                          | 60                                    |

Notes: 1. Raw-gates

2. Based on 40% array utilization. Actual utilization varies, depending on cell types used.

3. Additional I/O pads may be configured as V<sub>DD</sub>/V<sub>SS</sub>, subject to number and drive of output buffers.

4. I/O signals presently limited to 256 by tester capability.

**TAEC**

This technical data may be controlled under U.S. Export Administration Regulations and may be subject to the approval of the U.S. Department of Commerce prior to export. Any export or re-export directly or indirectly, in contravention of the U.S. Export Administration Regulations is strictly prohibited.

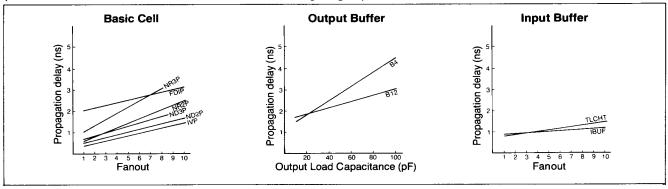

## **Basic Cell Delay vs Fanout**

(TC110G38,  $V_{DD} = 5V$ , Ta = 25°C with estimated wiring lengths)

## Absolute Maximum Ratings (Vss = 0V)

| Symbol          | Parameter           | Rating                   | Unit |

|-----------------|---------------------|--------------------------|------|

| V <sub>DD</sub> | DC supply voltage   | -0.3  to  +7.0           | V    |

| VIN             | DC input voltage    | $-0.3$ to $V_{DD} + 0.3$ | \ V  |

| I <sub>IN</sub> | DC input current    | ±10                      | mA   |

| Tstg            | Storage temperature | -40 to +125              | °C   |

## Recommended Commercial Operating Conditions (Vss = 0V)

| Symbol          | Parameter           | Rating       | Unit |

|-----------------|---------------------|--------------|------|

| V <sub>DD</sub> | DC supply voltage   | 4.75 to 5.25 | V    |

| Ta              | Ambient temperature | 0 to +70     | °C   |

## **DC Electrical Characteristics**

Specified at  $VDD = 5V \pm 5\%$  ambient temperature

| Comple of       | Poromotor                      | Parameter Condition                                  |             | Series      | Unit  |

|-----------------|--------------------------------|------------------------------------------------------|-------------|-------------|-------|

| Symbol          | Parameter                      | Condition                                            | Min.        | Max.        | UIIII |

|                 | Low Level Input Voltage        |                                                      |             |             |       |

| VIH             | TTL Level                      |                                                      | 2.0         |             | _ v   |

| • 111           | CMOS Level                     |                                                      | 3.5         |             |       |

|                 | SCHMITT Trigger                |                                                      | 4.0         |             |       |

|                 | High Level Input Voltage       |                                                      |             |             |       |

| VIL             | TTL Level                      |                                                      |             | 0.8         | _ v   |

| • 12            | CMOS Level                     |                                                      |             | 1.5         |       |

|                 | SCHMITT Trigger                |                                                      |             | 1.0         |       |

|                 | High Level Input Current       | V <sub>IN</sub> = V <sub>DD</sub>                    | <b>– 10</b> | 10          | μΑ    |

| Ін              | With Pull-down Resistors       | VIN = VDD                                            | 10          | 200         | μΛ    |

|                 | Low Level Input Current        | V <sub>IN</sub> = V <sub>SS</sub>                    | <b>- 10</b> | 10          | μΑ    |

| l <sub>IL</sub> | With Pull-up Resistors         | VIN = VSS                                            | - 200       | <b>– 10</b> | μ^    |

| 31.             | High Level Output Voltage      |                                                      |             |             |       |

|                 | Type B1                        | $I_{OH} = -1mA$                                      |             |             |       |

|                 | Type B2                        | $I_{OH} = -2mA$                                      |             |             |       |

| Vон             | Type B4                        | $I_{OH} = -4mA$                                      | 2.4         |             | V     |

|                 | Type B6                        | I <sub>OH</sub> = -6mA                               |             |             |       |

|                 | Type B8                        | $I_{OH} = -8mA$                                      |             |             |       |

|                 | Type B12 <sup>(1)</sup>        | I <sub>OH</sub> = - 12mA                             |             |             |       |

|                 | Low Level Output Voltage       |                                                      |             |             |       |

|                 | Type B1                        | I <sub>OL</sub> = 1mA                                |             |             |       |

|                 | Type B2                        | $I_{OL} = 2mA$                                       |             |             |       |

| Vol             | Type B4                        | I <sub>OL</sub> = 4mA                                |             | 0.4         | V     |

|                 | Type B6                        | I <sub>OL</sub> = 6mA                                |             |             |       |

|                 | Type B8                        | I <sub>OL</sub> = 8mA                                |             |             |       |

|                 | Type B12 <sup>(1)</sup>        | I <sub>OL</sub> = 12mA                               |             |             |       |

| _               | High Impedance Leakage Current |                                                      | <b>– 10</b> | 10          | ╛.    |

| loz             | With Pull-up Resistors         | V <sub>OU</sub> T=V <sub>DD</sub> or V <sub>SS</sub> | - 200       | - 10        | μΑ    |

|                 | With Pull-down Resistors       |                                                      | 10          | 200         |       |

| IDD             | Quiescent Supply Current       | V <sub>IN</sub> = V <sub>DD</sub> or V <sub>SS</sub> |             | 100(2)      | μΑ    |

Notes: (1) Requires two output pads. (2) Customer-Design Dependent

## **Development Flow & Customer Interface**

|           |         | Functional<br>& logic<br>design | Network<br>entry | Verify<br>design | Functional<br>& timing<br>simulation | Verify<br>node<br>coverage | Auto place<br>& route | Re-<br>simulate | PG & MASK<br>tooling |

|-----------|---------|---------------------------------|------------------|------------------|--------------------------------------|----------------------------|-----------------------|-----------------|----------------------|

|           | Level 1 | $\qquad \Rightarrow \qquad$     |                  |                  |                                      |                            |                       |                 |                      |

| Interface | Level 2 |                                 |                  |                  |                                      | <b></b>                    |                       |                 |                      |

| ievel     | Level 3 |                                 |                  |                  |                                      |                            |                       |                 |                      |

|           | Level 4 |                                 |                  |                  |                                      |                            |                       | $\rightarrow$   |                      |

<sup>(1)</sup> At level-2, design procedure takes place by customer at Toshiba LSI Design Center and at customer site for level-3.

## CAS System Features TOSHIBA MAINFRAME CAD SYSTEM

Integrated Hierarchical Design System using Macrocell and Macrofunctions library for:

Functional design ● Logic design ● Auto place

& route • Test pattern generation

High-speed logic simulation and Flexible auto place and route

Maximum circuit size:

●50K gates

Compatible interface language (TDL, TSTL)

Remote-access in man-machine environment

### **Package Adaptability List**

As of June 1989

| ackage | Par         | t Number           | 03 | 05 | 08       | 11 | 14  | 17 | 21       | 26  | 32  | 38 | 51 | 75 | AO | C9 |

|--------|-------------|--------------------|----|----|----------|----|-----|----|----------|-----|-----|----|----|----|----|----|

|        |             | 24                 | Α  | A  | Α        | Α  |     |    |          |     |     |    |    |    |    |    |

| 28     |             | A                  | Α  | A  | Α        | Α  |     | ,  |          |     |     |    |    |    |    |    |

|        |             | 40                 | A  | Α  | Α        | Α  | A   | Α  |          |     |     |    |    |    |    |    |

| DIP    |             | 42                 | Α  | Α  | Α        | Α  | Α   | A  |          |     |     |    |    |    |    |    |

|        |             | 48                 | A  | A  | Α        | Α  | Α   | Α  |          |     | - " |    |    |    |    |    |

|        |             | S42                | Α  | Α  | Α        | Α  | Α   | Α  |          |     |     |    |    |    |    |    |

|        |             | S64                |    | Α  | А        | Α  | Α   | Α  | D        | D   |     |    |    |    |    |    |

|        |             | 64                 | Α  | Α  | Α        | Α  | Α   | Α  | Α        | Α   | Α   | Α  | Α  |    |    |    |

|        |             | 68                 | Α  | Α  | Α        | Α  | Α   | Α  | Α        | Α   | Α   | Α  | Α  |    |    |    |

|        |             | 84                 |    | Α  | Α        | Α  | Α   | Α  | Α        | Α   | A   | Α  | Α  |    |    |    |

|        |             | 100                |    |    | Α        | Α  | Α   | Α  | Α        | Α   | Α   | Α  | Α  |    |    |    |

| PGA    |             | 120                |    |    |          | Α  | Α   | Ā  | Α        | Α   | Α   | Α  | Α  |    |    |    |

|        |             | 135                |    |    |          |    |     | Α  | Α        | Α   | Α   | Α  | Α  |    |    |    |

|        |             | 144                |    |    |          |    | T   | Α  | Α        | Α   | Α   | Α  | Α  |    |    |    |

|        |             | 180                |    |    |          |    |     |    |          | Α   | Α   | Α  | Α  |    |    |    |

|        |             | 224                |    |    | _        |    |     |    |          |     |     |    | Α  |    |    |    |

|        |             | 120                |    |    |          | Α  | Α   | Α  | Α        | Α   | Α   | Α  | Α  |    |    |    |

| Metal  | PGA         | 144                |    |    |          |    |     | Α  | Α        | Α   | Α   | Α  | Α  | _  |    |    |

|        |             | 95                 |    |    |          | -  |     |    |          |     |     | Р  | Р  | Р  |    |    |

|        |             | 155                |    |    |          |    |     |    | <u> </u> |     |     | D  | D  | D  | D  | D  |

| Cavity | Down PGA    | 223                |    | _  | _        |    |     |    |          |     | -   | Α  | Α  | Α  | Α  | Α  |

|        |             | 299                |    |    | <u> </u> |    | i   |    |          |     |     |    |    | Α  | Α  | Α  |

|        |             | 44                 | A  | Α  | Α        | Α  | Α   | Α  | Р        |     |     |    |    |    |    |    |

| PLCC   | ;           | 68                 | Α  | Α  | Α        | Α  | Α   | Α  | Α        | Α   | Α   | Α  | D  |    |    |    |

|        |             | 84                 |    | -  | Α        | Α  | Α.  | Α  | Α        | А   | Α   | Α  | D  |    |    |    |

|        |             | μ 44               | A  | A  | Α        | D  | D   | _  |          |     |     |    |    |    |    |    |

|        |             | 44                 | Α  | Α  | Α        | Α  | Α   | Α  |          |     |     |    |    |    |    |    |

|        |             | 60                 | Α  | Α  | Α        | Α  | Α   | Α  | D        | D   |     |    |    |    |    |    |

|        |             | 100A <sup>1)</sup> |    | Α  | ļ        |    |     |    |          |     |     |    |    |    |    |    |

|        | Square      | 100 <sup>1)</sup>  |    |    | Α        | Α  | Α   | Α  | Α        | Α   | Α   | Α  | Α  |    |    |    |

|        |             | 120                |    |    |          |    | D   | D  | D        | D   | D   | D  | D  |    |    |    |

| PFP    |             | 144                |    |    | Α        | Α  | Α   | Α  | Α        | Α   | Α   | Α  | Α  | D  | Р  | P  |

|        |             | 160                |    |    |          |    |     |    |          | Α   | Α   | Α  | Α  | Α  | P  | F  |

| Rectar |             | 184                |    |    |          |    |     |    | Α        | _ A | Α   | Α  | Α  | D  | Р  | F  |

|        |             | 64                 |    | Α  | Α        | Α  | Α   | Α  | Р        | Р   |     |    |    |    |    |    |

|        | Rectangular | 80                 | T  | Α  | Α        | Α  | Α   | Α  | Α        | Р   |     |    |    |    |    |    |

|        |             | 100                |    |    | Α        | Α  | Α   | Α  | Р        | Р   |     |    |    |    |    |    |

|        | -           | 100 <sup>1)</sup>  |    | 1  |          |    |     |    | Α        | Α   | Α   | Α  | Α  |    |    |    |

|        |             | 144                |    |    |          |    |     |    |          |     | Α   | Α  | Α  | D  | D  | D  |

| CFP    |             | 160                |    |    |          |    |     | 1  |          |     | D   | D  | D  | D  | D  | D  |

|        |             | 184                |    |    | + -      | 1  | + - |    |          |     |     | 1  | D  | D  | D  | D  |

A: Adaptable

Please refer to "Package Selector Guide" (Document I.D. SEMI-E-S 1001) for further information in detail.

<sup>(2)</sup> As for the EWS support, please refer to "EWS INTERFACE" (Document ID: SEMI-E-S1011)

D: Check with Toshiba for availability

<sup>(</sup>Under development)

P: Check with Toshiba for availability (Under planning)

Notes: 1) Flat Package 100 pin is classified into 2 types determined by number of inner leads available: 100A—84 inner leads. 100—100 inner leads.

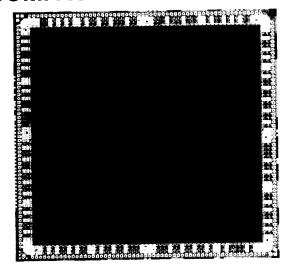

## **COMPACT AND POWERFUL!**

# TC110G Series Gate Array?

Part No.: TC110G 51 Used Gates: 15000 Gates

## **TC110G Series Library**

TC17G series-compatible macrocells and macrofunctions

- Macrocell performance optimization (Standard/High drive)

- Macrocell equivalent to SSI/MSI

Functional block of Megacells, Megafunctions

●2900 family

## **Macrocells**

| Logic Gate                  | 62  |

|-----------------------------|-----|

| Inverter/Internal Buffer    | 15  |

| Tri-state Internal Buffer   | 6   |

| Latch                       | 22  |

| Flip-flop                   | 36  |

| Decoder                     | 8   |

| Multiplexer                 | 14  |

| Adder                       | 6   |

| Input Buffer                | 48  |

| Output Buffer               | 40  |

| Bidirectional Output Buffer | 324 |

| Total                       | 581 |

## ●Multiplier, Barrelshifter, ALU, CLA, FIFO

●LSI/VLSI CPU Peripheral

Building-block memory (32 to 16K bit)

●RAM cell: 3 gates ●ROM cell: 1/4 gate

Customer-defined architecture

## **Macrofunction List**

|              | Ту                | pes                       |

|--------------|-------------------|---------------------------|

| Function     | LSI<br>Compatible | 74HC Series<br>Compatible |

| ADDERS       | 4                 | 11                        |

| COMPARATORS  | 6                 | 2                         |

| COUNTERS     | 19                | 11                        |

| DECODERS     | 10                | 4                         |

| FLIP-FLOPS   | _                 | 6                         |

| GATES        | _                 | 16                        |

| MULTIPLEXERS | 11                | 10                        |

| REGISTERS    | 19                | 16                        |

| OTHERS       | 8                 | 7                         |

| Total        | 77                | 73                        |

## **RAM**

| RAM-C<br>SINGLE<br>PORT<br>RAM     | ● Asynchronous ● Separated I/O, 3 state Output ● Max. 4608 Bit/Block (8~256 Word×4~36 Bit) ● Read Access Time (tacc) 15ns typ.                                     |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAM-E<br>(TRIPLE)<br>(PORT)<br>RAM | <ul> <li>◆Asynchronous</li> <li>◆2 Read 1 Write</li> <li>◆Max. 1152 Bit/Block</li> <li>(16~64 Word×4~18 Bit)</li> <li>◆Read Access Time(tacc) 11ns typ.</li> </ul> |

## **ROM**

| ROM-A   | ●Asynchronous                     |

|---------|-----------------------------------|

| /SINGLE | ●Max. 16384 Bit/Block             |

| PORT    | (64~1024 Word×2~32 Bit)           |

| \ROM /  | ●Read Access Time(tacc) 18ns typ. |

|         |                                   |

#### **Features**

- Proprietary 1.5μm HC²MOS/VLSI process technology.

0.6ns speed (2-input NAND gate, fanout = 2, tpd.)

- Achieves ultra high speed equivalent to 10K ECL.

- High packing density up to 129K raw gates.

- •3K to 129K raw gates.

- ●Up to 256 I/O pins.

- ◆Variable channel width architecture allows efficient silicon utilization.

- ●Full input/output TTL/CMOS compatibility.

- Advanced packaging techniques.

- ●Design is fully supported by TOSHIBA MAINFRAME CAD SYSTEM ●Programmable I/O cells with slew rate control (e.g. Output drive up to 12mA).

- Large macro capability (e.g. RAMs, ROMs, Megafunctions, Megacells\*).

- Performance optimization (e.g. Standard/High drive cells).

- \*: Scheduled to be released gradually.

## **TC110G Series Base Array**

- Variable routing track and column

- ●Max. 129K raw gates (1 raw gate = 2 pairs of Pch./Nch. transistor = 4 transistors)