# 82C206 INTEGRATED PERIPHERALS CONTROLLER

- 100% Compatible to IBM™ PC AT

- Fully compatible to Intel™s 8237 DMA controller, 8259 Interrupt controller, 8254 Timer/Counter, and Motorola™s 146818 Real Time Clock

- Offers 7 DMA channels, 13 Interrupt request channels, 2 Timer/Counter channels, and a Real Time Clock

- Reduced recovery time (120 ns) between control

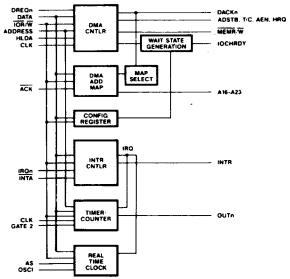

The 82C206 Integrated Peripheral Controller incorporates two 8237 DMA controllers, two 8259 Interrupt controllers, one 8254 Timer/ Counter, one MC146818 Real Time Clock, 74LS612 memory mapper, in addition to several other TTL/SSI interface logic chips to offer a single chip integration of all the peripherals attached to the peripheral bus (X-Bus) in the IBM'\* PC AT'\* While offering a complete compatibility to the IBM PC AT architecture, the chip offers enhanced features and improved speed performance. These include an additional 64 bytes of user RAM for the Real Time Clock, and drastically reduced recovery specifications for the 8237,

- 114 bytes of CMOS RAM memory

- 8 MHz DMA clock with programmable internal divider for 4 MHz operation

- Programmable wait states for the DMA cycle

- 16 Mbytes DMA address space

- Single chip 84-pin CMOS implementation

8259 and 8254. Variable wait state option is provided for the DMA cycles. Programmable delays are provided for the CPU access to the internal registers of the chip. The chip also provides an option to select 8 or 4 MHz system clock.

The 82C206, along with the CS8220 PC AT Compatible CHIPSet, provides a highly integrated high performance solution for a PC AT compatible implementation.

The 82C206 is implemented using advanced CMOS technology and is packaged in an 84-pin PLCC.

Figure 1. 82C206 Integrated Peripheral Controller Block Diagram

# CHIP5

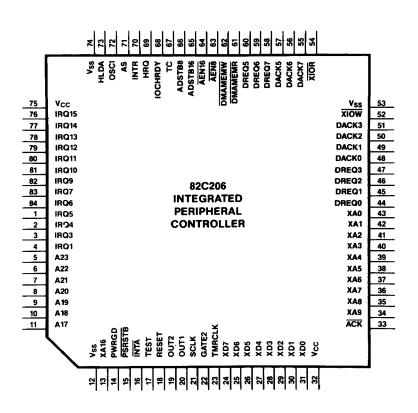

# 82C206 Pin Description

| Pin No. | Name    | Type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24-31   | XD7-XD0 | 1/0  | DATA BUS: The Data Bus lines are 3-state bi-directional lines connected to the system data bus (XD bus in a PC/AT design). The outputs are enabled in the program condition during the I/O Read to output the contents of the DMA controller registers (Address register, Status register, the Temporary register or a Word Count register), the three Interrupt Controller registers (Interrupt Request register, In Service register and the Interrupt Mask register), the Timer/Counters registers (namely the contents of these counters or states of the counters), the Real Time Clocks internal registers and page registers of memory mapper. |

|         |         |      | During an I/O write cycle, the outputs are disabled and the CPU can program the DMA Controller registers, the Interrupt Controller registers, the Timer/Counters registers, the DMA Page register and the Real Time Clock registers and internal RAM.                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |         |      | During DMA cycles, the most significant 8 bits of the address are output onto the data bus to be strobed into an external latch by ADSTB8 or ADSTB16. During memory-to-memory operations, data from the memory comes into the DMA Controller on the data bus during read from the memory. In the write to memory transfer, the data bus outputs place the data into the new memory location.                                                                                                                                                                                                                                                          |

|         |         |      | During the interrupt sequence, the interrupt controllers output the interrupt vector byte on the data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         |         |      | Data bus XD7-XD0 also acts as the multiplexed address/data bus for the Real Time Clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Pin No.     | Name           | Туре     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|----------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35-43<br>34 | XA8-XA0<br>XA9 | I/O<br>I | ADDRESS BUS: This is the system address bus used to address various registers of the 82C206. It is tied to the external bus (XA bus) in a PC/AT compatible design. During a non-DMA cycle, A3-A0 act as inputs and are used by the CPU to address the registers of the DMA Controller corresponding to DMA channels 0-3 and A4-A1 address the registers of the DMA Controller corresponding to DMA channels 5-7. In the active DMA cycle, A7-A0 are outputs and carry address information for DMA channels 0-3. Correspondingly, A8-A1 are address outputs for 16 bit DMA channels 5-7. During program condition, A9-A0 are used to address configuration register and the internal registers of DMA Controller, INT Controller, Timer, RTC and Memory Mapper. |

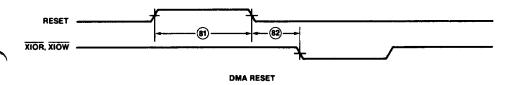

| 18          | RESET          | l        | RESET: Reset is active high input which affects the following registers:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             | •              |          | DMA Controllers: Clears the Command, Status, DMA Request, Temporary register, First/Last flip-flop; sets the Mask register. Following reset, the DMA controller is in an idle state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             |                |          | INTERRUPT Controllers: Clears the edge sense circuit, the interrupt mask register, all ICW4 functions, IRQ0 is assigned highest priority, slave address is set to 7, special mask mode is disabled and status read is set to IRR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

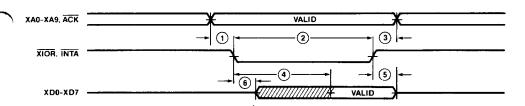

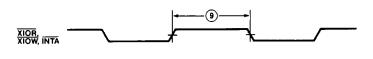

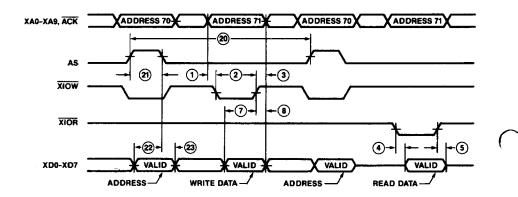

| 54          | XIOR           | I/O      | I/O READ: I/O Read is a bidirectional active low three-state line. In an idle cycle (non DMA, non-interrupt), it is an input control signal used by the CPU to read the 82C206 internal registers. In an active DMA cycle, it is an output control signal used by the DMA Controller to access data from a peripheral during a DMA write transfer.                                                                                                                                                                                                                                                                                                                                                                                                             |

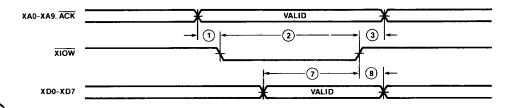

| 52          | XIOW           | I/O      | I/O WRITE: I/O Write is a bidirectional active low three-state signal. In an idle cycle (non-DMA, non-interrupt) it is an input control signal used by the CPU to load information to the 82C206 internal registers. In an active DMA cycle, it is an output control signal used by the DMA Controller to load data to the peripheral during a DMA Read transfer.                                                                                                                                                                                                                                                                                                                                                                                              |

| 61          | DMAMEMR        | 0        | DMA MEMORY READ: DMAMEMR is an active low three-state output used to access data from the selected memory location during DMA Read or memory-to-memory transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Pin No. | Name    | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 62      | DMAMEMW | 0    | DMA MEMORY WRITE: DMAMEMW is an active low three-state output used to write data to the selected memory location during DMA write or a memory-to-memory transfer. In a PC/AT compatible design, this signal is connected to XMEMW.                                                                                                                                                                                                                                                                                                                                                             |

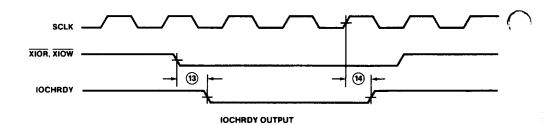

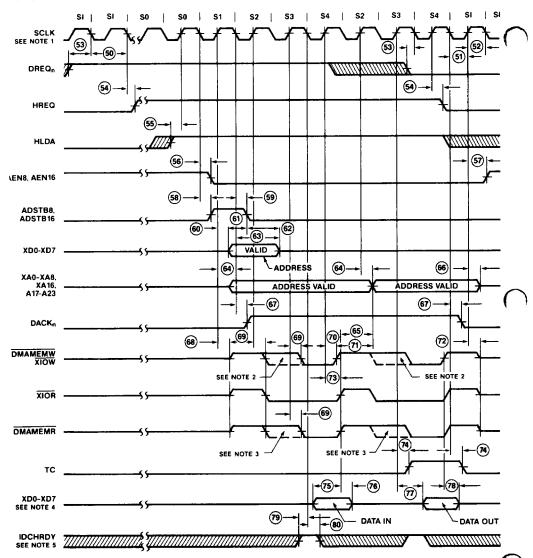

| 21      | SCLK    | I    | CLOCK INPUT: The Clock Input is used to generate the timing signals which control DMA operations. This input may be driven from DC to 10 MHz. The Clock may be stopped in either state for standby operation. The internal clock used for DMAC is either the SCLK or SCLK/2 depending on the setting of DMA CLOCK SELECT bit in the configuration register.                                                                                                                                                                                                                                    |

| 68      | IOCHRDY | 1/0  | I/O CHANNEL READY: In the input mode, a low on IOCHRDY causes the internal DMA ready signal to go low asynchronously. When IOCHRDY goes high, one DMA Clock cycle will elapse before internal DMA Ready goes up. This signal is used to extend memory read and write pulses for the DMA controllers to accommodate slow memories or I/O devices. IOCHRDY must satisfy set-up and hold times with respect to DMACLK in order to work reliably.                                                                                                                                                  |

|         |         |      | In the output mode, this pin is an open drain output and provides an active low output whenever any 82C206 register is addressed for read or write. This output will remain low for a programmed number of DMACLK cycles (as configured by bits 6 and 7 of 82C206 configuration register) and then goes high, if pulled up by an external register. IOCHRDY provides a means of introducing a programmed number of wait-states (as counted by DMACLK cycles) for I/O read/write cycles to 82C206. In a PC/AT architecture based design this pin should be wire-ored to PC/AT's IOCHRDY signal. |

| 73      | HLDA    | ł    | HOLD ACKNOWLEDGE: The active high Hold Acknowledge from the CPU indicates that it has relinquished control of the system busses.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

5

| Pin No.                | Name                               | Type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------|------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44-<br>47<br>60-<br>58 | DREQ0-<br>DREQ3<br>DREQ5-<br>DREQ7 | ı    | DMA REQUEST: The DMA Request (DREQ) are individual asynchronous channel request inputs used by peripheral circuits to obtain DMA service. In Fixed Priority, DREQ0 has the highest priority and DREQ7 has the lowest priority. A request is generated by activating the DREQ line of a channel. DACK will acknowledge the recognition of DREQ signal. Polarity of DREQ is programmable. Reset initializes these lines to active high. DREQ must be maintained until the corresponding DACK goes active. DREQ will not be recognized while the clock is stopped. Unused DREQ inputs should be pulled High or Low (inactive) and the corresponding mask bit set. |

|                        |                                    |      | DREQ0-DREQ3 support 8-bit transfers between 8-bit I/O and 8 or 16-bit system memory. DREQ5-DREQ7 support 16-bit data transfers between 16-bit peripheral and 16-bit system memory. DREQ4 is not available as it is used to cascade DREQ0-DREQ3.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 67                     | тс                                 | 0    | TERMINAL COUNT: Terminal Count (TC) is an active high signal. Information concerning the completion of DMA services is available at the TC output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        |                                    |      | A pulse is generated by the DMA Controller when terminal count (TC) for any channel is reached, except for channel 0 in memory-to-memory mode. During memory-to-memory transfers TC will be output when the TC for channel 1 occurs.                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                        |                                    |      | When a TC pulse occurs, the DMA Controller will terminate the service, and if auto-initialize is enabled, the base registers will be written to the current registers of that channel. The mask bit and TC bit in the status word will be set for the currently active channel unless the channel is programmed for auto-initialize. In that case, the mask bit remains clear.                                                                                                                                                                                                                                                                                 |

| Pin No.                | Name                               | Type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------|------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 69                     | HRQ                                | 0    | HOLD REQUEST: The Hold Request (HRQ) output is used to request control of the system bus. When a DREQ occurs and the corresponding mask bit is clear, or a software DMA request is made, the DMA Controller issues HRQ. The HLDA signal then informs the controller when access to the system busses is permitted. For stand-alone operation where the DMA Controller always controls the busses, HRQ may be tied to HLDA. This will result in one SO state before the transfer. |

| 48-<br>51<br>57-<br>55 | DACK0-<br>DACK3<br>DACK5-<br>DACK7 | 0    | DMA ACKNOWLEDGE: DMA Acknowledge is used to notify the individual peripherals when one has been granted a DMA cycle. The active polarity of these lines is programmable. Reset initializes them to active low. Because these signals are used internally for cascading the DMA channels and for DMA page register selection, these signals must be programmed to be active low.                                                                                                  |

| 66                     | ADSTB8                             | 0    | ADDRESS STROBE: This is an active high signal used to control latching of the upper address byte (A8-A15) for 8-bit peripherals. It will drive directly the strobe input of external transparent octal latches. During block operations, ADSTB8 will only be issued when the upper address byte must be updated, thus speeding operation through elimination of S1 states. ADSTB8 is active for DMA channels 0-3.                                                                |

| 64                     | AEN16                              | 0    | ADDRESS ENABLE for 16-BIT DMA TRANSFERS: This signal enables the 8-bit latch containing the upper 8 address bits (A9-A16) on to system address bus. It is inactive when external bus master controls the system bus (MASTER=0). This signal is active low.                                                                                                                                                                                                                       |

| 65                     | ADSTB16                            | 0    | ADDRESS STROBE for 16-BIT TRANSFERS (channels 5-7). This is an active high signal used to control latching of the upper address byte A9-A16 for 16-bit DMA transfers. Its function is just like ADSTB8.                                                                                                                                                                                                                                                                          |

| 63                     | AEN8                               | 0    | ADDRESS ENABLE for 8-BIT DMA TRANSFERS: This signal is the output enable for the 8-bit latch containing upper 8 address bits (A8-A15). It enables A8-A15 system address bus. It is inactive when external bus master controls the system bus (MASTER=0). This signal is active low.                                                                                                                                                                                              |

| Pin No.                | Name                                          | Type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------|-----------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33                     | ACK (MSE)                                     | 1    | MODULE SELECT ENABLE: When high, it enables the chip select function on one of the modules (DMA Controller, INT Controler, TIMER, RTC, DMA Page register or the Configuration register) for the programming function, i.e. CPU read or write of the command, status or other register of various modules of the 82C206. When low, the 82C206 is essentially disconnected from the system bus. The 82C206 at this time could be performing an active DMA or an interrupt cycle. In a PC/AT compatible design, this pin is tied to ACK signal. |

| 11-5<br>13             | A23-A17<br>XA16                               | 0    | DMA PAGE REGISTER ADDRESS: XA16 and A17-A23 are 3-state output pins. XA16 is the least significant bit of the DMA page register and is used for DMA transfers for 8-bit peripherals only (channel 0-3). XA16 is not used for DMA transfers to 16-bit peripherals (channel 5-7) as XA9-XA16 is provided by demultiplexing the data bus. A17-A23 are the upper 7 bits of the DMA page register.                                                                                                                                                |

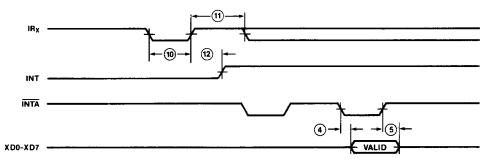

| 76-82<br>83, 84<br>1-3 | IRQ15-IRQ9<br>IRQ7, IRQ6<br>IRQ5-IRQ3<br>IRQ1 | <br> | INTERRUPT REQUESTS: Asynchronous inputs. An interrupt request is executed by raising an IRQ input low to high and holding it high until it is acknowledged (edge triggered mode) or just a high level on an IRQ input (level triggered mode).                                                                                                                                                                                                                                                                                                |

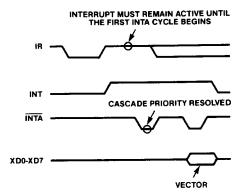

| 16                     | ĪNTĀ                                          | I    | INTERRUPT ACKNOWLEDGE: This pin is used to enable the interrupt controllers interrupt vector data on to the data bus by a sequence of interrupt acknowledge pulses issued by the CPU.                                                                                                                                                                                                                                                                                                                                                        |

| 70                     | INTR                                          | 0    | INTERRUPT: This pin goes high whenever a valid interrupt request is asserted. It is used to interrupt the CPU, and is usually connected to the CPU's interrupt pin.                                                                                                                                                                                                                                                                                                                                                                          |

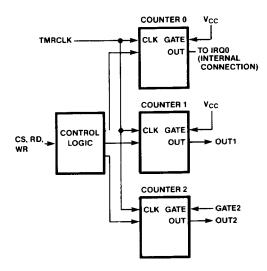

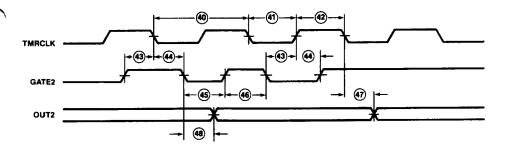

| 23                     | TMRCLK                                        | 1    | TIMER CLOCK: Clock input for Counter 0, Counter 1 and Counter 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 22                     | GATE2                                         | 1    | GATE 2: Gate input for Counter 2. In a PC/AT compatible design, the Counter 2 is used for tone generation for speaker. In this design, the GATE 2 input is driven by Bit 0 of I/O Port 61H (called TIM2GATE SPK).                                                                                                                                                                                                                                                                                                                            |

| 20                     | OUT1                                          | 0    | OUT 1: Output of Timer 1. In a PC/AT compatible design, Timer 1 is programmed as a rate generation to produce 15 µsec period signal used for interrupt request for refresh cycles.                                                                                                                                                                                                                                                                                                                                                           |

| 19                     | OUT 2                                         | 0    | OUT 2: Output of Timer 2. In a PC/AT compatible design, OUT 2 is used to drive the speaker.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Pin No.    | Name            | Туре | Function                                                                                                                                                                                          |  |  |

|------------|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 71         | AS              | l    | ADDRESS STROBE: Address strobe is a positive pulse whose falling edge latches the address from the XD bus.                                                                                        |  |  |

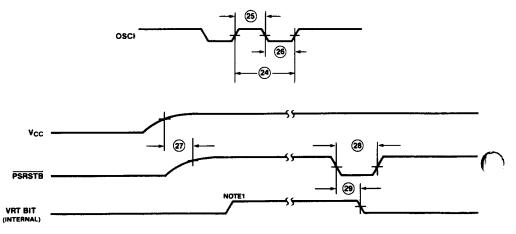

| 72         | OSCI            | ı    | OSCILLATOR INPUT: The time base for the time functions is connected to this pin. External square waves of 32.768 KHz may be connected to this input.                                              |  |  |

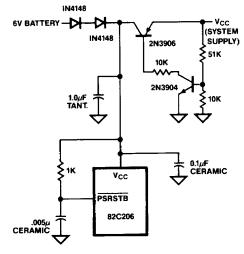

| 15         | PSRSTB          | I    | This input is used to establish the condition of the control registers when power is applied to the device. In a PC/AT compatible design, this pin should be tied to the battery back-up circuit. |  |  |

|            |                 |      | When PSRSTB and TEST are both low, the following occurs:                                                                                                                                          |  |  |

|            |                 |      | <ul><li>(a) Periodic Interrupt Enable (PIE) bit is cleared to<br/>zero.</li></ul>                                                                                                                 |  |  |

|            |                 |      | (b) Alarm Interrupt Enable (AIE) bit is cleared to<br>zero.                                                                                                                                       |  |  |

|            |                 |      | (c) Update ended Interrupt Enable (UIE) bit is<br>cleared to zero.                                                                                                                                |  |  |

|            |                 |      | <ul><li>(d) Update ended Interrupt Flag (UF) bit is cleared<br/>to zero.</li></ul>                                                                                                                |  |  |

|            |                 |      | (e) Interrupt Request status Flag (IRQF) is cleared to zero.                                                                                                                                      |  |  |

|            |                 |      | (f) Periodic Interrupt Flag (PF) bit is cleared to<br>zero.                                                                                                                                       |  |  |

|            |                 |      | (g) The part is not accessible.                                                                                                                                                                   |  |  |

|            |                 |      | (h) Alarm interrupt Flag (AF) bit is cleared to zero.                                                                                                                                             |  |  |

|            |                 |      | (i) Square Wave output enable list is cleared to zero.                                                                                                                                            |  |  |

| 14         | PWRGD           | i    | PWRGOOD: The Power Good pin must be high for bus cycles in which the CPU accesses the RTC. When PWRGD is low, all address, data, data strobe and R/W pins are disconnected from the processor.    |  |  |

| 17         | TEST            | ı    | TEST: Test is an active high input. It initializes various internal registers so that the test program starts in a known state. It should be tied low for normal operation.                       |  |  |

| 32, 75     | V <sub>cc</sub> |      | Power Supply                                                                                                                                                                                      |  |  |

| 12, 53, 74 | V <sub>SS</sub> | _    | Ground                                                                                                                                                                                            |  |  |

|            |                 |      |                                                                                                                                                                                                   |  |  |

# 82C206—INTEGRATED PERIPHERALS CONTROLLER

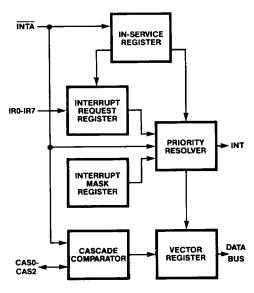

The 82C206 is a LSI implementation of the standard peripherals required to implement an IBM PC/AT system board. This device contains the equivalent of two 8237A DMA Controllers, a 74LS612 Mapper, two 8259A Interrupt Controllers, an 8254 Counter/Timer, and a MC146818 Real Time Clock with RAM. The 82C206 provides all of the standard peripherals required for a system board implementation except the keyboard interface controller. Figure 1 illustrates the subsystems contained within the 82C206.

Two DMA Controllers are provided and connected in such a way as to provide the user with four channels of DMA (DMA1) for 8-bit transfers and three channels of DMA (DMA2) for 16-bit transfers (the first 16-bit DMA channel is used for cascading). Included as part of the DMA subsystem is the Page Register (DMAPAGE) device which is used to supplement the DMA and drive the upper address lines when required.

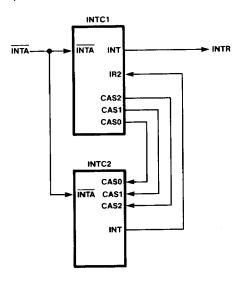

Sixteen channels of interrupt are provided in the 82C206. These channels are partitioned into two cascaded controllers (INTC1,INTC2) with 8 inputs each. Of these 16 channels, three are connected internally to various devices, allowing 13 user definable channels of interrupt. The three internally connected channels are as follows:

Channel 0 — Counter/Timer Counter 0

Interrupt

Channel 2 — Cascade to Slave Interrupt Controller (INTC2)

Channel 8 - Real Time Clock Interrupt

The remaining 13 channels may be defined and utilized as necessary to meet the users specific system requirements.

A Counter/Timer (CTC) subsystem is provided which contains three independent counters. All three counters are driven from a clock input pin which is independent from the other clock inputs to the device. Counter 0 is connected to Interrupt 0 of INTC1. It is intended to be used as a multi-level interrupt

to the system for such tasks as time keeping and task switching. Counter 1 may be programmed to generate pulses or square waves for use by external devices. The third channel (Counter 2) is a full function Counter/Timer which has a gate input for controlling the internal counter. This channel can be used as an interval counter, a timer, or as a gated rate/pulse generator.

A Real Time Clock (RTC) is included in the 82C206 for maintaining the time and date. This subsystem also contains 114 bytes of RAM in addition to the Clock/Calendar. The Clock/Calendar information and RAM are kept active by connecting the device to an external battery when system power is turned off.

To interconnect and control all of these major subsystems a top level control section is employed which is divided into subsystems for purposes of discussion.

The first section is the Clock and Wait State Control section. This subsystem controls the generation of DMA wait states and the negation of IOCHRDY (if programmed to do so) during CPU access of the device. The last subsystem is the Top Level Decode.

In order to accommodate over 200 registers in the 82C206 and maintain I/O decode compatibility with the IBM PC/AT, a multilevel decode scheme is employed. The Top Level Decode subsystem performs the function of generating enables to the various subsystems. Control and direction of the XD0-XD7 data bus buffers are also handled by this subsystem.

Each of these subsystems will now be described separately.

### Top Level Decode

The 82C206 Top Level Decode provides 8 separate enables to various subsystems of the device. Figure 2 contains a truth table for the Top Level Decoder. The enabling of the 82C206 XD0-XD7 output buffers is also controlled by this section. The output buffers are enabled whenever an enable is generated to an internal subsystem and the XIOR signal is asserted.

| ACK | XA9 | XA8 | XA7 | XA6 | XA5 | XA4 | ХАЗ | XA2 | XA1 | XAO | ADDRESS<br>RANGE(Hex) | SELECTED DEVICE |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----------------------|-----------------|

| 1   | 0   | 0   | 0   | 0   | 0   | 0   | Х   | Х   | X   | Х   | 000-00F               | DMA1            |

| 1   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 0   | Х   | 020-021               | INTC1           |

| 1   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 1   | Х   | 022-023               | CONFIG          |

| 1   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 0   | Х   | Х   | 040-043               | СТС             |

| 1   | 0   | 0   | 0   | 1   | 1   | 1   | 0   | 0   | 0   | 1   | 071                   | RTC             |

| 1   | 0   | 0   | 1   | 0   | 0   | 0   | х   | Х   | Х   | Х   | 080-08F               | DMAPAGE         |

| 1   | 0   | 0   | 1   | 0   | 1   | 0   | 0   | 0   | 0   | Х   | 0A0-0A1               | INTC2           |

| 1   | 0   | 0   | 1   | 1   | 0   | Х   | х   | Х   | Х   | Х   | 0C0-0DF               | DMA2            |

| 0   | X   | Х   | X   | Х   | Х   | Х   | Х   | X   | X   | Х   | DISAB                 | LED             |

| X   | 1   | Х   | ×   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | DISAB                 | LED             |

|     |     | 1   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | DISAB                 | LED             |

Figure 2. 82C206 Internal Decode

The decoder is enabled by three signals. These three signals are ACK, XA9 and XA8. To enable any internal device ACK must be "1" and both XA9 and XA8 must be "0".

The decode scheme employed in the 82C206 is designed to comply with the IBM PC/AT requirements and is more fully decoded. If the user wishes to take advantage of the areas which are unused by inserting additional peripherals in the I/O map, he may do so since the subsystems in the 82C206 will not respond to the unused address spaces established by the Top Level Decoder. The extra peripherals may be tied directly to the XD0-XD7 data lines since the 82C206 output buffers are not enabled unless an internal subsystem is enabled.

### Clock and Wait State Control

The Clock and Wait State Control subsystem performs four functions, control of the DMA command width, control of the CPU read or write cycle length, and selection of the DMA clock rate. All of these functions are user selectable by writing to the Configuration Register located at address 023H.

Writing and reading this register is accomplished by first writing a 01H to location 022H to select the 82C206 Configuration

Register, and then performing either a read or write to location 023H.

Configuration Register (023H) (Index 01H)

| msb |     |      |      |     |     |     | Isb |

|-----|-----|------|------|-----|-----|-----|-----|

| b7  | b6  | b5   | b4   | b3  | b2  | b1  | ь0  |

| RW1 | RW0 | 16W1 | 16W0 | 8W1 | 8W0 | EMR | CLK |

RW1-RW0—When the higher speed CPU's are accessing the 82C206, the cycle can be extended by programming up to four wait states into the Configuration Register. This will cause the 82C206 to assert a not ready condition on IOCHRDY (low) whenever a valid decode from the Top Level Decoder is detected and either XIOR or XIOW is asserted. IOCHRDY will remain low for the number of wait states programmed into the Configuration Register bits 6 and 7.

| RW1 | RW0 | Read/Write Cycle Wait States |

|-----|-----|------------------------------|

| 0   | 0   | 1                            |

| 0   | 1   | 2                            |

| 1   | 0   | 3                            |

| 1   | 1   | 4                            |

Wait states are in increments of one SCLK cycle and are not affected by the DMA Clock Divider.

16W1-16W0—Wait states can be independently controlled for both 8-bit and 16-bit DMA cycles. This allows the user to tailor the DMA cycle more closely to the application.

| 16W1 | 16W0 | 16-Bit DMA Wait States |

|------|------|------------------------|

| 0    | 0    | 1                      |

| 0    | 1    | 2                      |

| 1    | 0    | 3                      |

| 1    | 1    | 4                      |

**8W1-8W0**—Wait states may be inserted in 8-bit DMA cycles by programming these two bits in the Configuration Register.

| 8W1 | 8W0 | 8-Bit DMA Wait States |

|-----|-----|-----------------------|

| 0   | 0   | 1                     |

| 0   | 1   | 2                     |

| 1   | 0   | 3                     |

| 1   | 1   | 4                     |

Further control of the cycle length is available through the use of the IOCHRDY pin on the 82C206. During DMA this pin is used as an input to the wait state generation logic to extend the cycle if necessary. This input is driven low (0) by the peripheral to extend the cycle. The cycle can then be completed by releasing IOCHRDY and allowing it to return high (1).

EMR—This bit enables the extended DMAMEMR function. Normally the assertion of DMAMEMR is delayed one clock cycle later than XIOR in the IBM PC/AT implementation. This may not be desirable in some systems. A "1" programmed into this bit position will start DMAMEMR at the same time as XIOR.

CLK—This bit allows the user to insert a divider between the DMA Controller subsystems and the SCLK input pin, or connect the two directly. When this bit position contains a "0", the SCLK input is divided by two and is used to drive both the 8-bit and 16-bit DMA subsystems. A "1" in this position bypasses the divider and uses the SCLK input directly. Whenever the state of this bit is changed, an

internal synchronizer controls the actual switching of the clock to prevent a short clock pulse from causing a DMA malfunction.

The Configuration Register contents are preloaded by RESET to an initial value of 0C0 hex. This value establishes a default which is IBM PC/AT compatible and corresponds to:

Read/Write cycles —4 wait states

16-bit DMA transfers -1 wait state

8-bit DMA transfers -1 wait state

DMAMEMR delayed 1 DMA clock cycle later than XIOR

DMA clock is equal to SCLK/2

## **DMA FUNCTIONAL DESCRIPTION**

The equivalent of two 8237A DMA Controllers is implemented in the 82C206. Each controller is a four channel DMA device which will generate the memory addresses and control signals necessary to transfer information between a peripheral device and memory directly. This allows high speed information transfer with little CPU intervention.

The two DMA Controllers are internally cascaded to provide four DMA channels for transfers to 8-bit peripherals (DMA1), and three channels for transfers to 16-bit peripherals (DMA2). DMA2 Channel 0 privides the cascade interconnection of the two DMA devices, thereby maintaining IBM PC/AT compatibility.

DMA cycle length control is provided internally in the 82C206 allowing independent control for both 8-bit and 16-bit cycles. This is done through the programmable registers which can extend command signals or insert wait states.

Each DMA Channel has a pair of 16-bit counters and a reload register for each counter. The 16-bit counters allow the DMA to transfer blocks as large as 65536 words. The register associated with each counter allows the channel to reinitialize without reprogramming.

From this point on the description of the DMA subsystem pertains to both DMA1 and DMA2 unless otherwise noted.

# **DMA Operation**

During normal operation of the 82C206, the DMA subsystem will be in either the Idle condition, the Program condition or the Active condition. In the Idle condition the DMA controller will be executing cycles consisting of only one state. The idle state SI is the default condition and the DMA will remain in this condition unless the device has been initalized and one of the DMA requests is active or the CPU attempts to access one of the internal registers.

When a DMA request becomes active the device enters the Active condition and issues a hold request to the system. Once in the Active condition the 82C206 will generate the necessary memory addresses and command signals to accomplish a memory-to I/O, I/Oto-memory, or a memory-to-memory transfer. Memory-to-I/O and I/O-to-memory transfers take place in one cycle while memory-tomemory transfers require two cycles. During transfers between memory and I/O, data is presented on the system bus by either memory or the requesting device and the transfer is completed in one cycle. Memory-tomemory transfers however, require the DMA to store data from the read operation in an internal register. The contents of this register is then written to memory on the subsequent cycle.

During transfers between memory and I/O, two commands are activated during the same cycle. In the case of a memory-to-I/O transfer, the 82C206 will assert both DMAMEMR and XIOW allowing data to be transfered directly to the requesting device from memory. Note that 82C206 does not latch data from nor drive data out on this type of cycle.

The number of clock cycles required to transfer a word of data may be varied by programing the DMA or, optionally extended by the peripheral device. During an Active cycle the DMA will sequence through a series of states. Each state will be one DMA clock cycle in

length and the number of states in a cycle will vary depending on how the device is programmed and what type of cycle is being performed. The states are labeled S0-S4 and will be explained in detail in the section entitled Active Condition.

#### **Idle Condition**

When no device is requesting service the DMA is in an Idle condition which maintains the state machine in the SI state. During this time the 82C206 will sample the DREQ input pins every clock cycle. The internal select from the top level decoder and HLDA are also sampled at the same time to determine if the CPU is attempting to access the internal registers. When either of the above two situations occurs, the DMA will exit the Idle condition. Note that the Program condition has priorit over the Active condition since a CPU cycle has already started.

## **Program Condition**

The Program condition is entered whenever HLDA is inactive and an internal select is active. The internal select is derived from the top level decode described previously. During this time address lines XA0-XA3 become inputs if DMA1 is selected, or XA1-XA4 become inputs if DMA2 is selected. Note, when DMA2 is selected XA0 is ignored. These address inputs are used to select the DMA controller registers which are to be read or written. Figure 3 lists the register address assignment. Due to the large number of internal registers in the DMA subsystem, an internal flip-flop is used to supplement the addressing of the count and address registers. This bit is used to select between the high and low bytes of these registers. The flip-flop will toggle each time a read or write occurs to any of the word count or address registers in the DMA. This internal flip-flop will be cleared by hardware RESET or a Master Clear command and may be set or cleared by the CPU issuing the appropriate command.

Special commands are supported by the DMA subsystem in the Program condition to control the device. These commands do not make use of the data bus but are derived from a set of addresses, the internal select and XIOW or

|       |      | •    |      |               |                                                                      |

|-------|------|------|------|---------------|----------------------------------------------------------------------|

| DMA1  | DMA2 | XIOR | XIOW | Flip-<br>Flop | Register Function                                                    |

| 000h  | 0C0h | 0    | 1    | 0             | Read Channel 0 Current Address Low Byte                              |

|       |      | 0    | 1    | 1             | Read Channel 0 Current Address High Byte                             |

|       |      | 1    | 0    | 0             | Write Channel 0 Base and Current Address Low Byte                    |

|       |      | 1    | 0    | 1             | Write Channel 0 Base and Current Address High Byte                   |

| 001h  | 0C2h | 0    | 1    | 0             | Read Channel 0 Current Word Count Low Byte                           |

|       |      | 0    | 1    | 1             | Read Channel 0 Current Word Count High Byte                          |

|       |      | 1    | 0    | 0             | Write Channel 0 Base and Current Word Count Low By                   |

|       |      | 1    | 0    | 1             | Write Channel 0 Base and Current Word Count High Byt                 |

| 002h  | 0C4h | 0    | 1    | 0             | Read Channel 1 Current Address Low Byte                              |

|       |      | 0    | 1    | 1             | Read Channel 1 Current Address High Byte                             |

|       |      | 1    | 0    | 0             | Write Channel 1 Base and Current Address Low Byte                    |

|       |      | 1    | 0    | 1             | Write Channel 1 Base and Current Address High Byte                   |

| 003h  | 0C6h | 0    | 1    | 0             | Read Channel 1 Current Word Count Low Byte                           |

|       |      | 0    | 1    | 1             | Read Channel 1 Current Word Count High Byte                          |

|       |      | 1    | 0    | 0             | Write Channel 1 Base and Current Word Count Low By                   |

|       |      | 1    | 0    | 1             | Write Channel 1 Base and Current Word Count High By                  |

| 004h  | 0C8h | 0    | 1    | 0             | Read Channel 2 Current Address Low Byte                              |

|       |      | 0    | 1    | 1             | Read Channel 2 Current Address High Byte                             |

|       |      | 1    | 0    | 0             | Write Channel 2 Base and Current Address Low Byte                    |

|       |      | 1    | 0    | 1             | Write Channel 2 Base and Current Address High Byte                   |

| 005h  | 0CAh | 0    | 1    | 0             | Read Channel 2 Current Word Count Low Byte                           |

|       |      | 0    | 1    | 1             | Read Channel 2 Current Word Count High Byte                          |

|       |      | 1    | 0    | 0             | Write Channel 2 Base and Current Word Count Low By                   |

|       |      | 1    | 0    | 1             | Write Channel 2 Base and Current Word Count High By                  |

| 006h  | 0CCh | 0    | 1    | 0             | Read Channel 3 Current Address Low Byte                              |

|       |      | 0    | 1    | 1             | Read Channel 3 Current Address High Byte                             |

|       |      | 1    | 0    | 0             | Write Channel 3 Base and Current Address Low Byte                    |

|       |      | 1    | 0    | 1             | Write Channel 3 Base and Current Address High Byte                   |

| 007h  | 0CEh | 0    | 1    | 0             | Read Channel 3 Current Word Count Low Byte                           |

|       |      | 0    | 1    | 1             | Read Channel 3 Current Word Count High Byte                          |

|       |      | 1    | 0    | 0             | Write Channel 3 Base and Current Word Count Low Byt                  |

|       |      | 1    | 0    | 1             | Write Channel 3 Base and Current Word Count High Byt                 |

| 008h  | 0D0h | 0    | 1    | Х             | Read Status Register                                                 |

|       |      | 1    | 0    | Х             | Write Command Register                                               |

| 009h  | 0D2h | 0    | 1    | Х             | Read DMA Request Register                                            |

|       |      | 1    | 0    | Х             | Write DMA Request Register                                           |

| 00Ah  | 0D4h | 0    | 1    | Х             | Read Command Register                                                |

|       |      | 1    | 0    | Х             | Write Single Bit DMA Request Mask Register                           |

| 00Bh  | 0D6h | 0    | 1    | Х             | Read Mode Register                                                   |

|       |      | 1    | 0    |               | Write Mode Register                                                  |

| 00Ch  | 0D8h | 0    | 1    | Х             | Set Byte Pointer Flip-Flop                                           |

|       |      | 1    | 0    | Х             | Clear Byte Pointer Flip-Flop                                         |

| 00Dh  | 0DAh | 0    | 1    | Х             | Read Temporary Register                                              |

|       | 302  | 1    | ó    | x             | Master Clear                                                         |

| 00Eh  | 0DCh | 0    | 1    | X             | · · · · · · · · · · · · · · · · · · ·                                |

| VOE!) | JUCH | 1    | ó    | x             | Clear Mode Register Counter Clear All DMA Request Mask Register Bits |

|       |      |      |      |               |                                                                      |

| 00Fh  | 0DEh | 0    | 1    | Х             | Read All DMA Request Mask Register Bits                              |

|       |      | 1    | ò    | x             | Write All DMA Request Mask Register Bits                             |

Figure 3. DMA Registers

# CHIPS.

XIOR. These commands are Master Clear, Clear Mask Register, Clear Mode Register Counter, Set and Clear Byte Pointer Flip-Flop.

The 82C206 will enable programming whenever HLDA has been inactive for one DMA clock cycle. It is the responsibility of the system to ensure that programming and HLDA are mutually exclusive. Erratic operation of the 82C206 can occur if a request for service occurs on an unmasked channel which is being programmed. The channel should be masked or the DMA disabled to prevent the 82C206 from attempting to service a device with a channel which is partially programmed.

#### **Active Condition**

The 82C206 DMA subsystem enters the Active condition whenever a software request occurs or a DMA request on an unmasked channel occurs and the device is not in the Program condition. The 82C206 will then begin a DMA transfer cycle.

In a read cycle for example, after receiving a DREQ, the 82C206 will issue a HRQ to the system. Until a HLDA is returned the DMA will remain in an idle condition. On the next clock cycle the DMA will exit Idle and enter state S0. During S0 the device will resolve priority and issue DACK on the highest priority channel requesting service. The DMA will then proceed to state S1 where the multiplexed addresses are output and latched. State S2 is then entered, at which time the 82C206 will assert DMAMEMR. The device then transitions into S3 where the XIOW command is asserted. The 82C206 DMA will then remain in S3 until the Wait State Counter has decremented to zero and IOCHRDY is true. Note that at least one additional S3 will occur unless Compressed Timing is selected. Once a ready condition is detected, the DMA will enter S4 where both commands are deasserted. In Burst Mode and Demand Mode (discussed below), subsequent cycles will begin in S2 unless the intermediate addresses require updating. In these subsequent cycles the lower addresses are changed in S2.

The DMA can be programmed on a channel

by channel basis to operate in one of four modes. The four modes are listed below.

Single Transfer Mode—This mode directs the DMA to execute only one transfer cycle at a time. DREQ must be held active until DACK becomes active. If DREQ is held active throughout the cycle, the 82C206 will deassert HRQ and release the bus once the transfer is complete. After HLDA has gone inactive the 82C206 will again assert HRQ and execute another cycle on the same channel unless a request from a higher priority channel has been received. In this mode the CPU is ensured of being allowed to execute at least one bus cycle between transfers.

Following each transfer the word count is decremented and the address is incremented or decremented. When the word count decrements from 0000h to FFFFh the terminal count bit in the status register is set and a T/C pulse is generated. If the autoinitialization option has been enabled, the channel will reinitialize itself. If Autoinitialize is not selected the DMA will set the DMA request bit mask and suspend transfering on that channel.

Block Transfer Mode—When Block Transfer Mode is selected, the 82C206 will begin transfers in response to either a DREQ or a software request and will continue until a terminal count (FFFFh) is reached, at which time T/C is pulsed and the status register terminal count bit is set. In this mode DREQ need only be held active until DACK is asserted. Autoinitialization is optional in this mode also.

Demand Transfer Mode—In Demand Transfer mode the DMA will begin transfers in response to the assertion of DREQ and will continue until either terminal count is reached or DREQ becomes inactive. This mode is normally used for peripherals which have limited buffering ability. The peripheral can initiate a transfer and continue until its buffer capacity is exhausted. The peripheral may then re-establish service by again asserting DREQ. During idle periods between transfers the CPU is released to operate and can monitor the operation by reading intermediate values from the address and word count regis-

# CHIPS

ters. Once DREQ has been deasserted, higher priority channels are allowed to intervene. Reaching terminal count will result in the generation of a T/C pulse, the setting of the terminal count bit in the status register and autoinitialization (if enabled).

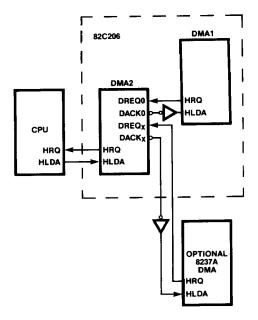

Cascade Mode-This mode is used to interconnect more than one DMA controller, to extend the number of DMA channels while preserving the priority chain. In Cascade mode the master DMA controller does not generate address or control signals. The DREQ and DACK signals of the master are used to interface the HRQ and HLDA signals of the slave DMA devices. Once the master has received a HLDA from the CPU in response to a DREQ caused by the HRQ from a slave DMA controller, the master DMA controller will ignore all inputs except HLDA from the CPU and DREQ on the active channel. This prevents conflicts between the DMA devices.

Figure 4 shows the cascade interconnection for two levels of DMA devices. Note that Channel 0 of DMA2 is internally connected for Cascade mode to DMA1. Additional devices can be cascaded to the available channels in either DMA1 or DMA2 since cascade is not limited to two levels of DMA controllers.

When programming cascaded controllers, begin with the device which is actually generating HRQ to the system (first level device) and then proceed to the second level devices. RESET causes the DACK outputs to become active low and are placed in the inactive state. To allow the internal cascade between DMA1 and DMA2 to function correctly, the active low state of DACK should not be modified. This is because the 82C206 has an inverter between DACK0 of DMA2 and HLDA of DMA1. The first level device's DMA request mask bits will prevent second level cascaded devices from generating unwanted hold requests during the initialization process.

#### **DMA Transfers**

Four types of transfer modes are provided in the 82C206 DMA subsystem. These transfer types are:

Figure 4. Cascade Mode Interconnect

Read Transfer—Read transfers move data from memory to an I/O device, by generating the memory address and asserting DMAMEMR and XIOW during the same cycle.

Write Transfer—Write transfers move data from an I/O device to memory by generating the memory address and asserting XIOR and DMAMEMW.

Memory-to-Memory Transfer—The memory-to-memory transfer is used to move a block of memory from one location in memory to another. DMA channels 0 and 1 may be programmed to operate as memory-to-memory channels by setting a bit in the Command Register. Once programmed to perform a memory-to-memory transfer the process can be started by generating either a software or an external request to channel 0. Once the transfer is initiated, Channel 0 provides the address for the source block during the memory read portion of the cycle. Channel 1 generates the address for the memory write cycle. During the read cycle, a byte of data is

latched in the internal Temporary Register of the 82C206. The contents of this register are then output on the XD0-7 data lines during the write portion of the cycle and subsequently written to memory. Channel 0 may be programmed to maintain the same source address on every cycle. This allows the CPU to initialize large blocks of memory with the same value. The 82C206 will continue performing transfer cycles until Channel 1 reaches terminal count.

Verify Transfer—The verify transfer is a pseudotransfer which is useful for diagnostics. In this type of transfer the DMA will operate as if it is performing a Read or Write Transfer by generating HRQ, addresses and DACK but will do so without asserting a command signal. Since no transfer actually takes place IOCHRDY is ignored during Verify transfer cycles.

#### **Autoinitialization**

Each of the four DMA channel Mode Registers contains a bit which will cause the channel to reinitialize after reaching terminal count. During this process, referred to as Autoinitialization, the Base Address and Base Word Count Registers, which were originally written by the CPU, are reloaded into the Current Address and Current Word Count Registers (both the base and current registers are loaded during a CPU write cycle). The base registers remain unchanged during DMA Active cycles and can only be changed by the CPU. If the channel has been programmed to autoinitialize, the request mask bit will not be set upon reaching terminal count. This allows the DMA to continue operation without CPU intervention.

During memory-to-memory transfers the Word Count Registers of both Channel 0 and Channel 1 must be programmed with the same starting value for full autoinitialization. If Channel 0 reaches terminal count before Channel 1, then Channel 0 will reload the starting address and word count and continue transferring data from the beginning of the source block. Should Channel 1 reach terminal count first, it will reload the current registers and Channel 0 will remain uninitialized.

#### **DREQ Priority**

The 82C206 supports two schemes for establishing DREQ priority. The first is fixed priority which assigns priority based on channel position. In this method Channel 0 is assigned the highest priority. Priority assignment then progresses downward through the channels in order with Channel 3 receiving the lowest priority.

The second type of priority assignment is rotating priority. In this scheme the ordering of priority from Channel 0 to Channel 3 is maintained but the actual assignment of priority changes. The channel most recently serviced will be assigned the lowest priority and, since the order of priority assignment remains fixed, the remaining three channels rotate accordingly. The rotating priority assignment is illustrated in Figure 5.

In instances where multiple requests occur at the same time the 82C206 will issue a HRQ but will not freeze the priority logic until HLDA is returned. Once HDLA becomes active the priority logic is frozen and DACK is asserted on the highest requesting channel. Priority will not be re-evaluated until HLDA has been deactivated.

### **Address Generation**

Eight intermediate bits of the address are multiplexed onto the data lines during Active cycles of the DMA. This reduces the number of pins required by the DMA subsystem. During state S1, the intermediate addresses are output on data lines XD0-XD7. These addresses should be externally latched and used to drive the system address bus. Since DMA1 is used to transfer 8-bit data and DMA2 is used to transfer 16-bit data, a one bit skew occurs in the intermediate address fields. DMA1 will therefore output addresses A8-A15 on the data bus at this time whereas DMA2 will output A9-A16. A separate set of latch and enable signals are provided for both DMA1 and DMA2 to accommodate the address skew.

During 8-bit DMA cycles, in which DMA1 is active, the 82C206 will output the lower 8-bits

| First Arbitration          | Second<br>Arbitration      | Third<br>Arbitration       | Priority |

|----------------------------|----------------------------|----------------------------|----------|

| Channel 0                  | Channel 2 - Cycle<br>Grant | Channel 3 - Cycle<br>Grant | Highest  |

| Channel 1 - Cycle<br>Grant | Channel 3                  | Channel 0                  |          |

| Channel 2                  | Channel 0                  | Channel 1                  |          |

| Channel 3                  | Channel 1                  | Channel 2                  | Lowest   |

Figure 5. Rotating Priority Scheme

of address on XA0-XA7. The intermediate 8-bits of address will be output on XD0-XD7 and ADSTB8 will be asserted for one DMA clock cycle. The falling edge of ADSTB8 is used to latch the intermediate addresses A8-A15. An enable signal, AEN8, is used to control the output drivers of the external latch. A16-A23 are also generated at this time from a DMA Page Register in the 82C206. Note that A16 is output on the XA16 pin of the device.

16-bit DMA cycles from DMA2 require the 82C206 to output the lower 8-bits of the address on XA1-XA8. The intermediate addresses A9-A16 are output on XD0-XD7. Control for a separate latch is provided by signals ADSTB16 and AEN16. The DMA Page Register now generates A17-A23. During 16-bit DMA transfers XA0 and XA16 remain inactive.

The DMA Page Register is a set of 16 8-bit registers in the 82C206 which are used to generate the high order addresses during DMA cycles. Only 8 of the registers are actually used but all 16 were included to maintain IBM PC/AT compatibility. Each DMA channel has a register associated with it with the exception of Channel 0 of DMA2 which is used for internal cascading to DMA1. Assignment of each of these registers is shown in Figure 6 along with its Read/Write address.

| Address | Register Function            |

|---------|------------------------------|

| 080h    | Unused                       |

| 081h    | 8-bit DMA Channel 2 (DACK2)  |

| 082h    | 8-bit DMA Channel 3 (DACK3)  |

| 083h    | 8-bit DMA Channel 1 (DACK1)  |

| 084h    | Unused                       |

| 085h    | Unused                       |

| 086h    | Unused                       |

| 087h    | 8-bit DMA Channel 0 (DACK0)  |

| 088h    | Unused                       |

| 089h    | 16-bit DMA Channel 2 (DACK6) |

| 08Ah    | 16-bit DMA Channel 3 (DACK7) |

| 08Bh    | 16-bit DMA Channel 1 (DACK5) |

| 08Ch    | Unused                       |

| 08Dh    | Unused                       |

| 08Eh    | Unused                       |

| 08Fh    | Refresh Cycle                |

|         |                              |

Figure 6.

DMA Address Extension Register Map

During Demand and Block Transfers, the 82C206 generates multiple sequential transfers. For most of these transfers the informa-

tion in the external address latches will remain the same, eliminating the need to be relatched. Since the need to update the latches occurs only when a carry or borrow from the lower 8-bits of the Address Counter exists, the 82C206 will only update the latch contents when necessary. The 82C206 will therefore, only execute S1 cycles when necessary, resulting in an overall through-put improvement.

#### **Compressed Timing**

The DMA subsystem in the 82C206 can be programmed to transfer a word in as few as 3 DMA clock cycles. The normal DMA cycle consists of three states: S2, S3, and S4 (this assumes Demand or Block Transfer Mode). Normal transfers require 4 DMA clock cycles since S3 is executed twice due to the 1 wait state insertion. In systems capable of supporting higher through-put, the 82C206 can be programmed to omit one S3 and assert both commands in S2. S2 begins the cycle by generating the address and asserting both commands. One S3 cycle is executed and the cycle terminates in S4. If Compressed Timing is selected, T/C will be output in S2 and S1 cycles will be executed as necessary to update the address latch. Note that Compressed Timing is not allowed for memory-to-memory transfers.

# Register Description

# Current Address Register

Each DMA channel has a 16-bit Current Address Register which holds the address used during transfers. Each channel can be programmed to increment or decrement this register whenever a transfer is completed. This register can be read or written by the CPU in consecutive 8-bit bytes. If Autoinitialization is selected, this register will be reloaded from the Base Address Register upon reaching terminal count in the Current Word Count Register. Channel 0 can be prevented from incrementing or decrementing by setting the Address Hold Bit in the Command Register.

#### **Current Word Count Register**

Each channel has a Current Word Count

Register which determines the number of transfers to perform. The actual number of transfers performed will be one greater than the value programmed into the register. The register is decremented after each transfer until it goes from zero to FFFFh. When this roll-over occurs the 82C206 will generate T/C and either suspend operation on that channel and set the appropriate Request Mask Bit or Autoinitialize and continue.

# **Base Address Register**

Associated with each Current Address Register is a Base Address Register. This is a write only register which is loaded by the CPU when writing to the Current Address Register. The purpose of this register is to store the initial value of the Current Address Register for Autoinitialization. The contents of this register are loaded into the Current Address Register whenever terminal count is reached and the Autoinitialize Bit is set.

### **Base Word Count Register**

This register preserves the initial value of the Current Word Count Register. It is also a write only register which is loaded by writing to the Current Word Count Register. This register is loaded into the Current Word Count Register during Autoinitialization.

#### **Command Register**

This register controls the overall operation of a DMA subsystem. The register can be read or written by the CPU and is cleared by either RESET or a Master Clear command.

| msb |     |    |    |    |    |    | Isb |

|-----|-----|----|----|----|----|----|-----|

| b7  | b6  | b5 | b4 | b3 | b2 | b1 | b0  |

| DAK | DRQ | EW | RP | СТ | CD | АН | М-М |

**DAK**—DACK active level is determined by bit 7. Programming a 1 in this bit position makes DACK an active high signal.

**DRQ**—DREQ active level is determined by bit 6. Writing a 1 in this bit position causes DREQ to become active low.

**EW**—Extended Write is enabled by writing a 1 to bit 5, causing the write commands to be asserted one DMA cycle earlier during a transfer. The read and write commands both begin in state S2 when enabled.

RP—Writing a 1 to bit 4 causes the 82C206 to utilize a rotating priority scheme for honoring DMA requests. The default condition is fixed priority.

CT—Compressed timing is enabled by writing a 1 to bit 3 of this register. The default 0 condition causes the DMA to operate with normal timing.

**CD**—Bit 2 is the master disable for the DMA controller. Writing a 1 to this location disables the DMA subsystem (DMA1 or DMA2). This function is normally used whenever the CPU needs to reprogram one of the channels to prevent DMA cycles from occuring.

AH—Writing a 1 to bit 1 enables the address hold feature in Channel 0 when performing memory-to-memory transfers.

M-M—A 1 in the bit 0 position enables Channel 0 and Channel 1 to be used for memory-to-memory transfers.

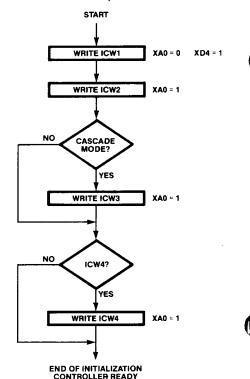

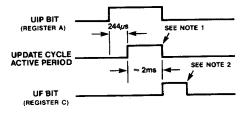

#### Mode Register