|

Author: Jonah McLeod

Source: Electronics, 20 Aug 1987 (pages 81-83 physical)

The AIC-6250 gives a 500% boost in host input-output performance, using

its 16-bit-wide data path to hit a 20-Mbyte-per-second transfer rate—the first

SCSI chip to do it.

Personal computers are rapidly closing the performance gap separating them

from more expensive low-end Motorola 68020-based work stations. The buses of

both IBM Corp.'s Personal System 2 and Apple Computer Inc.'s Macintosh II, for

example, can transfer data at more than 20 Mbytes per second. Yet both models

still come with disk controllers that can't transfer data across this

high-speed bus at more than 2 to 8 Mbytes/s. The reason for this lower transfer

speed—which is the main reason why PCs still don't measure up to work

stations in performance—is the lack of an inexpensive disk-controller chip

that could interact with the computer bus at the bus's maximum transfer

rate.

PC makers now have a solution to this problem. Adaptec Inc. is introducing a

Small Computer Systems Interface chip that the Sunnyvale, Calif., company says

is the first of its kind to achieve 20- Mbyte/s operation with the host

computer bus. Up to now, most existing SCSI controller chips could manage no

more than 4 Mbytes/s on the host computer bus, so the AIC-6250 SCSI Protocol

chip provides a 500% increase in host input-output performance. This will

enable a PC, with its bus and SCSI controller chip both operating at a

20-Mbyte/s transfer rate, to provide performance equal to that of a low-end

work station.

The AIC-6250 should help push SCSI toward high-end applications. Originally

designed as a low-cost interface between a computer and a peripheral, SCSI has

generally been used in PCs—the low-cost end of the computer spectrum. But as

designers figure out ways to get more and more speed out of the interface—the

AIC-6250 being a prime example—it increasingly will enable PCs to perform

more high-end applications (see p. 59) and will be used in more powerful

systems, such as work stations. The impact of the AIC-6250 will be heightened

by its price—$20 each in lots of 1,000, inexpensive enough to be used in

virtually any PC system design. Small quantities are available now, Adaptec

expects to ramp up in the last quarter of this year. When it does, the chip

should open up a far greater range of high-performance SCSI operations.

Previously, a system designer who wanted to get more performance out of SCSI

had to create his own printed-circuit board, adding anywhere from $200 to $500

to the system's cost.

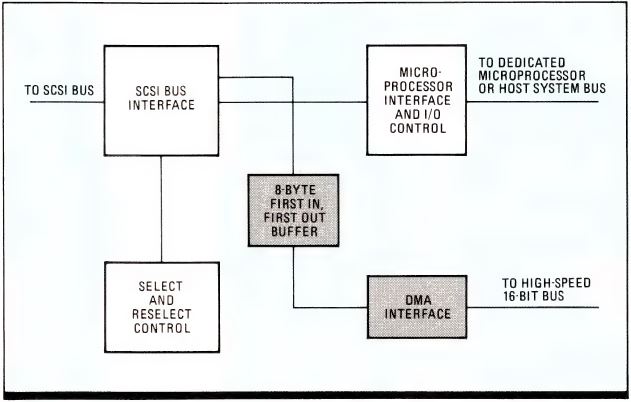

To achieve high performance, the AIC-6250 (see Figure 1) is the first

SCSI chip to offer a 16-bit-wide data path for connecting to host

computer-system buses. "Competitive chips have 8&-bit data paths," says

Jeffrey Miller, vice president of marketing at Adaptec. "Designing these

chips into an 80386- or 68020-based system with a 16- bit bus requires circuits

external to the chip to convert from an 8- to 16-bit data path."

Figure 1: ON THE BUS. The AIC-6250's bus interface handles

getting on and off the SCSI bus; a microprocessor interface and I/O-control

function routes command packets to and from the bus.

Also, the AIC-6250 is the first chip to offer three bus connections: the

16-bit data port, for connecting to the host computer system bus; an 8-bit data

port for connecting to the SCSI bus, and an 8-bit control port to allow the

host computer to communicate with the chip, even when a data transfer is

occurring on the other two buses. Other SCSI chips currently available provide

only an 8-bit data port to the host computer and an 8- bit port to the SCSI

bus. In addition, the AIC-6250 is the first SCSI controller that can operate

with a 20-MHz external clock; all other chips now handle only a 10-MHz external

clock.

The three I/O buses on the chip permit multi-tasking operation—they allow

more than one task to be processed at once. Two can transfer data between the

host computer and peripherals, while the third can provide concurrent

communications between the host CPU and the chip to configure yet another

transfer. "Up to now, because other chips have no separate data path to their

SCSI controller chip, if the CPU wants access to the SCSI chip, it has to halt

any ongoing data transfer," says G. Venkatesh, manager of Adaptec's IC

product line. "The sustained data rate on the CPU bus goes down. We get

around the problem by having the separate data path for the host CPU to access

the SCSI controller chip while a data transfer occurs on the other two

buses."

At any time, all three buses can be active, because each is being driven by

entirely different, autonomously operating elements in the system. To

accommodate all three buses, the chip performs the bus arbitration operations

for all three buses automatically, and in real time. To bring order to I/O

operations, a priority scheme was established by the SCSI specification. Up to

eight devices can be on the SCSI bus. Each is assigned a logical unit number,

with seven being the highest and zero the lowest. The host CPU usually has the

highest priority, so it can always access the SCSI bus. Next in priority is

typically the disk controller, with logical unit 6. Peripherals such as a tape

controller are usually given the lowest priority, logical unit 0.

Note: This is the ANSI / IBM standard, ID 7 SCSI

controller, ID6 Boot / IML drive, down to ID0. -LFO

The AIC-6250 achieves its fast system throughput by implementing all the

functions needed to provide an initiator or target by a host computer system

and any peripheral device on the SCSI bus. SCSI protocol requires that an

initiator select a device to perform some operation—read, write, seek, and so

on. The selected device becomes the target. Once the target has been selected,

it carries out the rest of the operations on the bus.

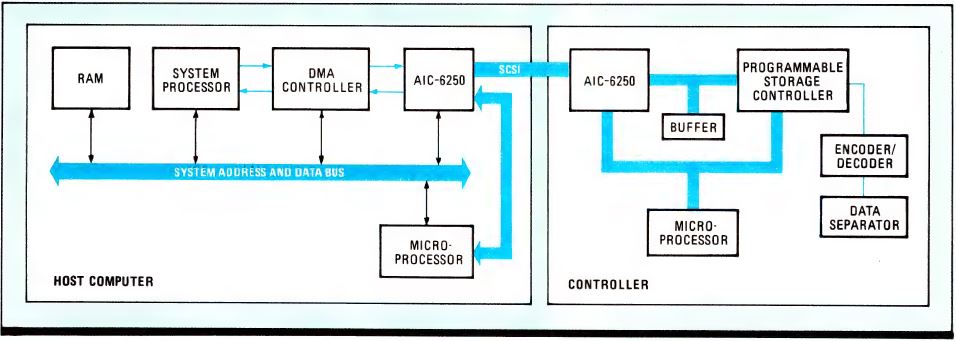

In a typical system configuration, one AIC-6250 interfaces between the host

computer and the SCSI bus and a second AIC-6250 connects the SCSI bus and a

peripheral device such as a Winchester, optical-disk, or tape drive (see

Figure 2). Depending on system configuration, the controllers can

operate in synchronous or asynchronous mode. In synchronous mode, the chips

transfer data on the SCSI bus at the maximum rate of 5 Mbytes/s. In

asynchronous mode, they transfer data at a maximum rate of 3 Mbytes/s.

"Mainframe I/O channels typically run at 3 Mbytes/s, and with bus contention it

is much lower than this," Miller says.

Figure 2: INTERFACING. Typically, one AIC-6250 interfaces

between the host and the SCSI bus and a second AIC-6250 connects the bus and

peripherals.

That speed makes the AIC-6250 faster than the transfer rates of most 5.25 -

and 3.5 in. disk drives used today in work stations and personal computers;

their top speed ranges from 930 Kbytes to 1.2 Mbytes/s. It does not, however,

mean the chip is far faster than it needs to be. For one thing, the coming

generation of drives will be considerably faster—the new 760-Mbyte EXT 8760

from Maxtor Corp., in San Jose, Calif., for example, has a 1.9-Mbyte/s transfer

rate. Some 8-in. Winchester drives already offer 2.5- and 3-Mbyte/s rates.

Also, newer drive designs incorporate a cache that can contain upwards of a

full track of data. "If the computer requests data from the disk that is

already in cache, the SCSI controller chip can access data from the cache and

transfer it at the full 3-Mbyte or 5-Mbyte/s transfer rate of the SCSI bus,"

says Venkatesh. "The AIC-6250 can serve this application today."

The reason for driving the SCSI bus at 5 Mbytes/s is the same as the reason

for driving the host CPU bus at 20 Mbytes/s. "In complex systems, there can

be multiple devices sitting on the system bus—a DMA controller, SCSI

controller, Ethernet, and so on," says Miller. "The faster a disk drive can

access the bus, make its transfer, and get off, the faster the overall system

through-put will be."

Because the AIC-6250 chip can handle a data transfer at up to 20 Mbytes/s,

it can also accept the relatively slow 90-Kbyte/s transfer rate of a tape drive

on the SCSI bus, store up to 8 bytes at a time, and then burst 8 bytes across

the system bus at 20 Mbytes/s. The 6250 transfers data at 20 Mbytes/s when the

system connects to a computer with a 16-bit data bus. A microprocessor

interface and I/O control function serve to route command packets to and from

the SCSI bus and to and from a microprocessor on the peripheral controller or

host computer.

Note: Not sure where this 20MB comes from. Sounds

like the 16-bit streaming transfer rate, NOT a sustained transfer. The Tribble

/ Early Spock / Newer Spock does 8.3MB bursts to the MCA bus. Perhaps IBM chose

to throttle the transfer to the MCA bus because the HD might not have an

AIC-6250 equivalent chip on the SCSI device? -LFO

Unlike other SCSI controller chips, most of which were designed for

controlling a peripheral device on the SCSI bus, the AIC-6250 was also designed

to control host computer access to the SCSI bus. When the AIC-6250 is connected

on the host side of the SCSI bus, it can receive SCSI command packets directly

from the host CPU, which is the case with most PC implementations. Or the

system can be designed with a separate microprocessor dedicated to handle the

I/O channel—typical of a work-station design.

Inside the chip, a direct-memory-access counter also allows the chip to

transfer up to 16 Mbytes of data without requiring the host CPU to become

involved. To move such a large amount of data, the host CPU issues the SCSI

commands to effect the transfer. The AIC-6250 on the host side sets up to

perform the transfer by sending a command to an AIC-6250 connected to, say, an

optical disk. The two then begin transferring bytes across the SCSI bus. A

counter inside the chip sending the data counts down with each byte

transferred. Its maximum count is 16 million. To support the two most popular

microprocessor buses, those of the 8086 and 68000 families, the chip has two

addressing schemes. With one pin on the 6250, the host system can identify

itself as a multiplexed or separated address and data bus, and the chip can

configure itself to operate accordingly.

Adaptec Broadens the Role of a SCSI Chip

Since its inception, the Small Computer Systems Interface has imposed a

speed limit on system buses of 5 Mbytes/s – he speed at which data can be

transferred on the SCSI bus. But the / Inc. team that designed the AIC-6250

SCSI Protocol Chip realized it could raise the speed limit by accelerating the

data as it came off the SCSI bus and hit the high-speed system bus. It did that

by developing a fast chip that works on both the system and the peripheral side

of the SCSI bus to move data quickly.

"We knew from the start that the chip had to operate equally well on both

sides of the SCSI bus and that it had to have separate interfaces for both the

SCSI and the host buses," says Jeffrey Miller, vice president of marketing at

Adaptec.

To achieve the necessary levels of performance in its chips, Adaptec

involved its system designers in the final design of the 6250 chip. "They

pointed out where the bottlenecks were in the design,' Miller says. Getting

designed into both the host computer side of the SCSI bus – especially by

leading computer manufacturers – would convince a lot of drive manufacturers

to design the chip into their embedded SCSI drives as well. "By dropping the

chip on both sides of the SCSI bus, a system designer gets the fastest possible

throughput: 20 Mbytes per second on the SCSI bus", says G. Venkatesh, IC

product line manager at Adaptec.

One of the problems remaining with SCSI – one that tends to encourage

system builders to use the same chip on both sides of the bus – is that the

interface specification is still subject to individual interpretation by chip

manufacturers. "But the system customers want a solution that optimizes

overall throughput. They don't want to deal with inconsistencies between

different chip manufacturers' SCSI implementations," Miller asserts.

|