**D** SQUARE D Instruction Bulletin

Bulletin No. 30298-004-01 April 1996 Raleigh, NC, USA

# SERIPLEX<sup>®</sup> SPX-EXM-INTF Interface Card

CONTENTS

| INTRODUCTION                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------|

| FEATURES                                                                                                               |

| SPECIFICATIONS                                                                                                         |

| THEORY OF OPERATION 4                                                                                                  |

| NEW FEATURES                                                                                                           |

| Simplified Multiplex Mapping for Multiplexed Input and Output Modules                                                  |

| Multiplex Channel Scan Size Selection                                                                                  |

| Multiplex Priority Channel                                                                                             |

| Software Control of the SERIPLEX Network Parameters                                                                    |

| Expanded Status Information                                                                                            |

| Hardware IRQ Selection                                                                                                 |

| Data Line Rest State                                                                                                   |

| INSTALLING THE EXM INTERFACE CARD                                                                                      |

| EXM Screen Setup                                                                                                       |

| DUAL-PORT RAM                                                                                                          |

| Non-multiplex Input Buffer (0x000-0x01F)                                                                               |

| Non-multiplex Output Buffer (0x020-0x03F)         9           Non-multiplex Passthru Buffer (0x040-0x05F)         10   |

| Safe State Buffer (0x060-0x07F)                                                                                        |

| Multiplex Input Mapping Buffer (0x080-0x09F)                                                                           |

| Multiplex Output Mapping Buffer (0x0A0-0x0BF)                                                                          |

| Multiplex Input Mapping Word (0x0C0-0x0C1)         14           Multiplex Output Mapping Word (0x0C2-0x0C3)         15 |

| Control Word (0x0F0-0x0F1)                                                                                             |

| Status Word (0x0F2-0x0F3) 17                                                                                           |

| Extended Control Word (0x0F4-0x0F5)                                                                                    |

| Extended Status Word (0x0F6-0x0F7)       19         SERIPLEX Parameters Word (0x0FC-0x0FD)       21                    |

| Firmware Revision ID (0x0FE-0x0FF)                                                                                     |

| Multiplex Input Buffer (0x100-0x2DF) 22                                                                                |

| Multiplex Output Buffer (0x300-0x04DF) 24                                                                              |

| Multiplex Passthru Buffer (0x500-0x6DF)         26           IRQ Select Word (0x7F4-0x7F5)         27                  |

| Interface Reset Command Word (0x7F6-0x7F7)                                                                             |

| Host Watch Event Word (0x7F8-0x7F9)                                                                                    |

| Interrupt Status Word (0x0FC-0x0FD)                                                                                    |

| Interrupt Control Word (0x7FE-0x7FF)                                                                                   |

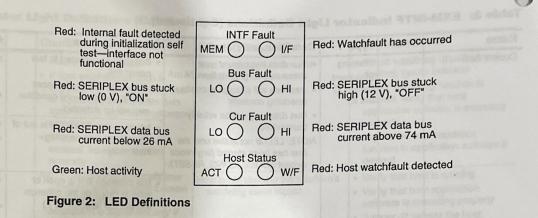

| APPENDIX A-INDICATOR LIGHT DEFINITIONS AND EXPLANATIONS                                                                |

| APPENDIX B—INITIALIZATION PROCEDURES                                                                                   |

| APPENDIX C—FAULT RESPONSES                                                                                             |

| APPENDIX D—POWER-UP AND RESET BEHAVIOR                                                                                 |

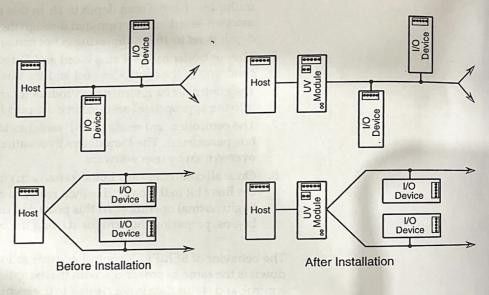

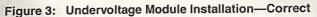

| APPENDIX E-UNDERVOLTAGE PROTECTION                                                                                     |

| © 1996 Square D. All Rights Reserved                                                                                   |

#### INSTALLING THE EXM INTERFACE CARD

**EXM Screen Setup**

SPX-EXM-INTE

XXX DOOO

1 - Enable

10000

- 1. Install the interface card in an open slot on the backplane of the computer.

- Connect the SERIPLEX adapter cable to the 9-pin connector on the card. The open end of the cable has 4 pre-tinned wires for connection to the SERIPLEX control bus network cable.

- 3. Access the main RadiSys EXM configuration setup menu by pressing the CNTL-ALT-ESC keys simultaneously.

- 4. Select the EXM configuration screen to configure EXM expansion modules in the system. To display this screen, press the F2 function key from the main setup screen.

Each EXM must be defined in this screen so the BIOS can identify and initialize each one at boot-up. Each EXM must be listed by slot number, ID, and two option bytes as defined below. The screen shown below shows configuration information in hexadecimal format. (F10 = save and return, ESC = return with no save)

| Slot | ID | 0B1 | 0B2 |

|------|----|-----|-----|

| 0    | FF | 00  | 00  |

| 1.1  | ED | 01  | 00  |

| 2    | 7D | 07  | 00  |

| 3    | FF | 00  | 00  |

| 4    | FF | 00  | 00  |

| 5    | FF | 00  | 00  |

| 6    | FF | 00  | 00  |

| 7    | FF | 00  | 00  |

Slot: Indicates the EXM slot in which the EXM is installed. ID: Hard-wired identification value. Each type of EXM has a unique ID value.

OB1/OB2: Two "option" bytes of configuration information.

NOTE: All 8 slots are listed on the setup screen even if they are not all used. All slots not occupied by an EXM module should show ID - FF (no EXM present).

#### Table 1: Configuration Screen Setup Values Definition

|       | 0B1 [1]               | (                     | 0B2                                 |

|-------|-----------------------|-----------------------|-------------------------------------|

| 6F    | Bits 7-4 reserved     |                       | Dual-Port Base Address              |

| Hex   | set to 0              | PRINEW FRIEN          | (A18 – A11) <sup>[2]</sup>          |

| GORAS | Bits 3-1              | Bit 0                 | 1310.1                              |

|       | 000 - No IRQ selected | 0 = card disabled     |                                     |

|       | 001 - IRQ3 0 3        | 1 = card enabled      | The section of the local sectors in |

|       | 010-IRQ4 05           | New sectore           |                                     |

| Curd  | 011 - IRQ5 🝖 ブ        | and the second second |                                     |

|       | 100 - IRQ7 89         |                       |                                     |

|       | 101 - IRQ11 🔊 🔁       |                       |                                     |

|       | 110-IRQ12 ØD          |                       |                                     |

|       | 111 - IRQ15 👩 🚝       |                       |                                     |

<sup>[2]</sup> A19 always assumed = 1.

After all EXM modules are configured, press F10 to save the data or ESC to ignore the changes. Both cases return to the main setup screen.

The EXM BIOS configuration setup must then be modified to enable and configure the EXM-INTF card. The EXM BIOS configuration setup is retained within a battery-backed RAM for each of the installed EXM modules.

© 1996 Square D All Rights Reserved

Problem with ID of SPX communication Card (6F-XX

@ 26/09/2022

#### **DUAL-PORT RAM**

The dual-port RAM is a 2K 8 block of memory that may be mapped into user memory on any 2K byte boundary between 0x80000 (8000:0000) and 0xFF800 (FF80:0000) (see Table 2). This is the upper half of "real" memory when using an Intel 80x86 based processor.

NOTE: When clearing memory on the dual-port RAM the user should **NOT** clear addresses 0xF0 - 0xFF. These addresses are the direct control and status locations used by the interface and are initialized by the interface itself.

The rest of this section describes the various buffer, control and status locations in the dual-port RAM. Addresses referred to are offsets from the base address of the 2K block.

| Offset(s)                 | Description and Page                                         |

|---------------------------|--------------------------------------------------------------|

| 0x000-0x01F               | "Non-multiplex Input Buffer (0x000-0x01F)" on page 8         |

| 0x020-0x03F               | "Non-multiplex Output Buffer (0x020-0x03F)" on page 9        |

| 0x040-0x05F               | "Non-multiplex Passthru Buffer" on page 10                   |

| 0x060-0x07F               | "Safe State Buffer (0x060-0x07F)" on page 11                 |

| 0x080-0x09F               | "Multiplex Input Mapping Buffer (0x080-0x09F)" on page 12    |

| 0x0A0-0x0BF               | "Multiplex Output Mapping Buffer (0x0A0-0x0BF)" on page 13   |

| 0x0C0-0x0C1               | "Multiplex Input Mapping Word (0x0C0-0x0C1)" on page 14 [1]  |

| 0x0C2-0x0C3               | "Multiplex Output Mapping Word (0x0C2-0x0C3)" on page 15 [1] |

| 0x0C4-0x0EF               | <reserved></reserved>                                        |

| 0x0F0-0x0F1               | "Control Word" on page 16                                    |

| 0x0F2-0x0F3               | "Status Word" on page 17                                     |

| 0x0F4-0x0F5               | "Extended Control Word (0x0F4-0x0F5)" on page 18             |

| 0x0F6-0x0F7               | "Extended Status Word (0x0F6-0x0F7)" on page 19              |

| 0x0F8-0x0FB               | <reserved></reserved>                                        |

| 0x0FC-0x0FD               | "SERIPLEX Parameters Word (0x0FC-0x0FD)" on page 21          |

| 0x0FE-0x0FF               | "Firmware Revision ID (0x0FE-0x0FF)" on page 21              |

| 0x100-0x2DF               | "Multiplex Input Buffer (0x100-0x2DF)" on page 22            |

| 0x2E0-0x2FF               | <reserved></reserved>                                        |

| 0x300-0x4DF               | "Multiplex Output Buffer (0x300-0x04DF)" on page 24          |

| 0x4E0-0x4FF               | <reserved></reserved>                                        |

| 0x500-0x6DF               | "Multiplex Passthru Buffer (0x500-0x6DF)" on page 26         |

| 0x6E0-0x7F3               | <reserved></reserved>                                        |

| 0x7F4-0x7F5               | "IRQ Select Word (0x7F4-0x7F5)" on page 27                   |

| 0x7F6-0x7F7               | "Interface Reset Command Word (0x7F6-0x7F7)" on page 28      |

| 0x7F8-0x7F9               | "Host Watch Event Word (0x7F8-0x7F9)" on page 28             |

| 0x7FA-0x7FB               | <reserved></reserved>                                        |

| 0x7FC-0x7FD               | "Interrupt Status Word (0x0FC-0x0FD)" on page 28             |

| 0x7FE-0x7FF               | "Interrupt Control Word (0x7FE-0x7FF)" on page 28            |

| <sup>[1]</sup> Preferred. |                                                              |

#### Table 2: Dual-Port RAM Map

Bulletin No. 30298-004-01 April 1996

Non-multiplex Input Buffer (0x000-0x01F) words 0x000-0x00F The non-multiplex input buffer occupies the first 32 bytes of dual-port RAM. Each of the 256 possible non-multiplex inputs is mapped as 1 bit in this table, packed 8 SERIPLEX addresses to each byte. If the bit associated with an input is "0" the input is OFF. If the bit associated with an input is "1" the input is ON.

NOTE: SERIPLEX address 0 is always reserved by the interface and is not available to the user.

The buffer is mapped as:

Offset 0x000 Bit 0 = SERIPLEX address 0 </reserved> Bit 1 = SERIPLEX address 1 Bit 2 = SERIPLEX address 2 Bit 3 = SERIPLEX address 3 Bit 4 = SERIPLEX address 4 Bit 5 = SERIPLEX address 5 Bit 6 = SERIPLEX address 6 Bit 7 = SERIPLEX address 7 Offset 0x001 Bit 0 = SERIPLEX address 8 Bit 1 = SERIPLEX address 9

Bit 2 = SERIPLEX address 10 Bit 3 = SERIPLEX address 11 Bit 4 = SERIPLEX address 12 Bit 5 = SERIPLEX address 13 Bit 6 = SERIPLEX address 14 Bit 7 = SERIPLEX address 15

#### Offset 0x01F

Bit 0 = SERIPLEX address 248 Bit 1 = SERIPLEX address 249 Bit 2 = SERIPLEX address 250 Bit 3 = SERIPLEX address 251 Bit 4 = SERIPLEX address 252 Bit 5 = SERIPLEX address 253 Bit 6 = SERIPLEX address 254 Bit 7 = SERIPLEX address 255

Following is example C code to test the state of a non-multiplex input at SERIPLEX address 11:

else

printf("Input 11 is OFF);

Non-multiplex Output Buffer (0x020-0x03F) words 0x010-0x01F The non-multiplex output buffer occupies bytes 0x20-0x3F of dual-port RAM. Each of the 256 possible non-multiplex outputs is mapped as 1 bit in this table, packed 8 SERIPLEX addresses to each byte. Setting the bit associated with an output to "0" turns that output OFF. The bit setting associated with turning on an output is 1.

NOTE: SERIPLEX address 0 is always reserved by the interface and is not available to the user.

The buffer is mapped as:

| Offset 0x020                      |     |                               |

|-----------------------------------|-----|-------------------------------|

| Bit 0 = SERIPLEX address          | 0   | <reserved< th=""></reserved<> |

| Bit 1 = SERIPLEX address          | 1   |                               |

| Bit 2 = SERIPLEX address          | 2   |                               |

| Bit 3 = SERIPLEX address          | 3   |                               |

| Bit 4 = SERIPLEX address          | 4   |                               |

| Bit 5 = SERIPLEX address          | 5   |                               |

| Bit 6 = SERIPLEX address          | 6   |                               |

| Bit 7 = SERIPLEX address          | 7   |                               |

| r sharping 28                     |     |                               |

| Offset 0x021                      |     |                               |

| Bit 0 = SERIPLEX address          | 8   |                               |

| Bit 1 = SERIPLEX address          | 9   |                               |

| Bit 2 = SERIPLEX address          | 10  |                               |

| Bit 3 = SERIPLEX address          | 11  |                               |

| Bit 4 = SERIPLEX address          | 12  |                               |

| Bit 5 = SERIPLEX address          | 13  |                               |

| Bit 6 = SERIPLEX address          | 14  |                               |

| Bit 7 = SERIPLEX address          | 15  |                               |

| Alter and the sub-                |     |                               |

| and a second second second second |     |                               |

| Offset 0x03F                      |     |                               |

|                                   | 248 |                               |

| Die o - Dinizi dani or            | 249 |                               |

| Die i - Diniti Din daar ood       | 249 |                               |

|                                   | 250 |                               |

| Bit 3 = SERIPLEX address 2        | 231 |                               |

Bit 3 = SERIPLEX address 251 Bit 4 = SERIPLEX address 252 Bit 5 = SERIPLEX address 253 Bit 6 = SERIPLEX address 254 Bit 7 = SERIPLEX address 255

Following is example C code to turn a non-multiplex output at SERIPLEX address 4 ON and address 17 OFF:

```

/* Interface base address is assumed to be D000:0000 */

int far *base;

FP_SEG = 0xD000;

FP_OFF = 0 \times 0000;

/* set interface to NORMAL operating mode */ ·

base[0xF0/2] &= 0xFFFC;

/* turn output at SERIPLEX address 4 ON*/

/- chan 4

*/

base[0x20/2] |= 0x0010;/* OR with 0000 0000 0001 0000

/* turn output at SERIPLEX address 17 OFF */

/*

/*

chan 17

*/

/* AND with 1111 1111 1111 1101 */

base[0x22/2] &= ~0x0002;

```

Non-multiplex Passthru Buffer (0x040-0x05F) words 0x020-0x02F The non-multiplex passthru buffer occupies bytes 0x40-0x5F of dual-port RAM. This buffer is only used when operating in SERIPLEX mode 2. This table "links" non-multiplex SERIPLEX inputs to non-multiplex SERIPLEX outputs in mode 2 without requiring intervention by the host computer. Each of the 256 possible nonmultiplex addresses is mapped as 1 bit in this table, packed 8 SERIPLEX addresses to each byte. Setting the bit associated with an address to "0" disconnects the input and output from each other. Setting the bit associated with an address to "1" links the input to the output.

NOTE: SERIPLEX address 0 is always reserved by the interface and is not available to the user.

The buffer is mapped as:

| Offset 0 | x040                          |         |                                         |          |

|----------|-------------------------------|---------|-----------------------------------------|----------|

| Bit 0    | = SERIPLEX                    | address | 0 <re< td=""><td>eserved&gt;</td></re<> | eserved> |

| Bit 1    | = SERIPLEX                    | address | 1                                       |          |

| Bit 2    | = SERIPLEX                    | address | 2                                       |          |

| Bit 3    | = SERIPLEX                    | address | 3                                       |          |

| Bit 4    | = SERIPLEX                    | address | 4                                       |          |

| Bit 5    | = SERIPLEX                    | address | 5                                       |          |

| Bit 6    | = SERIPLEX                    | address | 6                                       |          |

| Bit 7    | = SERIPLEX                    | address | 7                                       |          |

|          |                               |         |                                         |          |

| Offset ( | 0x041                         |         |                                         |          |

| Bit 0    | = SERIPLEX                    | address | 8                                       |          |

| Bit 1    | = SERIPLEX                    | address | 9                                       |          |

| Bit 2    | = SERIPLEX                    | address | 10                                      |          |

| Bit 3    | = SERIPLEX                    | address | 11                                      |          |

| Bit 4    | = SERIPLEX                    | address | 12                                      |          |

| Bit 5    | = SERIPLEX                    | address | 13                                      |          |

| Bit 6    | = SERIPLEX                    | address | 14                                      |          |

| Bit 7    | = SERIPLEX                    | address | 15                                      |          |

|          |                               |         |                                         |          |

|          | 1.2                           |         |                                         |          |

| Offset   | 0x05F                         |         |                                         |          |

| 011000   | A local and the second second | address | 248                                     |          |

| Bit C    |                               |         | 240                                     |          |

| Bit 1    |                               |         | 249                                     |          |

|          | 2 = SERIPLEX                  |         | 250                                     |          |

| Bit 3    | 3 = SERIPLEX                  | address |                                         |          |

|          |                               |         |                                         |          |

Bit 4 = SERIPLEX address 252 Bit 5 = SERIPLEX address 253 Bit 6 = SERIPLEX address 254 Bit 7 = SERIPLEX address 255

ex output at SE AT HEA address

Following is example C code to enable non-multiplex passthru on SERIPLEX addresses 20 and 31:

/\* Interface base address is assumed to be D000:0000 \*/

int far \*base;

FP\_SEG = 0xD000;

FP\_OFF = 0x0000;

/\* set interface to NORMAL operating mode \*/

base[0xF0/2] &= 0xFFFC;

| /* Enable pass-thru at SER | RIPLEX ad | dresses 20 and 3 | 1            |

|----------------------------|-----------|------------------|--------------|

|                            | /*        | /- chan 31       |              |

|                            | /*        |                  | /- chan 20   |

|                            | /*        | Ļ                | $\downarrow$ |

| base[0x42/2]  = 0x8010;    | /* 0      | R with 1000 0000 | 0001 0000    |

Bulletin No. 30298-004-01 April 1996

Safe State Buffer (0x060-0x07F) words 0x030-0x03F The safe state buffer occupies bytes 0x60-0x7F of dual-port RAM. This buffer provides the user with a convenient way to preset the state of the outputs to be used in case of a problem in the system. It is mapped in the same way as the non-multiplex output table and is selected by issuing a SAFE command (setting bits 1 and 0 of offset 0xF0 to 1 and 0, respectively).

Each of the 256 possible non-multiplex addresses is mapped as 1 bit in this table, packed 8 SERIPLEX addresses to each byte. Setting the bit associated with an address to "0" or to "1" will turn that output off or on, respectively.

#### NOTES:

- SERIPLEX address 0 is always reserved by the interface and is not available to the user.

- d (0x0CO-0x0C1)\* on mer 14

- In a mode 1 system an OFF in the safe state buffer will NOT override an ON at a field input. In mode 1 the interface can NOT force an output OFF, only ON.

The buffer is mapped as:

| Offset 0x060                                                                                                     |    |                       |

|------------------------------------------------------------------------------------------------------------------|----|-----------------------|

| Bit 0 = SERIPLEX address                                                                                         | 0  | <reserved></reserved> |

| Bit 1 = SERIPLEX address                                                                                         | 1  |                       |

| Bit 2 = SERIPLEX address                                                                                         | 2  |                       |

| Bit 3 = SERIPLEX address                                                                                         | 3  |                       |

| Bit 4 = SERIPLEX address                                                                                         | 4  |                       |

| Bit 5 = SERIPLEX address                                                                                         |    |                       |

| Bit 6 = SERIPLEX address                                                                                         |    |                       |

| Bit 7 = SERIPLEX address                                                                                         | 7  |                       |

|                                                                                                                  |    |                       |

| Offset 0x061                                                                                                     |    |                       |

| Bit 0 = SERIPLEX address                                                                                         |    |                       |

| Bit 1 = SERIPLEX address                                                                                         |    |                       |

| Bit 2 = SERIPLEX address                                                                                         | 10 |                       |

| Bit 3 = SERIPLEX address                                                                                         | 11 |                       |

| Bit 4 = SERIPLEX address                                                                                         | 12 |                       |

| Bit 5 = SERIPLEX address                                                                                         | 13 | raciani 30 c          |

| Bit 6 = SERIPLEX address                                                                                         | 14 |                       |

| Bit 7 = SERIPLEX address                                                                                         | 15 |                       |

| and the second |    |                       |

| an tracase is and the                                                                                            |    |                       |

|   |       |     |     | •        |         |     |  |

|---|-------|-----|-----|----------|---------|-----|--|

| ) | ffset | = ( | )x( | )7F      |         |     |  |

|   | Bit   | 0   | =   | SERIPLEX | address | 248 |  |

|   | Bit   | 1   | =   | SERIPLEX | address | 249 |  |

|   | Bit   | 2   | =   | SERIPLEX | address | 250 |  |

|   | Bit   | 3   | =   | SERIPLEX | address | 251 |  |

|   | Bit   | 4   | =   | SERIPLEX | address | 252 |  |

|   | Bit   | 5   | =   | SERIPLEX | address | 253 |  |

|   | Bit   | 6   | =   | SERIPLEX | address | 254 |  |

|   | Bit   | 7   | =   | SERIPLEX | address | 255 |  |

|   |       |     |     |          |         |     |  |

Following is example C code to demonstrate the safe state buffer:

```

/* Interface base address is assumed to be D000:0000 */

int far *base;

FP SEG = 0 \times D000;

FP_OFF = 0 \times 0000;

/* set interface to NORMAL operating mode */

base[0xF0/2] &= 0xFFFC;

/* set output at SERIPLEX address 20 ON in safe mode and leave */

*/

NOTE: it is assumed that

/* leave all other outputs OFF.

*/

/* dual-port RAM has already been cleared.

1*

*/

chan 20 -\

*/

1*

*/

/* OR with 0000 0000 0001 0000

base[0x62/2] |= 0x0010;

if(error)

( /* select SAFE mode */

base[0xF0/2] = (base[0xF0]&0xFFFC) | 0x0002);

```

}

#### **Multiplex Input Mapping Buffer** (0x080-0x09F) words 0x040-0x04F

The multiplex input mapping buffer occupies bytes 0x80-0x9F of dual-port RAM. The multiplex input mapping build occup which address blocks are to be used for This buffer is used to inform the interface which address block is to be multiple This buffer is used to inform the internace include address block is to be multiplexed for multiplex inputs. To designate that a particular address block is to be multiplexed, multiplex inputs. To designate that a planding word in the buffer. Multiplex write a value of 0xFFFF to the corresponding word in the buffer. Multiplex write a value of 0xFFFF to the contespond of the boundaries (16, 32, 48, ... 240).

#### NOTES:

- ES: SERIPLEX addresses 0 to 4 are reserved by the interface when operating in multiplexed SERIPLEX addresses 0 to 4 are reserved by the interface when operating in multiplexed SERIPLEX addresses 0 to 4 are reserved by 0 to 15 unavailable for multiplexed modules. .

- mode. In is makes the block of maintain backward compatibility with existing software. It is This buffer is provided to maintain backward mount the maintained in future more This buffer is provided to mathemate and may not be maintained in future versions of not recommended for new software and may not be maintained in future versions of not recommended for new software and mapping Word (0x0C0-0x0C1)" on page 14 for interface firmware. See "Multiplex Input Mapping Word (0x0C0-0x0C1)" on page 14 for the preferred method.

### The buffer is mapped as:

|         |             | <reserv< th=""><th>rody</th><th>1</th></reserv<>                                                                 | rody | 1   |

|---------|-------------|------------------------------------------------------------------------------------------------------------------|------|-----|

| Offsets | 0x080-0x081 |                                                                                                                  |      |     |

| Offsets | 0x082-0x083 | Module                                                                                                           |      | 16  |

| Offsets | 0x084-0x085 | Module                                                                                                           | at   | 32  |

|         | 0x086-0x087 | Module                                                                                                           | at   | 48  |

| Offsets |             | Module                                                                                                           |      | 64  |

| Offsets | 0x088-0x089 | and the second |      | 80  |

| Offsets | 0x08A-0x08B | Module                                                                                                           |      |     |

| Offsets | 0x08C-0x08C | Module                                                                                                           | at   | 96  |

| Offsets | 0x08E-0x08F | Module                                                                                                           | at   | 112 |

| Offsets | 0x090-0x091 | Module                                                                                                           | at   | 128 |

| Offsets | 0x092-0x093 | Module                                                                                                           | at   | 144 |

| Offsets | 0x094-0x095 | Module                                                                                                           | at   | 160 |

| Offsets | 0x096-0x097 | Module                                                                                                           | at   | 176 |

| Offsets | 0x098-0x099 | Module                                                                                                           | at   | 192 |

|         |             | Module                                                                                                           |      | 208 |

| Offsets | 0x09A-0x09B |                                                                                                                  |      |     |

| Offsets | 0x09C-0x09D | Module                                                                                                           | at   | 224 |

| Offsets | 0x09E-0x09F | Module                                                                                                           | at   | 240 |

|         |             |                                                                                                                  |      |     |

Following is example C code to "map" a multiplex input module at base addresses 16 and 128:

/\* Interface base address is assumed to be D000:0000 \*/ int far \*base;  $FP\_SEG = 0 \times D000;$  $FP_OFF = 0x0000;$

/\* mark buffer for multiplex input module at address 16 \*/ base[0x82/2] = 0xFFFF;

/\* mark buffer for multiplex input module at address 128 \*/ base[0x90/2] = 0xFFFF;

/\* verify that the interface is NOT busy and wait if it is \*/ if(base[0xF2/2] & 0x0010) wait\_not\_busy(); /\* wait for interface NOT busy \*/

/\* issue MAP command and set interface to NORMAL operating mode \*/ base[0xF0/2] = (base[0xF0/2] & 0xFFFC) | 0x0080;

#### Multiplex Output Mapping Buffer (0x0A0-0x0BF) words 0x050-0x05F

The multiplex output mapping buffer occupies bytes 0xA0-0xBF of dual-port RAM. This buffer is used to inform the interface which address blocks are to be used for multiplex outputs. To designate that a particular address block is to be multiplexed, write a value of 0xFFFF to the corresponding word in the buffer. Multiplex modules are expected to reside on 16-bit address boundaries (16, 32, 48, ... 240).

#### NOTES:

- SERIPLEX addresses 0 to 4 are reserved by the interface when operating in multiplexed mode. This makes the block of addresses from 0 to 15 unavailable for multiplexed modules.

- This buffer is provided to maintain backward compatibility with existing software. It is

not recommended for new software and may not be maintained in future versions of

interface firmware. See "Multiplex Output Mapping Word (0x0C2-0x0C3)" on page 15

for the preferred method.

#### The buffer is mapped as:

|         | 0 000 0.001 | <reser< th=""><th>trad</th><th>2010</th><th></th></reser<> | trad | 2010 |  |

|---------|-------------|------------------------------------------------------------|------|------|--|

| Offsets | 0x0A0-0x0A1 |                                                            |      |      |  |

| Offsets | 0x0A2-0x0A3 | Module                                                     | at   | 16   |  |

| Offsets | 0x0A4-0x0A5 | Module                                                     | at   | 32   |  |

| Offsets | 0x0A6-0x0A7 | Module                                                     |      | 48   |  |

| Offsets | 0x0A8-0x0A9 | Module                                                     | at   | 64   |  |

| Offsets | 0x0AA-0x0AB | Module                                                     | at   | 80   |  |

| Offsets | 0x0AC-0x0AC | Module                                                     | at   | 96   |  |

| Offsets | 0x0AE-0x0AF | Module                                                     | at   | 112  |  |

| Offsets | 0x0B0-0x0B1 | Module                                                     | at   | 128  |  |

| Offsets | 0x0B2-0x0B3 | Module                                                     | at   | 144  |  |

| Offsets | 0x0B4-0x0B5 | Module                                                     | at   | 160  |  |

| Offsets | 0x0B6-0x0B7 | Module                                                     | at   | 176  |  |

| Offsets | 0x0B8-0x0B9 | Module                                                     | at   | 192  |  |

| Offsets | 0x0BA-0x0BB | Module                                                     | at   | 208  |  |

| Offsets | 0x0BC-0x0BD | Module                                                     | at   | 224  |  |

| Offsets | 0x0BE-0x0BF | Module                                                     | at   | 240  |  |

|         |             |                                                            |      |      |  |

Following is example C code to "map" multiplex output modules at base addresses 16 and 32:

/\* Interface base address is assumed to be D000:0000 \*/

int far \*base;

FP\_SEG = 0xD000;

FP\_OFF = 0x0000;

/\* mark buffer for multiplex output module at address 16 \*/

base[0xA2/2] = 0xFFFF;

/\* mark buffer for multiplex output module at address 32 \*/

base[0xA4/2] = 0xFFFF;

wait\_not\_busy(); /\* wait for interface NOT busy \*/

/\* issue MAP command and set interface to NORMAL operating mode \*/

base[0xF0/2] = (base[0xF0/2] & 0xFFFC) | 0x0080;

#### Multiplex Input Mapping Word (0x0C0-0x0C1) word 0x060

The multiplex input mapping word occupies bytes 0xC0-0xC1 of dual-port RAM. This word is used to inform the interface which address blocks are to be used for multiplex inputs. To designate that a particular address block is to be multiplexed, set the corresponding bit to 1. Multiplex modules are expected to reside on 16-bit address boundaries (16, 32, 48, ... 240). In this word the 16-bit module boundaries are bit-mapped so that each bit of the word represents one 16-bit block of addresses.

NOTE: SERIPLEX addresses 0 to 4 are reserved by the interface when operating in multiplexed mode. This makes the block of addresses from 0 to 15 unavailable for multiplexed modules.

The word is mapped as:

| 0x0C0 | -                                                                                                        | Bit                                                                                                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                               | <reserved></reserved>                                                                                                                                                                                                     |

|-------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0C0 | -                                                                                                        | Bit                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                               | Module at 16                                                                                                                                                                                                              |

| 0x0C0 | -                                                                                                        | Bit                                                                                                                                                                                                                                                                                                                                                                           | 2                                                                                                                                                                                               | Module at 32                                                                                                                                                                                                              |

| 0x0C0 | -                                                                                                        | Bit                                                                                                                                                                                                                                                                                                                                                                           | 3                                                                                                                                                                                               | Module at 48                                                                                                                                                                                                              |

| 0x0C0 | -                                                                                                        | Bit                                                                                                                                                                                                                                                                                                                                                                           | 4                                                                                                                                                                                               | Module at 64                                                                                                                                                                                                              |

| 0x0C0 | -                                                                                                        | Bit                                                                                                                                                                                                                                                                                                                                                                           | 5                                                                                                                                                                                               | Module at 80                                                                                                                                                                                                              |

| 0x0C0 | -                                                                                                        | Bit                                                                                                                                                                                                                                                                                                                                                                           | 6                                                                                                                                                                                               | Module at 96                                                                                                                                                                                                              |

| 0x0C0 | -                                                                                                        | Bit                                                                                                                                                                                                                                                                                                                                                                           | 7                                                                                                                                                                                               | Module at 112                                                                                                                                                                                                             |

| 0x0C1 | -                                                                                                        | Bit                                                                                                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                               | Module at 128                                                                                                                                                                                                             |

| 0x0C1 | -                                                                                                        | Bit                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                               | Module at 144                                                                                                                                                                                                             |

| 0x0C1 | -                                                                                                        | Bit                                                                                                                                                                                                                                                                                                                                                                           | 2                                                                                                                                                                                               | Module at 160                                                                                                                                                                                                             |

| 0x0C1 | -                                                                                                        | Bit                                                                                                                                                                                                                                                                                                                                                                           | 3                                                                                                                                                                                               | Module at 176                                                                                                                                                                                                             |

| 0x0C1 | -                                                                                                        | Bit                                                                                                                                                                                                                                                                                                                                                                           | 4                                                                                                                                                                                               | Module at 192                                                                                                                                                                                                             |

| 0x0C1 | -                                                                                                        | Bit                                                                                                                                                                                                                                                                                                                                                                           | 5                                                                                                                                                                                               | Module at 208                                                                                                                                                                                                             |

| 0x0C1 | -                                                                                                        | Bit                                                                                                                                                                                                                                                                                                                                                                           | 6                                                                                                                                                                                               | Module at 224                                                                                                                                                                                                             |

| 0x0C1 | -                                                                                                        | Bit                                                                                                                                                                                                                                                                                                                                                                           | 7                                                                                                                                                                                               | Module at 240                                                                                                                                                                                                             |

|       | 0x0C0<br>0x0C0<br>0x0C0<br>0x0C0<br>0x0C0<br>0x0C0<br>0x0C1<br>0x0C1<br>0x0C1<br>0x0C1<br>0x0C1<br>0x0C1 | 0x0C0       -         0x0C1       - | 0x0C0 - Bit<br>0x0C0 - Bit<br>0x0C0 - Bit<br>0x0C0 - Bit<br>0x0C0 - Bit<br>0x0C0 - Bit<br>0x0C0 - Bit<br>0x0C1 - Bit<br>0x0C1 - Bit<br>0x0C1 - Bit<br>0x0C1 - Bit<br>0x0C1 - Bit<br>0x0C1 - Bit | 0x0C0 - Bit 2<br>0x0C0 - Bit 3<br>0x0C0 - Bit 4<br>0x0C0 - Bit 5<br>0x0C0 - Bit 5<br>0x0C0 - Bit 7<br>0x0C1 - Bit 0<br>0x0C1 - Bit 1<br>0x0C1 - Bit 2<br>0x0C1 - Bit 3<br>0x0C1 - Bit 4<br>0x0C1 - Bit 5<br>0x0C1 - Bit 6 |

Following is example C code to "map" a multiplex input module at base addresses 16 and 128:

```

/* Interface base address is assumed to be D000:0000 */

int far *base;

FP\_SEG = 0 \times D000;

FP_OFF = 0x0000;

/* mark buffer for multiplex input modules at address 16 and 128

1*

/- module at 128-143

/*

/- module at 16-31 ↓

/*

base[0xC0/2] = 0x0102; /* 0000 0001 0000 0010

/* verify that the interface is NOT busy and wait if it is */

if(base[0xF2/2] & 0x0010)

wait_not_busy(); /* wait for interface NOT busy */

/* issue MAP+ENHANCED_MAP_ENA command */

/* and set interface to NORMAL operating mode */

base[0xF0/2] = (base[0xF0/2] & 0xFFFC) | 0x00C0;

```

Multiplex Output Mapping Word (0x0C2-0x0C3) word 0x061 The multiplex output mapping word occupies bytes 0xC2-0xC3 of dual-port RAM. This buffer is used to inform the interface which address blocks are to be used for multiplex outputs. To designate that a particular address block is to be multiplexed, set the corresponding bit to 1. Multiplex modules are expected to reside on 16-bit address boundaries (16, 32, 48, ... 240).

NOTE: SERIPLEX addresses 0 to 4 are reserved by the interface when operating in multiplexed mode. This makes the block of addresses from 0 to 15 unavailable for multiplexed modules.

#### The word is mapped as:

| Offset | 0x0C2 | - | Bit | 0 | <reserved></reserved> |

|--------|-------|---|-----|---|-----------------------|

| Offset | 0x0C2 | - | Bit | 1 | Module at 16          |

| Offset | 0x0C2 | - | Bit | 2 | Module at 32          |

| Offset | 0x0C2 | - | Bit | 3 | Module at 48          |

| Offset | 0x0C2 | 1 | Bit | 4 | Module at 64          |

| Offset | 0x0C2 | - | Bit | 5 | Module at 80          |

| Offset | 0x0C2 | - | Bit | 6 | Module at 96          |

| Offset | 0x0C2 | - | Bit | 7 | Module at 112         |

| Offset | 0x0C3 | - | Bit | 0 | Module at 128         |

| Offset | 0x0C3 | - | Bit | 1 | Module at 144         |

| Offset | 0x0C3 | - | Bit | 2 | Module at 160         |

| Offset | 0x0C3 | - | Bit | 3 | Module at 176         |

| Offset | 0x0C3 | - | Bit | 4 | Module at 192         |

| Offset | 0x0C3 | - | Bit | 5 | Module at 208         |

| Offset | 0x0C3 | - | Bit | 6 | Module at 224         |

| Offset | 0x0C3 | - | Bit | 7 | Module at 240         |

|        |       |   |     |   |                       |

Following is example C code to "map" multiplex output modules at base addresses 16 and 32:

/\* Interface base address is assumed to be D000:0000 \*/

int far \*base;

FP\_SEG = 0xD000;

FP\_OFF = 0x0000;

/\* verify that the interface is NOT busy and wait if it is \*/

wait not\_busy(); /\* wait for interface NOT busy \*/

/\* and set interface to NORMAL operating mode \*/

base[0xF0/2] = (base[0xF0/2] & 0xFFFC) | 0x00C0;

/\* issue MAP+ENHANCED\_MAP\_ENA command \*/

\*/

base[0xC2/2] = 0x0006; /\* 0000 0000 0000 0110

ormanic to gerennice where to look h pomation. If d'is bit is "0" the old style bit mapping buffer and multiplex buch

© 1996 Square D All Rights Reserved

if(base[0xF2/2] & 0x0010)

#### SPX-EXM-INTF Interface Card Dual-Port RAM

#### Control Word (0x0F0-0x0F1) word 0x078

The main control word for the interface is located at bytes 0x0F0-0x0F1.

NOTE: If this word is written as 2 bytes instead of being written as a 16-bit word, the offset 0x0F0 MUST ALWAYS BE WRITTEN LAST.

Commands are located in bits 2 to 7 of offset 0x0F0 and require the user to monitor the BUSY status (bit 4 of offset 0x0F2). The interface should be NOT BUSY (that is, 0) before any command is issued. After issuing a command, the user should watch for BUSY (1) and then a return to NOT BUSY before writing to the interface buffers of control bytes.

These 2 bytes are defined as:

| Offset 0xF1 - Bit 7        | <reserved> (always 0)</reserved>                                                                                                                                                                      |  |  |  |  |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Offset 0xF1 - Bit 6        | Multiplex Channel Size Map Enable:<br>Must be set to 1 to allow processing of multiplex channel size select bits<br>(offset 0xF1 - bits 5 and 4) when map command (offset 0xF0 - bit 7) is<br>issued. |  |  |  |  |  |

| Offset 0xF1 - Bits 5 and 4 | Multiplex Channel Size Select Bits                                                                                                                                                                    |  |  |  |  |  |

| Offset 0xF1 - Bits 3-0     | <reserved> (always 0)</reserved>                                                                                                                                                                      |  |  |  |  |  |

| Bit 5 | Bit 4 | <b>Multiplex Channel Selection</b>   |

|-------|-------|--------------------------------------|

| 0     | 0     | Scan 2 multiplex channels            |

| 0     | 1     | Scan 4 multiplex channels            |

| 1     | 0     | Scan 8 multiplex channels            |

| 1     | 1     | Scan 16 multiplex channels (default) |

| Offset 0xF0 - Bit 7        | Map Command<br>This command has several actions:                                                                                                                                                                                                                                                                                                                                            |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | 1. Process multiplex input and output mapping information                                                                                                                                                                                                                                                                                                                                   |

| The Dil dis Studion of S   | 2. Process the number of multiplex channels to scan if multiplex channel size map enable is set to "1"                                                                                                                                                                                                                                                                                      |

|                            | 3. Process priority channel enable and priority channel selection.                                                                                                                                                                                                                                                                                                                          |

| Offset 0xF0 - Bit 6        | Enhanced Map Enable<br>This bit works with the map command to determine where to look for<br>multiplex input and output information. If this bit is "0" the old style<br>mapping buffers (multiplex input mapping buffer and multiplex output<br>mapping buffer) are used; otherwise, the newer mapping words (multiplex<br>input mapping word and multiplex output mapping word) are used. |

| Offset 0xF0 - Bit 5        | Map SERIPLEX Parameters<br>Maps the SERIPLEX clock rate and frame size parameters according to<br>the host parameters word (offset 0xFC). If the map mode enable bit is "1"<br>then the SERIPLEX mode (offset 0xFC - bit 7) is also set.                                                                                                                                                    |

|                            | (The SERIPLEX mode affects only the operation of the interface.<br>Individual modules must be programmed to change from mode 1 to<br>mode 2 SERIPLEX operation on a system level.)                                                                                                                                                                                                          |

| Offset 0xF0 - Bit 4        | Map Mode Enable<br>Enables SERIPLEX mode to be set according to the SERIPLEX mode bit<br>(offset 0xFC - bit 7) when the map SERIPLEX parameters command is<br>issued.                                                                                                                                                                                                                       |

| Offset 0xF0 - Bit 3        | Host Watchdog Control<br>This command bit serves two functions: (1) to control the processing of<br>the host watchdog parameters (offset 0xF4), and (2) to help recover from<br>a host watchdog fault. See "Host Watchdog Option" on page 18 for further<br>explanation.                                                                                                                    |

| Offset 0xF0 - Bit 2        | <reserved></reserved>                                                                                                                                                                                                                                                                                                                                                                       |

| Offset 0xF0 - Bits 1 and 0 | Interface Mode Select                                                                                                                                                                                                                                                                                                                                                                       |

© 1996 Square D All Rights Reserved -

#### Bulletin No. 30298-004-01 April 1996

#### SPX-EXM-INTF Interface Card Dual-Port RAM

| Bit 1 | Bit 0 | Interface Mode Select      |

|-------|-------|----------------------------|

| 0     | 0     | NORMAL                     |

| 0     | 1     | MONITOR                    |

| 1     | 0     | SAFE STATE                 |

| 1     | 1     | FORCE_LONG_RESET (default) |

#### Interface Modes

NORMAL: This is the "normal" operating mode for the interface. It allows full access to all interface functions in both non-multiplexed and multiplexed configurations with full read/write capability.

MONITOR: This mode "monitors" the status of the SERIPLEX bus inputs. No outputs are driven onto the bus; this also prevents the scanning of multiplexed inputs.

SAFE STATE: This mode causes the interface to transmit the contents of the safe state buffer instead of the multiplexed or non-multiplexed output tables. Multiplex channel scanning continues (if multiplex modules are mapped into the system) causing ALL multiplexed channels of a module base address to be set to the same value. The purpose of this buffer is to allow the user to predefine a "safe state" for the output in case of an emergency, so that selecting this interface mode is all that is necessary to transmit that condition rather than having to manipulate all of the outputs after the emergency condition has been detected.

FORCE\_LONG\_RESET: This mode shuts down the SERIPLEX clock, causing all modules to enter into a LONG\_RESET detect mode after approximately 40 ms. Once detected, all output modules except SPX-08D20mA, SPX-AOUT81-5 and SPX-AOUT81-10 enter their programmed shelf state until the SERIPLEX clock is restored.

#### NOTES:

- When the SERIPLEX bus clock signal is inactive, the EXM interface card holds the bus data line high (Version 1.5 and later).

- The SPX-08D20mA, SPX-AOUT81-5 and SPX-AOUT81-10 hold the last output value until the clock is restored.

The status word for the interface is located at bytes 0x0F2-0x0F3.

These 2 bytes are defined as:

| Offset | 0xF3 - | Bit | 7-Bit | 0 | <reserved> (alway</reserved> | s 0)  |  |

|--------|--------|-----|-------|---|------------------------------|-------|--|

| Offset | 0xF2 - | Bit | 7-Bit | 6 | <reserved> (alway</reserved> | \$ 0) |  |

| Offset | 0xF2   | Bit | 5     |   | LONG_RESET_DETECT            |       |  |

| Offset | 0xF2 - | Bit | 4     |   | BUSY FLAG                    |       |  |

| Offset | 0xF2 - | Bit | 3-Bit | 0 | <reserved> (alway</reserved> | s 0)  |  |

|        |        |     |       |   |                              |       |  |

LONG\_RESET\_DETECT indicates that the clock has been idle for at least 40 ms.

"Busy flag" indicates that the interface is BUSY initializing or processing a command. It should be noted that there may be a delay of several milliseconds before the busy flag is set depending upon the command issued. (The interface reset command takes the longest time before setting the busy flag.) As a result of this time delay it is recommended that the user watch for the busy flag to go active upon the issuing of a command before watching for the busy flag to be clear.

NOTE: This bit should always be reset (0) before modifying any of the control or data buffers.

17

**Extended Control Word** (0x0F4-0x0F5) word 0x07A

**Priority Channel Parameters** (offset 0xF5)

Host Watchdog Option

The extended control word for the interface is located at bytes 0x0F4-0x0F5. This word is treated as 2 separate bytes containing 2 sets of parameters. The host word is freated as 2 separate by the overall multiplex priority channel parameters watchdog parameters are at offset 0xF4 and multiplex priority channel parameters are at offset 0xF5.

The multiplex priority channel parameters allow the user to enable or disable the multiplex priority channel feature on the interface and to select the desired priority channel when enabled. The multiplex priority channel feature allows one multiplex channel to be scanned more often than the others. Once the channel has been selected and enabled it is scanned every other frame. Normal multiplex channel scanning for the other channels being scanned will take twice as long to scan. For example, if the multiplex channel scan size is set to 4 and multiplex channel 1 is chosen as the priority channel, then multiplex channels are scanned in the following sequence: 0, 1, 1, 1, 2, 1, 3, 1 (that is, the priority channel is scanned every other frame. In other words: 0, p, 1, p, 2, p, 3, p, 0, p, 1, p, 2, p, 3, p, ...).

| Offset | 0xF5 | - Bit | 7 | - | Bit | 5 | <reserved< th=""><th>l&gt;</th><th></th></reserved<> | l>      |        |

|--------|------|-------|---|---|-----|---|------------------------------------------------------|---------|--------|

| Offset | 0xF5 | - Bit | 4 |   |     |   | PRIORITY                                             | CHANNEL | Enable |

| Offset | 0xF5 | - Bit | 3 | - | Bit | 0 | PRIORITY                                             | CHANNEL | Select |

Priority Channel Enable: This bit determines whether or not the priority channel will be enabled or disabled when the next map command (Offset 0xF0 - Bit 7) is issued.

Priority Channel Select: These bits select the priority channel (that is, the multiplexed channel to be scanned at a higher rate). The range is from 0 to 15 (0000=0, 0001=1, ...1111=15).

The host watchdog option (when enabled) requires the host computer to write a specific pattern to a specific location at a periodic rate to inform the interface that the host is still functioning properly.

The time constant for time-out is selectable with the software with a range of 120 to 500 ms.

The action taken by the interface when a host watchdog fault is detected is userselectable. The available options are:

- Force a long reset condition on the SERIPLEX bus by stopping the SERIPLEX clock if offset 0xF4 bit 0 is set to 0

- Transmit an internal copy of the safe state buffer if offset 0xF4 bit 0 is set to 1

The internal copy of the safe buffer is made when the host watchdog option is enabled and processed.

There are two methods of recovery from a host watchdog fault condition. In one method, a software sequence of setting the fault acknowledge bit and then setting the host watchdog control bit allows the user to restart the interface with a minimum of re-initialization. The other method requires a reset to the interface either by issuing an interface reset command or via system reset from the host.

Bulletin No. 30298-004-01 April 1996

Host Watchdog Parameters (offset 0xF4)

| Offset | OVEA | - Bit | 7 | Host | Watchdog | Enable |  |

|--------|------|-------|---|------|----------|--------|--|

| OLISEL | UXP4 | - BIL | / | HOSL | watchdod | Enable |  |

| Bit 7 | Host Watchdog Enable                                                                                       |

|-------|------------------------------------------------------------------------------------------------------------|

| 0     | Disables host watchdog when a host watchdog control command<br>is issued to the control word (0x0F0-0x0F1) |

| 1     | Enables host watchdog when a host watchdog control command is issued to the control word (0x0F0-0x0F1)     |

Offset 0xF4 - Bit 6 <reserved> Offset 0xF4 - Bits 5 & 4 Watchdog Time Constant Selects

| Bit 5 | Bit 4 | Watchdog Time Constant         |

|-------|-------|--------------------------------|

| 0     | 0     | Approximately 120 ms           |

| 0     | 1     | Approximately 240 ms           |

| 1     | 0     | Approximately 380 ms           |

| 1     | 1     | Approximately 500 ms (default) |

Offset 0xF4 - Bit 2 Host Watchdog Fault Acknowledge

If software recovery is allowed, this bit is set to "1" and a host watchdog control command is issued to the control word (0x0F0-0x0F1) in order to acknowledge the fault and resume normal interface operation.

| Offset 0xF4 - Bit 1 | Host Watchdog Fault |

|---------------------|---------------------|

|                     | Recovery Method     |

| Bit 1 | Host Watchdog Fault Recovery Method                          |

|-------|--------------------------------------------------------------|

| 0     | Software recovery allowed                                    |

| 1 100 | Requires interface reset command or system reset on the host |

#### Offset 0xF4 - Bit 0 Host Watchdog Fault Action

| Bit 0 | Host Watchdog Fault Action                         |

|-------|----------------------------------------------------|

| 0     | Force LONG_RESET (stops the SERIPLEX clock)        |

| 1     | transmit an internal copy of the safe state buffer |

### The extended status word for the interface is located at bytes 0x0F6-0x0F7.

These 2 bytes are defined as:

Offset 0xF7 - Bits 7 & 6 <reserved> Offset 0xF7 - Bits 5 & 4 Multiplex Channel Size Selection Bits

| Bit 5 | Bit 4 | Multiplex Channel Size Selection     |

|-------|-------|--------------------------------------|

| 0     | 0     | Scan 2 multiplex channels            |

| 0     | 1     | Scan 4 multiplex channels            |

| 1     | 0     | Scan 8 multiplex channels            |

| 1     | 1     | Scan 16 multiplex channels (default) |

Offset 0xF7 - Bits 3-1 <reserved> Offset 0xF7 - Bit 0 Multiplex Mode Flag

| Bit 0 | Multiplex Mode Flag         |

|-------|-----------------------------|

| 0     | No multiplex modules mapped |

| 1     | Multiplex modules mapped    |

Extended Status Word (0x0F6-0x0F7) word 0x07B

#### SPX-EXM-INTF Interface Card **Dual-Port RAM**

Host Watchdog Fault Flag

| offs  | et 0xF6 - Bit /          |

|-------|--------------------------|

| Bit 7 | Host Watchdog Fault Flag |

| 0     | No fault has occurred    |

| 1     | Fault has occurred       |

7

Input Delay Fault Offset 0xF6 - Bit 6

| Bit 6 | Input Delay Fault     |

|-------|-----------------------|

| 0     | No fault has occurred |

| 1     | Fault has occurred    |

SERIPLEX Data Bus - High Current Fault

(1 0 mA)

| Offs | et 0xF6 - Bit 5       | Useb Current Fault (>≈74 mA)          |

|------|-----------------------|---------------------------------------|

|      |                       | - High Current Fault (≫74 mA)         |

| 0    | No fault has occurred |                                       |

| 1    | Fault has occurred    |                                       |

| Offs | et 0xF6 - Bit 4       | SERIPLEX Data Bus - Low Current Fault |

| Bit 4 | SERIPLEX Data Bus - Low Current Fault (<=20 IIIA) |

|-------|---------------------------------------------------|

| 0     | No fault has occurred                             |

| 1     | Fault has occurred                                |

Interface Watchdog Fault Offset 0xF6 - Bit 3

| Bit 3 | Interface Watchdog Fault |

|-------|--------------------------|

| 0     | No fault has occurred    |

| 1     | Fault has occurred       |

SERIPLEX Data Bus - Control Fault Offset 0xF6 - Bit 2 (Stuck High - at SERIPLEX Bus Power)

| Bit 2 | 2 SERIPLEX Data Bus - Control Fault (Stuck High -<br>SERIPLEX Bus Power) |         |  |  |

|-------|--------------------------------------------------------------------------|---------|--|--|

| 0     | No fault has occurred                                                    | Sugar . |  |  |

| 1     | Fault has occurred                                                       |         |  |  |

SERIPLEX Data Bus - Control Fault Offset 0xF6 - Bit 1 (Stuck Low - at SERIPLEX Bus Common)

Bit 2 SERIPLEX Data Bus - Control Fault (Stuck Low - at SERIPLEX Bus Common) 0 No fault has occurred. 1 Fault has occurred. .

Offset 0xF6 - Bit 0 Long Reset Detect Flag

| Bit 1 | Long Reset Detect Flag                                 |

|-------|--------------------------------------------------------|

| 0     | SERIPLEX clock has been detected within the last 40 ms |

| 1     | No SERIPLEX clock has been running for at least 40 ms  |

SPX-EXM-INTF Interface Card Dual-Port RAM

Bulletin No. 30298-004-01 April 1996

SERIPLEX Parameters Word (0x0FC-0x0FD) word 0x07E The SERIPLEX parameters word is located at bytes 0x0FC-0x0FD. This word is used to control the operating characteristics of the SERIPLEX Bus (that is, SERIPLEX mode, clock rate and frame size).

<reserved>

SERIPLEX MODE

11 mo orno

These bytes are defined as:

|       | et 0xFD - Bits 7 -<br>et 0xFC - Bit 7 |

|-------|---------------------------------------|

| Bit 7 | SERIPLEX MODE                         |

| 0     | SERIPLEX mode 1                       |

| 1     | SERIPLEX mode 2                       |

|       |                                       |

Offset 0xFC - Bits 6 - 4 SERIPLEX Clock Rate

0

| SERIPLEX<br>Clock Rate |  |  |  |

|------------------------|--|--|--|

| 100 kHz                |  |  |  |

| 75 kHz                 |  |  |  |

| 64 kHz                 |  |  |  |

| 50 kHz                 |  |  |  |

| 32 kHz                 |  |  |  |

| 25 kHz                 |  |  |  |

| 20 kHz                 |  |  |  |

| 16 kHz                 |  |  |  |

|                        |  |  |  |

Offset 0xFC - Bits 3 - 0 SERIPLEX Frame Size

|     | 0x11E-0x11F                                                                       |

|-----|-----------------------------------------------------------------------------------|

|     | 0x120-0x121                                                                       |

|     | 6x122-0x123                                                                       |

| 60  | 0x124-0x125                                                                       |

| 240 | 0x128-0x127                                                                       |