THE INSIDERS' GUIDE TO MICROPROCESSOR HARDWARE

# Alpha Sails, PowerPC Flails

x86 Poses Significant Threat to RISC Workstation Sales

by Linley Gwennap

Last issue, we reviewed the x86 market. Our New Year's coverage continues with articles about general-purpose RISC processors, media processors (see page 10), and embedded processors (see page 16).

During the past year, market prospects for PowerPC melted faster than ice cream on an Exponential chip, despite a renewed effort by the processor vendors to deliver competitive price/performance. Apple's problems proved too severe to fix quickly, and the company lost a third of its market share. After finally loosening its hold on Mac OS, Apple failed to find any other significant system maker to boost the Mac platform. The year ended with a whimper when IBM and Motorola admitted that not even their own internal systems groups are interested in Windows NT on PowerPC.

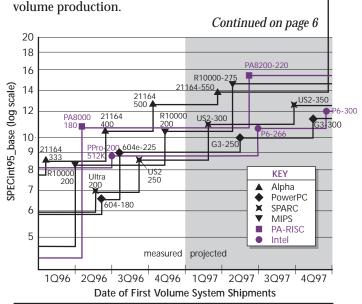

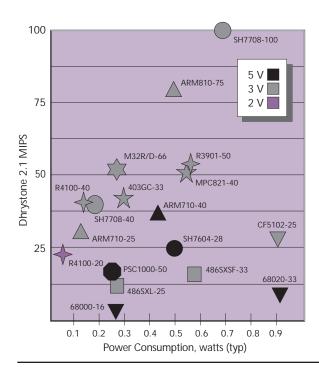

This announcement, combined with strong execution by Digital, puts Alpha in a surprisingly good position. After brief incursions by Intel and HP, Digital regained the microprocessor performance lead last fall, as Figure 1 shows. With the announcement of the 21264, due around the end of this year, Digital set a high hurdle for any vendor wishing to challenge that lead. Perhaps more important, Alpha is now the only RISC architecture supporting Windows NT and thus is the only alternative to x86 in this growing market. The company is pinning its NT hopes on the 21164PC, a new low-cost device due in 2Q97, along with x86 compatibility provided by its FX!32 emulator/translator.

In the meantime, uncharacteristically weak execution let Intel's boot heel slip ever so slightly off the throat of its RISC competition. After dramatically gaining the integer performance lead in late 1995 with its 200-MHz Pentium Pro, the company has yet to announce a faster processor, watching idly as most of the RISC vendors passed Intel's best performance. Worse yet, faster parts such as Klamath, Deschutes, and Merced have reportedly slipped 3–6 months. We still believe that market forces leave Intel well positioned in the workstation and server markets that have been the core

of RISC's success, but Intel's slippage gives the RISC vendors a bit more breathing room.

Once again, we offer our RISCie awards to acknowledge the best and worst RISC events of 1996. This year, we decided to let Intel join in the fun as an honorary RISC vendor. For the purposes of these awards, however, we have left out other x86 processor vendors as well as RISC processors aimed at the embedded market.

#### Digital Bets on NT

Another year, another title. Digital grabs its fourth award for **World's Fastest Microprocessor (shipping)**, this time for the 500-MHz 21164, rated at 12.6 SPECint95 (base). Yields on this chip seem to be good, so we expect Digital to squeeze out a speed boost, perhaps to 550 MHz, in the next few months. The company has demonstrated 600- MHz parts, but this frequency may not be attainable in

Figure 1. Digital will see increased competition for the integer performance lead in 1997, but the 21264 will be its trump card. (Source: SPEC for 1996 data, MDR for 1997)

Inside: Media Processors > Embedded CPUs > USB Micros > Tillamook

#### GLANCE

| Alpha Sails, PowerPC Flails               |     |

|-------------------------------------------|-----|

| Editorial: What's NeXT for Apple?         | . 3 |

| Most Significant Bits                     | . 4 |

| First Media Processors Reach the Market   |     |

| Embedded Vendors Seek Differentiation     |     |

| Controllers Proliferate as USB Catches On |     |

| Literature Watch                          | 24  |

| Recent IC Announcements                   | 25  |

| Patent Watch                              | 26  |

| Chart Watch                               | 27  |

| Resources                                 | 28  |

Founder and Editorial Director Michael Slater mslater@mdr.zd.com

#### Publisher and Editor in Chief

Linley Gwennap linley@mdr.zd.com

#### **Senior Editor**

Jim Turley jturley@mdr.zd.com

Senior Analyst Peter N. Glaskowsky png@mdr.zd.com

Associate Editor: Kathy Acuff

#### **Editorial Board**

Dennis Allison Rich Belgard Brian Case Jeff Deutsch Dave Epstein Don Gaubatz John Novitsky **Bernard Peuto** Nick Tredennick John F. Wakerly

#### **Editorial Office**

298 S. Sunnyvale Avenue Sunnyvale, CA 94086-6245 Phone: 408.328.3900 Fax: 408.737.2242

Microprocessor Report (ISSN 0899-9341) is published every three weeks, 17 issues per year. Rates are: U.S. and Canada: \$595 per year, \$1,095 for two years. Europe: £450 per year, £795 for two years. Elsewhere: \$695 per year, \$1,295 for two years. Additional copies in the same envelope: \$195 per year in the U.S. and Canada, \$250 elsewhere. Back issues are available.

## Published by

**MICRODESIGN**

President: Peter Christy pchristy@mdr.zd.com

#### **Business Office**

874 Gravenstein Hwy. So., Suite 14 Sebastopol, CA 95472 Phone: 707.824.4004 Fax: 707.823.0504 **Subscriptions:** 707.824.4001

cs@mdr.zd.com

World Wide Web: www.chipanalyst.com

Copyright ©1997, MicroDesign Resources. All rights reserved. No part of this newsletter may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without prior written permission.

Winner, Computer Press Award, 1993, 1994

Printed on recycled paper with soy ink.

# What's NeXT for Apple?

## New OS Strategy Leaves More Questions Than Answers

With the disclosure of Apple's new operating-system strategy (see page 5), the company has finally begun filling the strategic vacuum created when Copland was abandoned last year. Apple's plan deserves credit for being bold and innovative, but it also means Mac applications

will never have the full benefit of a protected, multitasking operating system unless they are rewritten (though Apple is working on tools to ease this transition). The new OS, codenamed Rhapsody, is not an enhanced Macintosh but rather a new platform that offers Macintosh compatibility.

The success of the OS plan is also a critical issue for PowerPC: with Windows NT on PowerPC all but abandoned, the volume desktop future for PowerPC lies entirely with Apple's software. Unfortunately, the new OS strategy is unlikely to lead to significant market share growth for Apple. Furthermore, applications written for Rhapsody will be easily ported to other operating systems and processor architectures, reducing the proprietary lock PowerPC has had on Macintosh applications.

What does this mean for Mac users? For the next year and a half—or longer, if, as seems likely, the software schedule slips—Mac OS will continue to lack key modern OS features. Starting in mid-1998, Mac users will have the choice of staying with the old OS or moving to Rhapsody.

Rhapsody is sure to have far greater memory requirements than Mac OS; NextStep currently requires 32M, and it would not be surprising if Rhapsody requires significantly more to run well. This means the vast majority of the installed base of Macintosh systems will require memory upgrades to handle the new OS. Education and home users, long the core of Apple's market, may find the increased memory requirements to be onerous, if not prohibitive. Rhapsody will also require new drivers for peripherals, such as scanners and backup devices. Users with devices from companies that have disappeared, or that have dropped Mac support, may find they can't use these devices under the new operating system.

Most Mac OS applications will run within the so-called compatibility box, but all the limitations of the old OS remain. For example, any application can crash the entire compatibility box. The only improvement from the current situation is that just the compatibility box, rather than the entire system, would need to be restarted. Apple claims applications will run at least as fast in the compatibility box as under the native Mac OS, due to the faster underlying I/O structure and kernel.

To get the benefits of Rhapsody, applications must be written to the OpenStep APIs. OpenStep offers a very nice development environment, including a powerful set of Web development tools, but it is far outside the mainstream and has had little success outside of large corporate in-house developers. Apple hopes its evangelism and higher volumes will make OpenStep a far bigger success, but this remains to be seen. Apple is fragmenting its already modest market share into two APIs; developers targeting Rhapsody will have, at least initially, only a fraction of the already small Macintosh market share available to them.

The user scenario for switching to Rhapsody will be similar, in many ways, to the switch to Power Macs. At first, users will run most applications in the compatibility box and gain little benefit from the new platform. In time, more software (especially high-end applications, such as publishing and multimedia development tools) will become available in native Rhapsody versions. The big question is how long this transition will take—and indeed, whether the majority of applications will ever be ported to Rhapsody.

Apple has committed to supporting Next's existing products, which provide the OpenStep APIs on top of Windows NT and various flavors of Unix. If Apple continues to support OpenStep as a cross-platform API, it could increase developer appeal by enabling developers to support Windows NT and Rhapsody with the same effort. However, this would leave Rhapsody's applications undifferentiated. Apple could add features to Rhapsody without offering them in the NT version of OpenStep, which would provide differentiation for Apple but weaken the developer proposition.

Mac developers and users facing the tumultuous, multiyear transition to Rhapsody are likely to look more intensely than ever at shifting their efforts to Windows. Even if many applications move to the OpenStep APIs, users probably will have the option of running most of those applications under NT. Users of OpenStep applications will have a choice between an x86 system running NT, with the additional bonus of Windows applications, or a PowerPC system running Rhapsody, with the additional bonus of Mac applications.

Apple is, in essence, allowing Mac OS to slowly fade away while building its future on the Next platform. Although this strategy may enable Apple to build a sustainable niche, it pushes today's Macintosh even further into the fringe.  $\square$

Milas Slato

#### MOST SIGNIFICANT BITS

#### ■ Tillamook to Extend P55C

Sources have confirmed that Intel is developing a 0.25-micron version of its P55C processor, as we have speculated (see MPR 10/28/96, p. 20). The new device, said to be codenamed Tillamook after a small town in Oregon, is expected to be a simple optical shrink of the current P55C processor. The P55C is built in Intel's 0.28-micron process, known as P854. We expect Tillamook to appear sometime in 2H97 at 200 MHz and possibly 233 MHz.

The key advantage of the shrink is a significant reduction in power. The 0.25-micron process, known as P856, is designed to run at 1.8 V (see MPR 9/16/96, p. 11), while the current P55C operates at 2.45 V in notebooks. This voltage change alone will decrease power dissipation by almost 50%. At 200 MHz, the P55C dissipates too much power to fit into a standard notebook design, preventing Intel from offering this part for mobile systems. Tillamook will easily fit into standard notebooks at 200 MHz.

In fact, even a 233-MHz Tillamook would have a maximum power dissipation of about 6 W, no sweat for notebook designers. Since the P55C hits 200 MHz in the current process, the smaller transistors should allow operation at 233 MHz. While a 233-MHz Tillamook would be a boon to notebook users, Intel may wish to push desktop users to the Klamath socket, locking out its x86 competitors. Intel may release the 233-MHz Tillamook only in a mobile module to keep it from appearing on the desktop.

Another advantage is a significantly decreased die size: Tillamook should be about 85 mm², just over half the size of the 140-mm² P55C. (Despite the 0.28-micron transistors, the P55C uses the equivalent of 0.35-micron metal layers, so the move to 0.25-micron produces a substantial die shrink.) This shrink will reduce manufacturing costs and increase per-wafer output.

Intel engineers will be challenged to provide 3.3-V I/O with the 1.8-V process, originally intended for 2.5-V I/O. Assuming Intel overcomes this challenge and that Tillamook maintains the P55C pinout, the only change required to the motherboard will be for the lower supply voltage.

Pressure from AMD and Cyrix may have helped Intel decide to greenlight the new chip. Tillamook gives Intel a response to the K6 and M2, which both offer increased performance in the P55C socket. The new part also provides some relief to thermally stressed notebook designers while filling a gap between the P55C and the forthcoming Mobile Deschutes, a P6 processor due in 1H98.

If Intel chooses to release a 233-MHz Tillamook for the desktop, it will provide one last performance kicker to the Pentium line before forcing vendors to move to P6 mother-boards. As the first Intel processor to go through four full process generations, the Pentium core is proving to have quite a long lifetime. —*L.G.*

#### Intel Launches MMX, P55C

Capping a nine-month product roll-out, Intel has officially launched the Pentium Processor with MMX Technology, previously known as the P55C (see MPR 10/28/96 p. 20 and 12/30/96, p. 1). Intel has been shipping the chip in volume for some time, so both mobile and desktop systems using it are available immediately from a wide range of vendors.

The P55C delivers a modest performance benefit for applications that don't use MMX because of its larger onchip cache. The 200-MHz chip delivers 6.4 SPECint95 (base) and 3.9 SPECfp95 (base)—an impressive boost of 26% over the non-MMX version (see page 27 for full SPEC details). On BAPCo's SYSmark32 tests, the 200-MHz P55C shows gains of 12% under Windows 95 and 19% under NT 4.0. These gains are lower than for SPEC because of the greater number of memory and I/O accesses in the application-oriented SYSmark32.

Intel's Media Benchmark—one of few benchmarks that illustrate MMX performance—shows a boost of about 60%. This is not a particularly meaningful number, however, as it is a combination of four widely varying results. On 3D geometry, which does not use MMX, the P55C delivers a trivial 4% increase, mainly due to the larger cache. On image processing, the improvement is a whopping 370%; audio shows a 113% gain, while video is boosted by 78%.

After January 27, pricing (in 1,000s) for the desktop version, which is in a plastic PGA and runs at 2.8 V, is \$356 for the 166-MHz part and \$539 for the 200-MHz version. The mobile versions are in PGA or TAB packages and operate at 2.45 V; pricing in either package is \$539 at 150 MHz and \$336 at 166 MHz.

The desktop prices are about \$50 higher than those of the non-MMX versions at the same clock speed, while the 150-MHz mobile version carries a larger \$122 premium. When one compares performance, on the other hand, the P55C-166 fares well against a Pentium-200 but costs \$142 less. If buyers are savvy, this difference will cause the old 200-MHz part to phase out rather quickly.

The initial MMX software offerings are nearly all consumer focused. At the launch event, Intel showed about a dozen applications, including games, photo capture and editing programs, home 3D modeling software, and a software MIDI synthesizer. (See *mmx.com/mmx/software* for a list of applications.) Intel expects about 100 applications supporting MMX to ship by the end of the year.

The early applications are predominantly from smaller companies. To motivate these vendors to support MMX before there is any installed base, Intel has provided cash as prepaid royalties for system-bundling deals. In essence, Intel has guaranteed the software vendors a certain level of success in selling their applications to system makers for bundling, and it has provided the cash up front to help fund

Thanks to its lower supply voltage, the P55C is able to deliver more performance within a thermal envelope similar to the P54C's. The 166-MHz mobile version is rated at 9.5 W maximum, slightly less than the mobile P54C-150. . For the desktop versions, the power dissipation is also similar to that of the P54C: the 200-MHz P55C dissipates a maximum of 15.7 W. (See <code>developer.intel.com/design/mmx/index.htm</code> for more information.)

With most information on the P55C previously disclosed, the official launch provided few surprises. We expect the initial midrange pricing for the part to drop substantially by midyear, making the P55C the best-selling PC processor during 2H97. This growth will quickly establish MMX as a requirement in the PC market. —*M.S.*

#### Apple Offers New OS Strategy

Apple has, at long last, laid out its new operating-system strategy and taken the first step toward implementing that strategy by acquiring Next Software. Apple's plan leads to a modern, object-oriented operating system replete with all the right buzzwords. Unfortunately, the benefits of the new OS will accrue only to applications written for a new application programming interface (API) based on Next's Open-Step API. Macintosh applications will be supported only within a compatibility box that carries with it all of the disadvantages of the current Mac OS.

The new operating system, code-named Rhapsody, will include Next's OpenStep software, extended with a few key Mac APIs, such as QuickTime and OpenDoc, and a version of Mac OS for compatibility with existing applications. An early developer release is promised for the middle of this year, with a limited end-user release by the end of the year. A version with Mac application compatibility and an enhanced Mac-style user interface is promised for mid-1998. This version is expected to be the first of interest to Mac users; the late-'97 version will be used mainly by developers and current users of Next's software.

Next's original product was a full operating system, called NextStep, based on the Mach kernel (used in a version of Unix developed at Carnegie-Mellon). More recently, Next shifted its efforts to OpenStep, a "middleware" product that implements Next's development environment and APIs on top of existing operating systems (including Windows NT and various versions of Unix). Although it has been assumed in many press reports that Rhapsody will use the Mach kernel, Apple says this decision has not been made; the Copland kernel and other options are also being considered.

With the now-abandoned Copland operating system, Apple had hoped to provide a high degree of compatibility with existing Mac applications while replacing the kernel to provide memory protection and pre-emptive multitasking. Because Mac Toolbox routines are not re-entrant, Copland required a nearly complete rewrite of the operating system.

Unfortunately, most Mac applications use undocumented features in the system software, such as directly accessing internal data structures. This misuse has made maintaining compatibility extremely difficult.

The new strategy forces existing Mac OS applications to run within a "compatibility box," which is just a copy of Mac OS running as a task under the new operating system. This version of Mac OS will be modified to work through the new kernel instead of communicating directly with the hardware. Apple says application compatibility will be better than it would have been with Copland, and at least 85% of existing applications should run. A key difference from the Copland strategy, however, is that standard Macintosh applications cannot take advantage of the new pre-emptive multitasking and interapplication memory protection.

Apple promises that twice-yearly releases of the existing Mac OS will continue through at least the end of the decade. The Harmony release (Mac OS 7.6), just now shipping, has modest stability and performance enhancements. Due in mid-'97 is the Tempo release, which will include a new multithreaded Finder—finally written in native PowerPC code—that will bring to System 7 some of the user-interface enhancements originally created for the ill-fated Copland. For most Mac users, Tempo and its follow-ons—rather than Rhapsody—will be the most significant developments for at least the next two years. —M.S.

#### ■ AMD Pushes K5 to PR166 Performance

By increasing the K5's core clock speed to 116.5 MHz (see MPR 12/9/96, p. 4), AMD has announced a new version with performance similar to that of a Pentium-166, according to AMD. The new K5-PR166 is slated for availability by the end of this quarter. AMD is currently shipping K5 processors with performance ratings of up to PR133, using internal clock speeds of up to 100 MHz. The PR166 carries a list price (in 1,000-unit quantities) of \$167.

Reaching the PR166 level puts AMD well into the sweet spot of the PC market. Pentium-166 systems were the most popular high-end PC during the recent Christmas season; with the introduction of the P55C, the Pentium-166 will be Intel's midrange processor throughout 1H97. The PR166 lists for 43% less than the Pentium-166, and AMD is likely to offer deeper discounts than Intel.

On the other hand, a large gap in Intel's pricing structure puts the PR166 at about the same price as a 150-MHz Pentium and \$33 more than a Pentium-133. OEMs will gain little extra performance by substituting a PR166 for an Intel processor of the same price.

For the first time, AMD has introduced a version of the K5 that matches the performance of an Intel chip priced at more than \$200. This success will boost AMD's average selling price and aid in the company's recovery from a financially disastrous 1996. The K5, however, is still far from matching the performance of Intel's fastest parts, a task that falls to the forthcoming K6. -L.G.

#### **RISC Processors**

Continued from page 1

Any such speed boost will have to last until the end of the year, when the 21264 is set to debut. Digital claims the forthcoming device will achieve a stunning 30 SPECint95 and 60 SPECfp95 (base), making it the World's Fastest **Microprocessor (announced)**. These figures represent more than twice the performance of the fastest chips today and, if achieved, should keep Digital in the performance lead.

To date, however, this lead has not led to a large market share for Alpha. Digital's hopes for a significant increase in volume lie with Windows NT. The vast majority of NT users continue to work with x86 systems, as most NT customers are buying systems for \$4,000 or less. Few Alpha systems are available at this price today, but Digital plans to change that with the 21164PC, a stripped-down version of the 21164 that supposedly retains that chip's superior performance while using PC-style cache and memory chips. Digital may need a Bit of Magic Dust to deliver on this claim; if it does, users willing to consider a non-x86 processor will find the 21164PC a solid competitor for Klamath in the high-end NT market.

Contrary to our projections, Mitsubishi stayed aboard the Alpha ship despite another year of essentially no Alpha revenue. The company is a codeveloper and second source of the 21164PC and thus could take advantage of any NT gains. The potential for NT-on-Alpha also attracted newcomer Samsung to the fold. The Korean giant will initially focus on the 21264 core but may try to muscle in on the 21164PC action. By 1998, Mitsubishi could get Caught in a Squeeze Play between Samsung's low manufacturing costs and Digital's developed sales channels.

The second prong to Digital's NT strategy is FX!32. This emulation/translation software wins our **Alchemy Award** as the best product yet to convert x86 code into RISC. Although much delayed, FX!32 finally achieved open availability last fall. At least by some measurements, the product achieved its goal of delivering 70% of native Alpha performance when running translated x86 programs. FX!32, combined with native versions of Microsoft Word and Excel as well as many performance-hungry applications, will help wean some NT users from their x86 systems.

For Alpha to succeed, particularly from the viewpoint of Mitsubishi and Samsung, the platform must ultimately attract more system vendors. The Silicon Graphics purchase of Cray, which will ultimately replace the Alpha chips in Cray's MPP system with MIPS processors, leaves Digital as the only Alpha system vendor most people have ever heard of. To make its chips more attractive, Digital has given up its title as maker of the **Most Expensive Microprocessors**. As we recommended last year, the company cut its processor prices in half, bringing them more in line with Intel's.

Any meaningful financial benefits from the NT strategy are unlikely to accrue before 1998. The Alpha vendor must find some other way to stem its recent flow of red ink before the wave drowns corporate interest in Digital products.

#### PowerPC Resets Goals

During the past year, IBM Microelectronics and Motorola got their act together, taking advantage of new manufacturing processes to aggressively increase the clock speeds of their mainstream PowerPC chips. With both companies shifting most of their production to 0.35-micron CMOS, the 603e climbed to 240 MHz while the 604e reached 225 MHz, earning the rarely seen **Ahead of Schedule** award. The vendors also reined in their marketing groups, not announcing products until they were actually shipping, for a change.

Unfortunately, this success did not extend to the illfated PowerPC 620. This chip, originally due in 3Q95, wins the **Flying Dutchman** award: doomed to roam the seas forever, occasionally glimpsed through the mist but never finding its way to port. The latest plan has the 620 showing up in IBM systems sometime in 2H97—maybe. Users needing 64bit support may instead turn to IBM's Apache, an internally developed 64-bit PowerPC processor. This would leave Groupe Bull as the only customer for the 620.

After reaching the end of the original PowerPC roadmap (except for the aforementioned Dutchman), Motorola and IBM unfurled a new map that extends through 2001, giving them the Biggest Crystal Balls award. This year will see the debut of the first G3 processors, which are derived from the 603 and 604 cores but add new cache and bus interfaces to increase performance. The G4 is due in late 1998, and the 2K is planned for 2001.

Despite recent advances, PowerPC has little hope of establishing a significant performance advantage over Intel's processors. And while every other major processor vendor is adding multimedia extensions, the PowerPC partners refuse to even acknowledge a plan to implement them, earning the partners a dubious Mental Eclipse award. This blind spot will put PowerPC chips well behind Intel's MMX processors in performance on many multimedia applications.

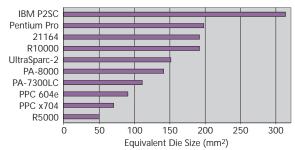

IBM rolled out its P2SC, a single-chip version of its Power2 processor, last fall. The massive chip wins several awards, including Most Transistors (15 million), Best Memory Bandwidth (2.2 Gbytes/s), and on the downside, Highest CPU Manufacturing Cost (\$375 estimated). The six-way superscalar POWER processor offers pedestrian integer performance but superlative speed on high-end scientific code and high-bandwidth commercial applications such as OLTP.

Newcomer Exponential unveiled its x704, due to ship in 2Q97. The PowerPC chip uses bipolar logic to achieve clock speeds of up to 533 MHz and better projected performance than any PowerPC processor from Motorola or IBM. We give this chip the Light Bulb award, in honor of its good ideas and its power dissipation (85 W). Apple and others will use this chip in high-end Macintoshes.

Even as the PowerPC hardware plot improved, the software story descended into lurid prose. PowerPC wins the award for **Most Dead Operating Systems**, as IBM dropped OS/2 support, Sun de-emphasized Solaris for PowerPC, and Windows NT on PowerPC is left with no announced system vendors. The once all-consuming PowerPC universe has essentially collapsed to proprietary IBM operating systems (AIX, OS/400) and Mac OS.

Despite the dire straits of its own company's processor, IBM's PC group continues to thwart every attempt to leverage its sales channels in support of PowerPC, earning the **Barry Bonds Poor Teammate** award. IBM has a license to sell Mac clones and could become the first major PC maker outside of Apple to adopt Mac OS, but don't expect to see this happen any time soon.

With the evaporation of NT support, major vendors such as Canon and Toshiba have abandoned the PowerPC ship. Although Apple finally opened its Mac OS licensing campaign early last year, it was a case of **Right Place, Wrong Time**. The unimpressive results are that Macintosh clones are available from Motorola and a handful of small companies that few non-Mactivists would know.

The inability of IBM and Motorola to deliver significantly better performance or price/performance than Intel has led to this lack of interest. Recent improvements are simply **Too Little, Too Late**. There remains little reason to use PowerPC for any software that already runs on x86. At this point, PowerPC's market share is tied to Mac OS, the one operating system that doesn't run on x86. Apple's ongoing problems, however, have caused the Mac's market share to drop from about 10% to 7% in the past year, as forecast by Nick Tredennick (see MPR 9/12/94, p. 18).

We're not sure what to make of Apple's new OS strategy (see page 5). If the plan fails, Apple's share will continue to plummet, although the Mac faithful may keep the company alive indefinitely. But even in the best case, a revived Mac OS, along with the next-generation Rhapsody OS, seems unlikely to exceed a single-digit market share. Interestingly, Next's OS has already been ported to x86; we would not be surprised to see Rhapsody on x86 or IA-64 as well as on PowerPC.

Many pundits, including ourselves, had forecast that PowerPC could achieve a 20% share of the desktop market by 2000. Now, it looks like PowerPC will be lucky to own 5–10% at that point. This share is still far better than that of any other RISC and is plenty to keep the architecture afloat, but it won't threaten Intel and, compared with the initial bright hopes for PowerPC, is a **Major Disappointment**.

#### **HP Regains Performance Competitiveness**

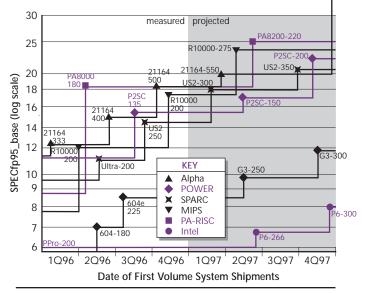

As Figure 1 shows, HP started 1996 trailing the other major processor vendors, including Intel, in integer performance. The debut of the PA-8000 in April changed all that, pushing HP into the lead in both integer and floating-point performance and completing a **Worst-to-First Leap**. Although the 500-MHz 21164 later surpassed HP's integer score and matched its floating-point score, the PA-8000 remains ahead of all other shipping microprocessors.

### Major RISC Events of 1996

Digital's 21164 rocketed from 333 MHz (2/12/96, p. 4) to 400 MHz (3/5/96, p. 4) and then 500 MHz (7/8/96, p. 1). The company also revealed its superfast 21264 (10/28/96, p. 11). Samsung signed on as a third source for Alpha processors (7/8/96, p. 4). Digital cut its processor prices in half (12/30/96, p. 5).

Digital gave a peek at its low-cost 21164PC (4/15/96, p. 4 and 10/28/96, p. 4). The chip will be the first with Alpha's multimedia extensions (11/18/96, p. 24). The company's FX!32 emulator/translator (3/5/96, p. 11) began shipping in the fall (10/28/96, p. 4).

**Exponential** taped out its BiCMOS PowerPC chip in January (2/12/96, p. 6) and described its internal architecture at the Microprocessor Forum (10/28/96, p. 1).

The PowerPC 604e jumped to 180 MHz (5/6/96, p. 4), then eased up to 200 MHz (5/27/96, p. 13) and ultimately 225 MHz (8/5/96, p. 5). The PowerPC 603e used a shrink to 0.35-micron CMOS to reach 200 MHz (5/27/96, p. 13) and later 240 MHz (10/28/96, p. 5).

Motorola and IBM jointly revealed a new PowerPC roadmap (8/26/96, p. 12).

Apple expanded its Mac OS licensing program by allowing Motorola (3/5/96, p. 4) and IBM (5/6/96, p. 11) to sublicense the OS to third parties. By year end, seven companies had licensed Mac OS (10/7/96, p. 5).

IBM began shipping its P2SC processor in August (8/26/96, p. 14) and outlined plans to deploy a 64-bit Apache processor in mid-1997 (3/25/96, p. 4).

HP shipped limited volumes of the PA-8000 in April (4/15/96, p. 4), seizing the performance lead from Digital. PA-8000 workstations followed in June (6/17/96, p. 4). HP revealed plans for the PA-8200 and 8500 at the Microprocessor Forum (10/28/96, p. 18).

MIPS announced MIPS V and MDMX (11/18/96, p. 24). R10000 servers began shipping in March (2/12/96,

p. 4), but workstations didn't ship until the fall (10/7/96, p. 5). The R5000 was announced at 200 MHz (1/22/96,

p. 10) but shipped at 180 MHz (2/12/96, p. 4).

QED announced plans to sell its own chips (9/16/96, p. 5) starting with the RM7000 (10/28/96, p. 36).

Fujitsu's TurboSparc (11/18/96, p. 17) began shipping as a successor to MicroSparc-2. Sun revealed plans for UltraSparc-2i (10/7/96, p. 1), which will fill in the low end starting in late 1997.

Netpower dumped MIPS in favor of Pentium Pro (3/5/96, p. 5). Amdahl chose Pentium Pro over RISC (5/27/96, p. 4). Compaq rolled out its first workstations, all based on Pentium Pro (9/16/96, p. 5).

Microsoft dropped support for **Windows NT** on MIPS (10/28/96, p. 5). IBM and Motorola extinguished NT on PowerPC (12/30/96, p. 4).

The PA-8000 is an impressive device. With a buffer of 56 instructions, it has the Most Reordering Capacity of any microprocessor (see page 27). Its dual floating-point multiply-accumulate units are also unique. All this power comes at a price: at 345 mm<sup>2</sup> in an antiquated 0.5-micron process, the PA-8000 also takes the award for **Biggest Die.**

The company plans to stay in the performance race with a pair of processors derived from the PA-8000. The PA-8200, due this spring, will boost performance by about 40% with a few relatively small changes and a clock-speed boost. As Figure 2 shows, this chip should give HP leadership FP performance, at least until the 21264 appears. The PA-8500, planned for mid-1998, will challenge the 21264's performance using a 0.25-micron process. The 8500 will fill the gap until Merced appears in 1H99.

HP started shipping its new midrange processor, the PA-7300LC, in September. The chip delivers performance similar to that of a 200-MHz Pentium Pro (a bit better on FP, a bit worse on integer). HP itself is now selling Pentium Pro workstations, preparing for the ultimate unification of its product lines around Merced and other IA-64 chips. While the company has a solid plan to address the high end, efforts on IA-64 may prevent progress in the midrange; the 7300LC is probably the last PA-RISC chip to address that space. Well before Merced appears, many HP customers will be faced with the choice of paying a premium to stay with PA-RISC or getting maximum price/performance by adopting Pentium Pro. At least HP can make a sale in either case.

### Silicon Graphics Revamps Products

SGI spent the year reworking its entire system lineup, moving to the R10000 at the high end and the R5000 at the low end. Both chips provided performance disappointments, earning MIPS a penalty for **Elastic Marketing Claims**. The

Figure 2. HP is tied for the FP performance lead with Digital and hopes its PA-8200 will reign supreme during 2H97. (Source: SPEC for 1996 data, MDR for 1997)

R5000 was announced at 200 MHz but never got past 180 MHz in SGI's systems. Performance fared worse, as the announced 5.2 SPECint95 (base) turned into 4.0 when systems rolled out, although it later crept up to 4.7. The chip is now shipping at 200 MHz in embedded applications but not in workstations.

The R5000 offers significantly lower performance than a Pentium Pro, even on floating-point code, but it costs much less to manufacture. In fact, at just \$25, the R5000 has the **Lowest Manufacturing Cost** among all desktop RISC processors. Although this low cost will ultimately aid the R5000 in the embedded market, it does little to help SGI.

The R10000 rolled out in 1Q96, but yield problems prevented the processor from achieving significant volume until the fall. NEC and Toshiba continue to be unable to get more than a few parts to yield at the advertised 200 MHz, although there are enough 195-MHz parts to enable SGI to ship some high-end servers at that speed. These yield problems caused the price of the 200-MHz R10000 to remain at \$3,000, making it the **Most Expensive Microprocessor.**

The R10000 had its own performance disappointment: the initial systems were rated at 13 SPECfp95 (base), far short of the 18 originally promised. MIPS explained that system limitations were hampering performance, and by the end of the year, new systems appeared that demonstrated the "true" performance of the R10000 is 17.4 SPECfp95. A final blow was NEC's manufacturing problem that forced it to recall the few thousand R10000s it had shipped, earning the Most Embarrassing Bug award.

The past year also saw the demise of Windows NT on MIPS, a promising product cruelly ignored by MIPS parent Silicon Graphics. Earning a Squandered Advantage penalty, SGI's complete disdain for NT drove Acer, NEC, and ultimately all other NT-on-MIPS system vendors from the market, leaving Microsoft no choice but to pull the plug, despite having originally developed NT on MIPS systems.

In 1997, SGI will look to the RM7000 to revitalize its midrange. This chip, the first sold under the QED name, is projected to deliver in excess of 10 SPECint95 and 10 SPECfp95, keeping pace with Intel's high end. The R10000 should see a shrink to 0.25-micron in 1H97, boosting the clock speed to 275 MHz and keeping SGI in the performance race with other high-end RISC vendors.

#### Sun Focuses on Java

It seems an odd match, but we are giving Sun the Silent Running award for saying so little about SPARC during 1996, at least in part because the Java spigot was on full (see page 16). One minor misstep: Sun Microelectronics (SME) announced a 182-MHz version of UltraSparc that never shipped; the vendor jumped directly to 200 MHz a quarter later.

In a bigger snafu, SME claimed UltraSparc-2 was shipping in volume at 250 MHz back in June, yet to date the part has appeared in only a few expensive Sun servers for which no benchmarks have been published, earning UltraSparc-2 a **Phantom Product** citation. The culprit appears to be Texas Instruments' manufacturing process, as the UltraSparc-2 design has been complete for months. TI's aggressive plans to advance its IC process technology (see MPR 9/16/96, p. 11) seem to be falling short.

Even if we give Sun credit for the estimated performance of its 250-MHz part, the company languishes in its traditional role of sporting the **Slowest High-End Processor**. If TI can get back on track, UltraSparc-2 may reach 350 MHz this year, but this improvement will be merely enough to compete with Intel's Klamath and the PowerPC G3 for last place in the integer performance race.

Throughout 1996, Sun Microsystems (SMCC) relied on the skanky MicroSparc-2 (1.4 SPECint95) to "power" its low-end and midrange workstations. SMCC recently rolled out systems based on Fujitsu's new TurboSparc chip, which offers twice the performance of MicroSparc-2 but still lags well behind Pentium, much less Pentium Pro, in performance. To gain a competitive low end, Sun needs to move to UltraSparc-2i, a highly integrated derivative of UltraSparc, but this chip isn't due until late 1997 or early 1998.

SMCC's adoption of UltraSparc ended its brief flirtation with Ross Technology's HyperSparc CPU. This loss, coupled with the erosion of the SPARC clone market, left Ross reeling; expenses exceeded revenues by more than 30% in the most recent quarter. Apparently, Ross didn't expect Sun to cut off its purchases of HyperSparc, earning the Texas vendor the **Jeane Dixon Forecasting** award.

#### Intel Gains Despite Slips

In a change of style, Intel rolled out four speed grades of its new Pentium Pro processor in late 1995 rather than doling them out one per quarter. This strategy vaulted Intel into the integer performance lead, albeit briefly, and garnered plenty of attention. For 1996, however, we are flagging Intel for **Illegal (Lack of) Motion,** as the 200-MHz Pentium Pro remained its high-end processor for the entire year. This inactivity leaves Intel well behind Digital and HP—and, to a lesser extent, MIPS and PowerPC—in integer performance, although Intel still leads the laggard SPARC.

Things are looking better for 1997. The next P6 processor, Klamath, is expected to appear in 2Q, boosting clock speeds to 266 MHz. Faster clock speeds await the deployment of Intel's 0.25-micron process, due in 2H97. We expect to see the P6 hit 300 MHz by the end of this year, but even this improvement will not allow Intel to approach the performance lead in 1997.

Intel's only new desktop processor for most of 1996 was the 200-MHz Pentium. Introduced with "immediate availability" in June, the chip was extremely difficult to find in systems until well into the fall, earning Intel a **Phantom Product** citation. Intel denies any production problems; the good news is that the chip is now widely available.

Despite these problems, even the 1995-vintage Pentium Pro was enough to disrupt RISC vendors' plans. Earning an **Operation Crush** award, the chip delivered enough performance to block MIPS and PowerPC from gaining NT design wins, as vendors from Amdahl to Netpower chose Pentium Pro over RISC chips. Only Alpha, with its superior performance, remains to challenge Intel in the NT space.

These NT vendors represented only incremental business to RISC chip vendors, so losing them does little harm. Pentium Pro's real threat is against the RISC workstation and server businesses that form the heart of the revenue streams of Sun and Silicon Graphics. This threat is exemplified by Compaq's entry into the workstation market, with its lineup based entirely on Pentium Pro and Windows NT. These systems offer performance (integer, floating-point, and 3D graphics) similar to that of low-end and midrange RISC workstations but, taking advantage of PC components and economies of scale, at significantly lower prices.

Leveraging their own PC businesses, Digital and HP are now offering similar Pentium Pro workstations, using the **Eat Your Own Young** strategy popularized by Intel. Sun and SGI, however, have no such alternative; their low-end and midrange business appears doomed. Sun is trying to reinvent itself as a high-end-server and thin-client vendor, while SGI appears to be positioning itself as a high-end 3D and supercomputer company. Both companies see Web servers as a major market opportunity, although Pentium Pro will provide competition there as well. We believe these tricky business conversions will limit growth for at least the next few years, making it more difficult to support in-house RISC architectures such as SPARC and MIPS.

#### Intel Challenges Cozy RISC Vendors

Within the cozy confines of the RISC enclave, 1997 appears devoid of earthshaking events. Digital and HP will vie for the performance leadership crown. Quarter-micron versions of the R10000 and UltraSparc-2 will improve the competitiveness of these parts. PowerPC and Intel will trail in performance, particularly on floating-point applications, but the gap on integer code will not be as great as in the past. No new processor cores are slated to appear from the major vendors until the debut of the 21264, likely to be at the very end of the year (or later). When it appears, the forthcoming Alpha chip will open an enormous performance gap.

Among customers considering either RISC- or Intelbased systems, however, the plot is more likely to resemble that of *Mars Attacks!*, with the P6 playing the role of the little green men. The combination of the P6 and Windows NT delivers a price/performance advantage over RISC/Unix systems, and the P6, particularly in low-cost dual-processor configurations, can match the performance of all but the fastest RISC systems on most tasks. Because of the high degree of software lock-in among RISC users, this effect will not vaporize any RISC vendors overnight, but it will place a drag on sales and particularly on profits. As in *Independence Day*, RISC vendors must devise an innovative solution to thwart an incredibly powerful and aggressive foe.

# First Media Processors Reach the Market

## Programmable Solutions from Chromatic, Philips Gain Momentum

by Peter N. Glaskowsky

Despite limited availability in 1996, media processors became a significant factor in the PC market. Several new architectures were introduced in 1996. There are now three major architec-

tures for the PC market, and designers of consumer electronics have several to choose from.

Most of the activity was behind the scenes: building strategic relationships between hardware and software vendors and attempting to influence the development of 3D and multimedia architectures at Microsoft. These efforts will guide the formation of the market over the next few years.

This year will be much busier than last, as the plans of several vendors finally reach fruition and customers get their first look at the new technology. Products based on Chromatic's Mpact will hit the streets this month or next, with the Philips TriMedia only three months behind. Samsung's more ambitious MSP should arrive late in the year, finally allowing direct comparisons among the three chips based on real applications instead of raw clock rates.

While these three vendors are hoping to gain design wins in both PCs and consumer products, other vendors are more narrowly focused on consumer devices. By eliminating some of the overhead required by PCs, such as floating-point support and a PCI interface, these embedded chips aim to reach the lower price points required for consumer products. Fujitsu and Mitsubishi have announced such devices, with DVD players as the primary target; Oak and C-Cube are expected to follow suit this year.

Rendition is in a class by itself. With its programmable core, the Vérité chip looks much like other media processors, but the company has positioned the device solely as a 3D accelerator for PCs. Vérité competes mainly against hardwired 3D graphics chips.

### Combining Capabilities Can Cause Confusion

Flexibility, the greatest advantage of media processors, may also be their biggest problem. In some ways, media processors are a middle-of-the-road technology. In theory, they combine the cost/performance advantages of hardwired solutions with the flexibility of software implementations. This opens them to competition from several directions, however. Makers of hardwired graphics and audio chips, along with softwareonly vendors, can target specific aspects of PC multimedia and sometimes offer better point solutions.

The media-processor solution does not satisfy all PC OEMs. Some system vendors believe that the classic

approach, with separate subsystems for graphics and audio, provides a more useful form of flexibility. By offering a selection of graphics solutions—a low-end 2D/3D chip on the motherboard, or a few different PCI cards—as well as hardware and software alternatives for audio, vendors can create a well-differentiated product line. Media-processor boards can be difficult to fit into this strategy. Even though media processors can provide high-performance graphics along with high-quality audio, they potentially eliminate several configurations from a system vendor's product line.

This problem is really the result of the checklist mentality that prevails at many PC vendors. Product differentiation is achieved by checking off a different set of items—3D acceleration, MPEG playback, wavetable audio, etc. Media processors are just too good at this game: they allow the vendor to check off every box, as long as the media processor has the right software available.

The narrow checklist view makes media processors look so good that vendors have a hard time explaining why the user should want any other system configuration. The solution to this quandary is to offer media-processor solutions at several performance levels. Low-end and midrange systems can be differentiated solely by the software components sold with the system, while high-end systems can be equipped with faster hardware and even more software.

#### Chromatic to Take Early Lead

The first full-featured media processor to ship will come from Chromatic Research. Chromatic's two original partners, Toshiba and LG Semicon, shipped the first production units of the Mpact/3000 media processor to OEMs in September of last year. In November, SGS-Thomson became the third (and final, according to Chromatic) source for Mpact. SGS-Thomson is likely to begin shipping product in late 1997.

The key strengths of first-generation Mpact parts are in the areas of 2D graphics, audio, and MPEG-2 playback. Mpact's 3D performance will improve dramatically with the arrival of floating-point hardware and a rendering pipeline on Mpact 2, but Mpact/3000 is at least competitive with lowend 3D chips like the S3 Virge and ATI Rage.

No Mpact-based products have yet appeared in retail sales channels, and only LG Electronics has even announced a board-level Mpact product. Even so, Chromatic anticipates strong sales this year, primarily in motherboard applications. The Mpact R/3000 and R/3600 are expected to ship in volume in 1Q97, adding an internal RAMDAC and a faster speed grade, with the Mpact 2/6000 shipping in 3Q97. This lineup will give Chromatic customers four parts to choose from, providing much-needed product-line differentiation.

11

| .8.    |

|--------|

| . y V. |

| × 3/   |

| ~//    |

|                         | Chromatic<br>Mpact R/3000 | Chromatic<br>Mpact 2/6000 | Philips<br>TM-1 | Philips<br>TM-PC | Samsung<br>MSP-1 | Samsung<br>MSP-1G |

|-------------------------|---------------------------|---------------------------|-----------------|------------------|------------------|-------------------|

| 2D acceleration         | Yes                       | Yes                       | No              | Yes              | No               | Yes               |

| 3D geometry (polys/s)   | n/a                       | 1M                        | 750K            | 750K             | 750K             | 750K              |

| 3D setup (polys/s)      | n/a                       | 1.2M                      | 1M              | 1M               | 750K             | 750K              |

| 3D fill rate (pixels/s) | 5M                        | 42M                       | n/a             | n/a              | n/a              | n/a               |

| MPEG-1 decode           | Yes (SW)                  | Yes (SW)                  | Yes (SW)        | Yes (SW)         | Yes (SW)         | Yes (SW)          |

| MPEG-2 decode           | Yes (SW)                  | Yes (SW)                  | Yes (SW)        | Yes (SW)         | Yes (SW)         | Yes (SW)          |

| MPEG-1 encode           | Yes (HW)                  | Yes (HW)                  | Yes (SW)        | Yes (SW)         | Yes (SW)         | Yes (SW)          |

| Videoconferencing       | Yes                       | Yes                       | Yes (SW)        | Yes (SW)         | Yes (SW)         | Yes (SW)          |

| Video in                | Yes                       | Yes                       | Yes             | Yes              | Yes              | Yes               |

| Video out               | Yes                       | Yes                       | Yes             | Yes              | Yes              | Yes               |

| Audio support           | Yes                       | Yes                       | Yes             | Yes              | Yes              | Yes               |

| Telephony support       | Yes                       | Yes                       | Yes             | Yes              | Yes              | Yes               |

| Clock rate              | 62.5 MHz                  | 125 MHz (est.)            | 100 MHz         | 100 MHz          | 100 MHz          | 160 MHz           |

| Integer ops/cycle       | 48                        | 48                        | 38              | 38               | 64               | 64                |

| Peak integer perf       | 3.0 GOPS                  | 6.0 GOPS                  | 3.8 GOPS        | 3.8 GOPS         | 6.4 GOPS         | 10.2 GOPS         |

| Int width at peak perf  | 8 or 9 bits               | 8 or 9 bits               | 8 bits          | 8 bits           | 8 bits           | 8 bits            |

| Peak FP performance     | n/a                       | 0.5 GFLOPS                | 0.5 GFLOPS      | 0.5 GFLOPS       | 1.6 GFLOPS       | 2.5 GFLOPS        |

| Local RAM bandwidth     | 500 Mbyte/s               | 1200 Mbyte/s              | 400 Mbyte/s     | 400 Mbyte/s      | 800 Mbyte/s      | 1280 Mbyte/s      |

| Open SW dev env         | No                        | No                        | Yes             | Yes              | Yes              | Yes               |

| Price for chip          | \$50                      | n/d                       | \$50            | \$53             | n/d              | n/d               |

| Production date         | Now                       | n/d                       | Now             | 8/97             | 3Q97             | n/d               |

Table 1. Samsung's MSP-1 shows a clear advantage in both integer and floating-point performance compared to other PC media-processor architectures, while Chromatic's Mpact includes the broadest range of features. n/a=not applicable, n/d=not disclosed (Source: vendors)

Introducing second-generation Mpact technology even before first-generation parts had reached the hands of end users was a gutsy but correct decision. Chromatic is a small company, and Mpact 2 should reassure potential customers that Chromatic is determined to become a significant force in the PC market.

#### Software, Business Models Evolve

High-performance media processors mean nothing to end users without software to implement the necessary multimedia algorithms. Chromatic refers to this code generically as Mediaware, and derives most of its revenue from Mediaware licensing. Licensing fees for chip designs are calculated to cover the cost of chip development, not to generate profit.

Chromatic has released version 1.0 of its Mediaware library, which supports basic 2D, 3D, audio, telephony, and digital-video functions. The company has already described some of its plans for the next release in 1H97, adding DVD support, videophone operation, and more advanced audio and telephony features. This next release will also take advantage of MMX extensions, if present, to reduce hostprocessor overhead. All of this work is being done by Chromatic's 100+ software engineers, certainly a challenging task.

Chromatic does not make it possible for its semiconductor partners, or anyone else, to develop software for Mpact, although the company remains open to the possibility if a compelling case is offered for some specialty function. Aside from business issues, developing for a complex VLIW (very long instruction word) SIMD (single-instruction multiple-data) architecture is inherently difficult. If Chromatic were to allow third-party software development, it would have to expend considerable effort on tools, training, and technical support for the independent developer.

#### TriMedia Provides First Competitor to Mpact

The Philips TriMedia TM-1 is close on the heels of Mpact. Entering production only three months later than the Chromatic design, the TM-1 offers potentially better performance at a higher cost. As Table 1 shows, the chip's processor core is more directly comparable to the Mpact 2's, since it includes floating-point support. Both use VLIW and SIMD techniques to achieve high performance on multimedia algorithms.

Philips, however, chose not to include hardware support for 2D/3D graphics or MPEG encoding in the TM-1. While the TM-1 is nominally capable of acting as an SVGAcompatible display controller with the appropriate firmware, performance is likely to be unacceptably slow in this mode, and Philips does not emphasize this capability. Later TriMedia parts will remedy this omission.

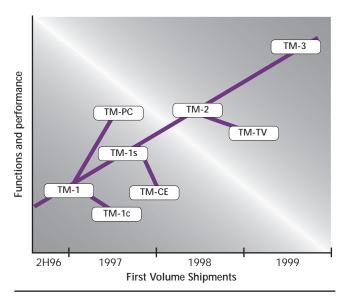

In fact, Philips's roadmap refers to no fewer than seven TriMedia derivatives, as Figure 1 shows. By the end of 1997, Philips may be shipping the TM-1 (itself a shrink of previous internal versions), a TM-1c with further feature shrinks, a TM-PC for Microsoft's Talisman, and a TM-CE version for consumer-electronics applications. In 1998, Philips expects to have a TM-2 with 4× the performance of the TM-1 and additional (but unspecified) features. TM-2 will beget TM-TV, a version for interactive televisions from the Philips consumer-electronics division. An even faster part, described only as TM-3, may arrive in 1999.

In other respects, the TM-1's level of integration is similar to that of Mpact 2, with digital audio and video I/O. The

Figure 1. Philips's Trimedia roadmap shows a plethora of parts, including the mainline of TM-1, TM-2, and TM-3 as well as several derivatives aimed at specific markets. (Source: Philips)

Philips TM-1 reference design emphasizes these features, providing video digitizing and playback plus sound and telephony features. Most TM-1 products will follow the same pattern, leaving 2D/3D graphics on the motherboard or a separate expansion card.

Apple's recent adoption of TriMedia fits well with the part's current capabilities. This plan is similar to Apple's earlier use of a DSP for QuickTime acceleration. The coprocessor approach was dropped when Apple moved from the 68K to PowerPC, but now it's back. TriMedia thus becomes Apple's response to Intel's MMX. IBM, Motorola, and Apple have not developed multimedia extensions for the PowerPC processor family, so Apple was forced to find another way to provide multimedia acceleration for its platform.

#### Samsung Promises Best Performance

The most ambitious media-processor design yet described is Samsung's MSP. Although the first 100-MHz MSP is not scheduled to ship until 3Q97, Samsung has already described a 166-MHz follow-on that will exceed 10 BOPS on 8-bit data. Even the 100-MHz part matches the integer performance of Mpact 2 in the same time frame.

MSP shines in floating-point throughput. Its 256-bitwide SIMD engine—four times wider than Mpact's—supports a 32-bit IEEE-compliant floating-point representation in addition to the 8-, 16-, and 32-bit integer formats common to most media processors. The result is a peak execution rate of 1.6 GFLOPS on multiply-accumulate operations at 100 MHz, far exceeding the FP capabilities of all other announced parts, as Table 1 shows. Floating-point performance translates directly to 3D geometry performance, giving MSP a significant advantage over host-based geometry processing and other media processors on complex 3D scenes with many small triangles.

Samsung sidestepped another problem faced by other media-processor vendors: the inefficiency of scalar tasks like communications and scheduling on vector processors. Instead, MSP includes an independent ARM7 processor core to handle system-level tasks like scheduling and host communication without interfering with the vector processor.

### Talisman Offers Opportunity for TriMedia, MSP

Although Philips and Samsung plan to add limited 2D and 3D support to future versions of their media processors, the best opportunity for market-leading 3D performance for both architectures will come from Microsoft's Talisman initiative. Talisman defines a radically new 3D rendering architecture with chunk-based rendering and dynamic imagelayer compositing. Aimed at the entertainment-software market, Talisman's enhancements should yield dramatically higher 3D throughput.

Microsoft's Talisman reference design will use TM-PC to accelerate 3D geometry calculations as well as audio and video operations, creating a comprehensive single-board multimedia solution that places very little demand on the host CPU except for scene definition and data-structure

Samsung's MSP is also part of the Talisman program, but MSP's schedule is far enough behind the TM-1's that Microsoft has settled on TM-1 for the first reference design. Samsung will produce its own reference design once MSP is ready, giving software vendors two Talisman platforms to choose between.

Talisman is unlikely to have much effect on the market in 1997; we estimate fewer than 100,000 Talisman cards will be sold this year at an average price of at least \$600, mostly to software developers and forward-looking end users. Throughout the year and into 1998, however, Talisman will be a powerful influence on the development of 3D software as well as competing 3D hardware. Chromatic, for example, has emphasized that Mpact 2 will support some Talisman features.

#### TriMedia, MSP Rely on Third-Party Developers

Philips and Samsung are also doing most of their own software development, but both depend on outside vendors for key software components. Philips provides TriMedia's realtime kernel and what Philips describes as a "smart" C/C++ compiler that understands the complex static scheduling rules in TM-1. This compiler, part of a software-development environment that Philips offers for \$15,000, has been under development for seven years, and Philips believes it represents a significant edge over its competitors. The compiler comes with code libraries for many common multimedia algorithms, but Philips expects its OEM partners to differentiate their offerings by developing custom software.

Most of Samsung's software tools were developed under contract by Metaware. That company, mostly known as a tools developer for embedded development, provided a

### Microsoft's Direct3D Delayed—ISVs Eye OpenGL

Amid rumblings of dissatisfaction—and a few open defections—developers of 3D games are trying to deal with delayed and canceled releases of Microsoft's critical Direct3D API.

Direct3D, part of Microsoft's DirectX APIs, provides a software interface between application programs and 3D accelerators. It includes a hardware abstraction layer (HAL) that translates the commands and data structures into the proper format for the 3D hardware. Direct3D also includes a hardware emulation layer that takes over some functions for 3D accelerator chips that provide only partial acceleration.

Microsoft had planned to release version 3.0 of DirectX in August, but it did not ship until November. A Microsoft developers conference in November was postponed until April. DirectX 4.0 has been canceled entirely, and DirectX 5.0 is not expected until midyear.

Direct3D's immediate mode is the focus of most of the trouble. Application software sends commands to Direct3D in execute buffers that are difficult to manage. Direct3D also suffers from hardware implementation problems. Microsoft has no program in place to test or enforce the compliance of 3D hardware with Direct3D. Some boards claim to implement certain features but actually don't, causing trouble for software developers that try to make use of those features. Direct3D provides capability bits to describe which features are supported, but it's difficult to develop applications that support all possible combinations.

At least one game developer has chosen not to support Direct3D until these problems are fixed. John Carmack, cofounder of Id software and lead programmer for Quake, the company's popular 3D shoot-'em-up, has been vocal in

his criticisms (finger johnc@idsoftware.com). Describing his effort to port Quake to Direct3D, he writes, "Direct3D Immediate Mode is a horribly broken API." Id canceled its Direct3D effort and now plans to release an OpenGL-based version of Quake.

OpenGL is similar to Direct3D's immediate mode and is said to have a number of advantages, including greater ease of use. Instead of execute buffers, applications simply provide a sequence of subroutine calls, each describing one vertex of a triangle. OpenGL products must pass a set of compliance tests, making performance more predictable. This increases the cost of OpenGL hardware but eliminates the need for Direct3D's capability bits and piecemeal approach to emulation.

The Direct3D controversy may also affect Microsoft's Talisman. The company's original plan was to add extensions to Direct3D to control new Talisman features such as image layers, texture compression, and anisotropic filtering. These extensions are due by the end of 1997, but any substantial changes to the baseline Direct3D API would likely delay these new features and push most Talisman applications into late 1998. Microsoft has also announced plans to add Talisman support to its implementation of OpenGL, covering its bases in the event that more game developers reject Direct3D.

The delays in DirectX releases from Microsoft may signal major changes in Direct3D. Microsoft has often released hastily prepared software just to get a foothold in a new market (probably starting with MS-DOS 1.0) and later followed up with significantly improved code. We hope that will be the case here.

C compiler for MSP's ARM and vector processors, as well as an assembler, linker, and debugger. Samsung added simulator, profiler, and decompiler tools. The tools are available for Windows 95 PCs or SPARC workstations. The lack of C++ support, as in the TriMedia development environment, is not disabling; most driver and codec development will take place at the lower C and assembly-language levels.

No matter who provides the software, all vendors of media processors remain at Microsoft's mercy for the APIs needed to use their processors under Windows. Many uncertainties remain in these software interfaces. For example, a system with an MMX processor and a media processor could perform some multimedia tasks on either chip. Chromatic is developing an x86-based resource manager that could assign a task to the least busy device, but it will be difficult to do this in a Windows-compatible way without Microsoft's help.

Microsoft's Direct3D API is coming under fire from software vendors (see sidebar). Changes in the API would

force media-processor vendors to change their software—and possibly their hardware as well, since Direct3D determines the features that 3D accelerators must support.

#### **Product Positioning Open to Debate**

These three vendors claim their media processors bring high-end features to the PC market. Chromatic emphasizes Mpact 2's 1M-polygon/s 3D throughput in support of this positioning, for example. By the time Mpact 2 arrives, however, 1M polygons/s will be merely midrange performance; dedicated 3D chips such as the Vsis 3DPro already exceed this mark. Since media processors must be priced at about \$50 to meet OEM budgets, it is unrealistic for any of the media-processor vendors to expect to surpass the performance of more expensive 3D-only hardware.

At the same time, the three vendors claim their media processors are also suitable for low-end embedded products. Philips's plans include TM-CE, a TriMedia derivative for

|                         | C-Cube<br>VRP CL-4020 | Fujitsu<br>MMA | Mitsubishi<br>D30V | Oak (un-<br>announced) | Rendition<br>Vérité |

|-------------------------|-----------------------|----------------|--------------------|------------------------|---------------------|

| 2D acceleration         | n/a                   | n/a            | n/a                | n/a                    | Yes (HW)            |

| 3D setup (polys/s)      | n/a                   | n/a            | n/a                | n/a                    | 150K                |

| 3D fill rate (pixels/s) | n/a                   | n/a            | n/a                | n/a                    | 25M                 |

| MPEG-1 decode           | Yes (HW)              | Yes (SW)       | Yes (SW)           | Yes (HW)               | No                  |

| MPEG-2 decode           | No                    | Yes (SW)       | Yes (SW)           | Yes (HW)               | No                  |

| MPEG-1 encode           | Yes (HW)              | No             | No                 | Yes (HW)               | No                  |

| Video in                | Yes                   | No             | No                 | No                     | No                  |

| Video out               | Yes                   | No             | No                 | Yes                    | No                  |

| Audio support           | No                    | Yes            | Yes                | Yes                    | No                  |

| Clock rate              | 80 MHz                | 180 MHz        | 250 MHz            | 67.5 MHz               | 50 MHz              |

| Integer ops/cycle       | 4                     | 6              | 4                  | 1                      | 2                   |

| Peak integer perf       | 0.32 GOPS             | 1.08 GOPS      | 1.0 GOPS           | 0.07 GOPS              | 0.1 GOPS            |

| Int width at peak perf  | 8 bits                | 16 bits        | 16 bits            | 32 bits                | 32 bits             |

| Local RAM bandwidth     | 160 Mbyte/s           | 720 Mbyte/s    | n/d                | 67.5 Mbyte/s           | 400 Mbyte/s         |

| Price for chip          | n/d                   | n/d            | n/d                | n/d                    | \$40                |

| Production date         | Now                   | n/d            | n/d                | n/d                    | Now                 |

Table 2. Among special-purpose media processors, MMA and D30V offer the highest integer performance, while VRP supports MPEG encoding and Vérité speeds 3D rendering. n/a=not applicable, n/d=not disclosed (Source: vendors)

consumer electronics. Samsung proposes MSP as a good part for video games and set-top boxes, and Chromatic has even suggested using Mpact for multimedia acceleration under Windows CE.

These plans also may be unrealistic. Media processors must be powerful and sophisticated to meet the needs of the PC market, but this requirement burdens them with relatively large die sizes made on advanced fab lines. This burden will make them uncompetitive with parts designed for low-cost applications. Instead, media-processor vendors should focus on the mainstream PC market, at least 40 million units a year—certainly an opportunity worth pursuing, and one that will require their full attention.

#### C-Cube Concentrates on Video Compression

Chromatic, Philips, and Samsung form the "Big Three" of the media-processor business, but other companies plan to use programmable architectures to good advantage in narrower markets. C-Cube, for example, has been a long-time advocate of programmable engines for digital-video compression and decompression.

C-Cube's VideoRISC processor (VRP) is widely used for MPEG-1 and MPEG-2 encoding by digital satellite TV broadcasters, but VRP derivatives could certainly be adapted to other tasks. The core of VRP is a fairly conventional RISC design. It executes 32-bit integer instructions in a five-stage pipeline and also supports a set of SIMD operations on four byte-size operands in an eight-stage pipe shared with the integer engine.

Like most media processors, VRP includes some fixedfunction logic. A variable-length-coding unit offloads the relatively simple data-compression tasks from the CPU, and a motion estimator accelerates MPEG compression by comparing 8×8-pixel blocks against two reference frames at an effective rate of two billion operations per second. Even with its on-chip caches, DRAM controller, and video and host I/O interfaces, VRP is small enough to allow C-Cube to offer one or two complete VRPs on a single chip. The current implementations run at up to 80 MHz. At this speed, a single device can perform limited MPEG-1 encoding; multiple VRPs in parallel are used for higher quality and for MPEG-2 encoding.

Future VRP derivatives could include more than two VRPs per chip and operate at higher clock rates. Digital video is likely to become a major application segment in the next few years, and with the simple addition of a PCI interface, VRP could become a strong player in that market. Adding support for addi-

tional data types, including 2D/3D graphics and audio, could make VRP into a true media processor competitive with Mpact, TriMedia, and MSP. C-Cube's relationships with OEMs like Diamond, Matrox, and Orchid would provide good sales channels for such products.

#### Fujitsu, Mitsubishi, Oak Seek DVD Role

Fujitsu's multimedia assist (MMA) processor is a relatively simple 32-bit, two-way LIW design with limited 16-bit SIMD support. With a peak throughput of 1.08 BOPS at 180 MHz, the part is capable of DVD decoding but requires a separate SparcLite host processor.

MMA includes a graphics controller, audio interfaces, and several built-in peripherals but lacks a PCI interface, floating-point support, and 3D rendering capabilities. Without these capabilities, MMA is not useful for PC multimedia applications. In the DVD application, however, MMA is a good fit. By way of comparison, MMA could replace as many as seven of the devices found in Toshiba's reference DVD player chip-set design.

Mitsubishi has developed the D30V, a programmable chip intended mainly for consumer devices. At just 37 mm², the D30V is the smallest of all announced media processors. At 250 MHz, it is also the fastest, as Table 2 shows. The high clock speed allows the chip to use a simple two-way LIW architecture very similar to MMA's. Even with its small die, the D30V includes 64K of on-chip memory split between instruction and data storage. The D30V also includes audio and video output circuitry and a variable-length decoder.

Oak Technology is considering its options in the DVD market. While Oak has not yet announced any parts, the company provided a fairly specific description of a RISC-based DVD decoder at the 1996 Microprocessor Forum.

The design includes a 32-bit RISC engine, but hardwired function units handle most of the work. MPEG-2 and AC-3 decoders are included, with the RISC core managing the flow of data within the device and its local memory. Such a part strains the definition of a media processor, but the presence of a programmable engine would make it easier to add additional features should Oak develop an interest in other markets.

These vendors may be satisfied with the DVD market—a total of several million units by 1998—but media processors designed for DVD could provide a foundation for future media processors for the PC market.

#### Rendition Remains Focused on 3D Graphics

Rendition's Vérité V1000 has become one of the more successful 3D accelerators in the PC 3D market. This is due in large part to Rendition's ability to form strategic relationships within the PC industry.

The V1000 is not a multimedia processor and provides only average 3D acceleration, but the part's programmability makes it more flexible than its competitors in the 3D-accelerator market. The core of the V1000 is a 32-bit RISC processor with limited VLIW capabilities. The CPU core handles 3D setup and some 2D acceleration functions. With no floating-point capability of its own, the V1000 depends on host-based geometry processing. Rendition has used this programmability to implement custom antialiasing algorithms and special effects for game titles.

The part is used in graphics adapters from Canopus, Creative Labs, Intergraph, and Number Nine, and at least 19 software vendors have announced support or, in most cases, actual products. The V1000 is currently the only 3D accelerator supported by Quake, a distinction other 3D chip vendors must envy. Rendition has not announced a successor to the V1000, but we expect to see one early this year, offering more competitive performance and reinforcing Rendition's solid position in the market.

Missing in Action: Mfast, MicroUnity, and Nvidia In spite of impressive specifications, IBM's Mfast project has been canceled. First described at the Microprocessor Forum in 1995, Mfast was designed to yield 10 BOPS of sustained performance on 16-bit operands and was planned to ship in mid-1997. Research continues, but all product plans have been shelved.

MicroUnity's original MediaProcessor, an impressive five-thread 1-GHz BiCMOS design, failed for lack of applications requiring its level of performance (and able to pay its price), but the company continues to develop a single-threaded CMOS MediaProcessor that may find uses in cable modems or other broadband-RF devices.

Nvidia's NV1 became a casualty of mixed messages. While it is an adequate 3D accelerator that offers audio support through an integrated DSP engine, the chip's sales suffered from a mistargeted and misunderstood marketing campaign touting its nonstandard 3D interface. Today, the NV1 is essentially obsolete. The NV3, planned for a 1Q97

#### Multimedia Milestones of 1996

Chromatic (www.chromatic.com) began shipments of its Mpact 1 media processor and disclosed the design of its next-generation Mpact 2 device (11/18/96, p. 1). The company later said SGS-Thomson will join LG Semicon and Toshiba in building and selling Mpact chips (12/9/96, p. 5).

Fujitsu (www.fujitsumicro.com) debuted its MMA design, a media processor intended for DVD players (11/18/96, p. 11).

MicroUnity (www.microunity.com) canceled its BiCMOS media processor, laying off much of its staff (8/5/96, p. 5). The company is developing a simpler CMOS processor for cable modems (10/28/96, p. 4).

Mitsubishi (www.mitsubishi.com) developed the D30V, a single-chip DVD decoder (12/9/96, p. 1).

Oak (www.oaktech.com) previewed a DVD decoder with a programmable RISC core (11/18/96, p. 5).

**Philips** (www.semiconductors.philips.com) neared completion of its TM-1 media processor.

Rendition (www.rendition.com) rolled out its Vérité chip, a programmable 3D accelerator (5/6/96, p. 1).