# PCMCIA Defines Standard For PC Cards Originally Intended for Memory, Standard Expands to Cover I/O

#### **By Brian Case**

Over the next few years, smaller, lighter laptop and hand-held computers are expected to become one of the largest segments of the computer system market. Despite the fact that many of these computers will be configured for specific applications, they will need to offer expandability to lure many buyers.

To be expandable, these small computers need small expansion cards. In an effort to prevent a repeat of the ad hoc, defacto standardization that led to the ISA bus, the 300-member Personal Computer Memory Card International Association (PCMCIA) was formed in 1989 to promote interchangeability of expansion cards among computers and other electronic equipment. As the name suggests, the PCMCIA was originally concerned only with memory cards, but since then, the standard has been broadened to cover cards that include I/O functions such as modems and LAN interfaces.

Recently, the first PCMCIA-compliant cards and computers with PCMCIA slots have appeared, and vendors of cards, systems, and support chips are rushing to participate in the potentially huge market. Dozens of companies exhibited PCMCIA technology at the recent fall Comdex (see sidebar below).

Even as all this activity is taking place, the association is struggling to evolve the standard as new features are proposed. The standard was initially focused on IBM PC-compatible systems, but a group of companies including Apple, for example, is proposing a 32-bit bus-master extension to PCMCIA while maintaining backward compatibility. In another direction, Intel has developed the Exchangeable Card Architecture (ExCA) specification, which is an implementation of PCMCIA.

### The PC Card Standard

A card that meets the PCMCIA standard is called a "PC Card" and conforms in three areas: card physical, card interface (electrical), and card software. At the lowest level, the cornerstone of the software standard is the Card Information Structure (CIS). Analogous to a table of contents, the CIS (also called the "metaformat") can contain detailed information about the the devices on the card, such as timing and voltage requirements, addressspace partitioning, and application-specific information. The CIS is discussed in detail later.

There is an existing JEIDA (Japan Electronics Industry Development Association) standard for DRAM cards that is completely separate from PC Cards but is endorsed by PCMCIA. These 88-pin cards are intended to replace SIMMs for easier system memory upgrades.

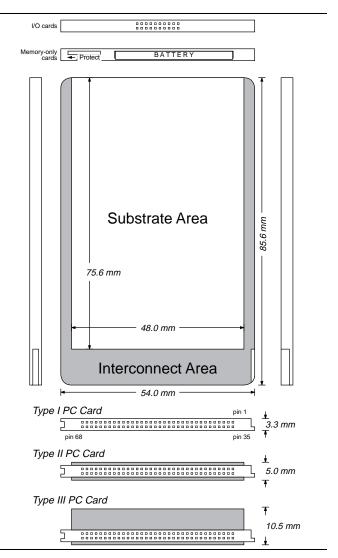

The current PCMCIA standard—release 2.01 (also published as JEIDA 4.1)—defines three physical card sizes that differ only in the thickness of the "substrate" area of the card. Figure 1 shows—in actual size—the physical dimensions of the three types of credit-cardsized PC Cards. As shown, the cards have asymmetrical edge guides to prevent incorrect insertion. Note that

Figure 1. PCMCIA card physical characteristics, shown actual size. A memory card may have a write-protect switch and battery on its front edge as shown, but they will not be present on some types of memory cards.

| Pins                                            | Signal Name     | Memory-Only I/O And Memory<br>Interface Interface                                      |                                        |  |  |  |

|-------------------------------------------------|-----------------|----------------------------------------------------------------------------------------|----------------------------------------|--|--|--|

| 30, 31, 32, 2,                                  | D0D7            | Data bus                                                                               |                                        |  |  |  |

| 3, 4, 5, 6<br>64, 65, 66, 37,<br>38, 39, 40, 41 | D8D15           |                                                                                        |                                        |  |  |  |

| 29, 28, 27, 26,<br>25, 24, 23, 22               | A0A7            | Address bus                                                                            |                                        |  |  |  |

| 12, 11, 8, 10, 21, 13, 14, 20                   | A8A15           |                                                                                        |                                        |  |  |  |

| 19, 46, 47, 48,<br>49, 50, 53, 54               | A16A23          |                                                                                        |                                        |  |  |  |

| 49, 50, 53, 54<br>55, 56                        | A24A25          |                                                                                        |                                        |  |  |  |

| 1, 34, 35, 68                                   | GND             | Ground                                                                                 |                                        |  |  |  |

| 17, 51                                          | Vcc             | Power supply                                                                           |                                        |  |  |  |

| 36, 67                                          | *CD1, *CD2      | Card Detect                                                                            |                                        |  |  |  |

| 7, 42                                           | *CE1, *CE2      | Card Enable 1, Card Enable 2                                                           |                                        |  |  |  |

| 9                                               | *OE             | Output Enable                                                                          |                                        |  |  |  |

| 15                                              | *WE/*PGM        | Write Enable/Program                                                                   |                                        |  |  |  |

| 16                                              | RDY/*BSY, *IREQ | Card ready                                                                             | Interrupt Request                      |  |  |  |

| 18                                              | Vpp1            | Programming Supply<br>Voltage 1                                                        | Programming And<br>Peripheral Supply 1 |  |  |  |

| 33                                              | WP, *IOIS16     | Write Protect                                                                          | I/O Port Is 16 bits                    |  |  |  |

| 43                                              | RFSH            | Refresh                                                                                |                                        |  |  |  |

| 44                                              | *IORD           | reserved                                                                               | I/O Read                               |  |  |  |

| 45                                              | *IOWR           | reserved                                                                               | I/O Write                              |  |  |  |

| 52                                              | Vpp2            | Programming Supply Programming And<br>Voltage 2 Programming And<br>Peripheral Supply 2 |                                        |  |  |  |

| 57                                              |                 | reserved                                                                               |                                        |  |  |  |

| 58                                              | RESET           | Reset                                                                                  |                                        |  |  |  |

| 59                                              | *WAIT           | Wait                                                                                   |                                        |  |  |  |

| 60                                              | *INPACK         | reserved                                                                               | Input Port Acknowledge                 |  |  |  |

| 61                                              | *REG            | Register Select                                                                        | Register Select &<br>I/O Enable        |  |  |  |

| 62                                              | BVD2, *SPKR     | Battery Voltage<br>Detect 2                                                            | Audio Digital<br>Waveform              |  |  |  |

| 63                                              | BVD1, *STSCHG   | Battery Voltage Card Statuses<br>Detect 1 Changed                                      |                                        |  |  |  |

Table 1. PCMCIA interface bus signals.

skinnier cards can be used in thicker slots; i.e., Type-I cards can go in Type-II slots. The standard demands that cards be opaque to trigger an optical sensor, but the substrate covers can be clear, which will allow vendors to build lucite-encased cards as promotional items.

The card has a 68-pin socket connector with two rows. The host system has a pin connector, and since the PCMCIA standard allows hot insertion and removal (i.e., while system power is active), the power and card-detect pins are of different lengths to provide connection sequencing during card insertion. Power pins are the longest at 5.0 mm and make contact first; signal pins, at 4.25 mm, make contact next; and the 3.5 mm card-detect pins make contact last.

Since the card-detect pins are at opposite ends of the connector, a detect signal at both pins indicates that all other pins have already mated. The detect pins are simply connected to ground on the card and pulled up to Vcc on the system.

PCMCIA release 1.0 defined only a memory interface even for cards that contain I/O devices. Release 2.0 adds a few signals and allows others to be redefined under software control to accommodate cards that use both memory-only and I/O interfaces.

# PC Card Interface

Table 1 lists the PCMCIA signals defined in the release 2.0 specification. As the table shows, most signals are the same for both the memory-only and I/O interfaces, but a few are different.

The PCMCIA bus provides 16 data and 26 address lines. There are three 64M address spaces: common memory, attribute memory, and I/O. The common memory address space is where all the RAM in a memory card would be mapped. The attribute memory space is where the CIS is stored and where the system accesses card configuration and control registers. Each card in a system is allocated private address spaces for common and attribute memory, but the I/O address space is shared among all PCMCIA cards installed in the system.

The REG signal is asserted by the system to select between common and attribute memory under the memory-only interface; under the I/O interface, REG acts as an enable signal. In the attribute space, only even-numbered bytes are accessible (and only D0..D7 are valid), so consecutive bytes have addresses that differ by two. IORD and IOWR indicate read and write accesses to a card's I/O space.

CE1 and CE2 enable the even-numbered and oddnumbered bytes of the data bus, respectively. Together with A0, these signals allow an 8-bit host system to access all data through the low byte of the data bus (D0..D7).

Early PC Cards were simple arrays of memory chips with fixed, known timing characteristics. For these cards, once an access starts, it completes according to the standard timing, and the RDY/BSY line is used to indicate whether or not the card can start a new access request or that the card is not done initializing after a power-up or reset sequence. Release 2.0 adds the WAIT line to allow cards to insert wait states into individual accesses.

INPACK indicates to the system that the card can respond to an I/O read at the given address. INPACK lets the system know which card is responding to an I/O access when cards are configured to do some I/O address decoding on their own; cards can either let the system do I/O address decoding and card selection or let the card decide to respond. INPACK can be used by the system to enable a data buffer between the card and the rest of the system.

For cards that incorporate battery backup, the BVD1 and BVD2 signals allow a system to detect a weak battery. When BVD2 alone is asserted, the battery is weak but still able to sustain the card's memory. If BVD1 is asserted, the battery voltage is too low to retain the contents of the oncard memory. Thus, a system can warn a user to replace the battery before data is lost and, if BVD1 is asserted, that the integrity of the data on the card has probably been compromised.

It was envisioned that a variety of memory types would be used in PC Cards. The Vpp1 and Vpp2 supplies

| Configuration Option Register (offset 0)          |             |                     |          |               |        |          |          |  |  |

|---------------------------------------------------|-------------|---------------------|----------|---------------|--------|----------|----------|--|--|

| 7                                                 | 6           | 5                   | 4        | 3             | 2      | 1        | 0        |  |  |

| SRESET                                            | LevIREQ     | Configuration Index |          |               |        |          |          |  |  |

| Card Configuration and Status Register (offset 2) |             |                     |          |               |        |          |          |  |  |

| 7                                                 | 6           | 5                   | 4        | 3             | 2      | 1        | 0        |  |  |

| Changed                                           | SigChg      | IOis8               | reserved | Audio         | PwrDwn | Intr     | reserved |  |  |

| Pin Replacement Register (offset 4)               |             |                     |          |               |        |          |          |  |  |

| 7                                                 | 6           | 5                   | 4        | 3             | 2      | 1        | 0        |  |  |

| CBVD1                                             | CBVD2       | CRdy/Bsy            | CWProt   | RBVD1         | RBVD2  | RRdy/Bsy | RWProt   |  |  |

| Socket and Copy Register (offset 6)               |             |                     |          |               |        |          |          |  |  |

| 7                                                 | 6           | 5                   | 4        | 3             | 2      | 1        | 0        |  |  |

| reserved                                          | Copy Number |                     |          | Socket Number |        |          |          |  |  |

Figure 2. The four standard I/O card configuration registers.

are present to serve the needs of flash, EPROM, and OTP devices that require special programming voltages. The actual voltages supplied on these lines are determined by information in the card's CIS. A system is required to supply  $\vee$ cc on these pins until it determines the actual requirements of the card. The standard recommends that systems be able to supply at least 12V on the lines, but some older EPROMs require either 12.5V or 12.75V.

PCMCIA release 2.0 has some provision for both 5V and 3.3V cards. As with the  $\lor$ pp supplies, Vcc starts out at 5V immediately after card insertion. The system can lower  $\lor$ cc to 3.3V if the card's CIS indicates that it is a dual-voltage card. Thus, at least part of a 3.3V card must also operate at 5V.

An I/O card is required to present a standard, memory-only interface to the system immediately after power-up or reset. Once the system determines that the card is an I/O card, the card is configured appropriately, and certain signals are redefined as indicated in the right-hand column of Table 1.

If a card has a write-protect switch, the WP signal indicates its state. IOIS16, which replaces WP for an I/O card, signals the system that the I/O address corresponds to an I/O port that can be accessed as a 16-bit quantity. When the system attempts a 16-bit I/O access and IOIS16 is not asserted, the system must break the access into two byte accesses. The interrupt request line can be either level or edge triggered. The SPKR signal provides a single-amplitude square wave to drive the system's speaker.

The status lines that are replaced by the new I/O signals are still available to the system through bits in the *Pin Replacement* register (described below). The STSCHG signal can be programmed to tell the system that one of these bits has changed state.

## Card Configuration Registers

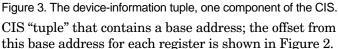

Four card configuration registers are defined in the PCMCIA release 2.0 standard, and Figure 2 shows their layouts. A given card may implement a subset or superset of these registers as necessary. The location of these registers in the attribute address space is specified by a

# **PCMCIA Proliferates**

PCMCIA cards and systems were everywhere at Comdex. Major manufacturers shipping Intel-based notebook computers with PCMCIA slots include AST, NCR, Toshiba, Sharp, and Dell; several other companies showed systems that are not yet in production. HP's highly successful 95LX palmtop also includes a PCMCIA slot. Most systems have a single PCMCIA slot, but a few have two. PCMCIA is not limited to PCs; EO's personal communicators have a PCMCIA slot, and Apple's forthcoming Newton will include one.

Most memory cards are Type I (i.e., the thinnest version), while most I/O cards are Type II. Since PCMCIA cards are too thin for most standard connectors, I/O cards typically have a "pigtail" cable that plugs into the exposed edge of the card and provides the appropriate connector at the other end.

A wide variety of memory cards is available, including flash, EEPROM, EPROM, OTP EPROM, batterybacked SRAM, DRAM, and masked ROM. Typical flash memory card sizes are 256K to 4M; a few vendors offer cards as large as 20M, but availability is limited for the larger sizes. Masked ROM cards up to 32M are available. SRAM sizes are typically 4M or smaller, but DRAM cards go up to 16M. (As with all memory products, larger capacities will be available soon.)

Most flash memory cards provide directly-accessed memory arrays and require Microsoft's flash file system or equivalent software for disk emulation, since flash memory can't be used as RAM (because of its limited endurance and slow writes). SunDisk's flash cards are unique in that they provide an on-card processor and interface that emulates a hard disk; from the system's perspective, the card *is* a hard disk. This simplifies software support and makes the card compatible with systems using any processor or operating system. Sizes range from 1 to 20 Mbytes.

Amazing as it may seem, even mechanical hard disks are available on PCMCIA cards; both 1.8" and 1.3" drives can fit within the Type III size. Typical capacities are 10 and 20 MB.

Fax modem cards are among the most popular peripheral cards, with nearly a dozen vendors. Many are 2400 bps data/9600 bps fax, but several vendors (including AT&T, whose chip set is at the heart of many of the faster cards) now offer 14.4 kbps fax and data.

LAN cards are also popular, with Ethernet cards offered by numerous vendors including AMD and Intel. Even IBM, which does not yet offer a system with a PCMCIA slot, has announced Ethernet, Token Ring, and 3270 emulation cards.

Other functions available (or at least demonstrated) on PCMCIA cards include SCSI interfaces, infrared wireless network cards, RF wireless network cards, and even a GPS (global positioning system) receiver.

In the Pin Replacement register, CBVD1, CBVD2, CRdy/Bsy, and CWProt are "sticky" bits that indicate a change in the state of the corresponding internal signal. The RBVD1, RBVD2, RRdy/Bsy, and RWProt bits allow the system to read the current states of the internal signals.

The Card Configuration and Status register contains miscellaneous status and control bits. The Changed bit is set whenever one or more of the "C" bits in the pin replacement register are set. If SigChg is also set, the STSCHG interface signal will be asserted when the Changed bit is set. The IOis8 bit tells the card that an 8-bit system intends to perform all 16-bit accesses as separate 8-bit accesses. The Audio bit enables the use of BVD2 as the SPKR signal when the card is in I/O mode. PwrDwn allows the system to force the card into a low-power state if the card supports it. Intr reflects the state of the card's internal interrupt request whether or not the card has been configured to use RDY/BSY as IREQ. If not, the system can poll the card for interrupts.

A system chooses one of potentially many card configurations by writing a value into the Configuration Index field of the *Configuration Option* register. The SRE-SET bit allows the system to selectively reset a particular card. The LevIREQ bit determines whether interrupts from the card will generate an edge or level trigger. This is important in systems where the PCMCIA interface chips are connected to a system bus, such as ISA or Micro Channel.

The Socket and Copy register contains two fields that allow the system to keep track of two or more identical cards or cards that share I/O port addresses. The Socket Number field is initialized on each card by the system with the number of the socket into which the card is plugged. The Copy Number field is used to differentiate identical cards.

# Software on the PC Card

When a card is inserted into a PCMCIA slot, the card assumes the default "memory-only" card configuration. Immediately after the card finishes its initialization (RDY/BSY signals ready), the system reads the card's CIS from attribute memory (REG active). Some older RAM cards have a "pseudo-floppy" organization with no CIS. These cards can be recognized by the values of the first few bytes of memory, which are the first bytes of a standard DOS boot block.

On newer cards, the CIS is a sequence of entries, called "tuples," that describe the card's structure and special characteristics. Each tuple begins with a one-byte tuple code followed by a one-byte link to the next tuple in the sequence. Since the link is simply a length byte, a tuple is limited to 255 bytes of information.

The release 2.0 standard defines 21 tuple codes for such things as checksums, byte ordering, device types (I/O, ROM, SRAM, flash, etc.), device speeds, device sizes, voltage requirements, and so forth.

A sequence of related tuples is called a "partition descriptor." Typically, a CIS contains multiple partition descriptors.

The metaformat encoded in the CIS is a hierarchy of four levels:

- Level 1 requires the specification of basic device information such as memory type, size, and speed.

- Level 2 describes the low-level data organization. Tuples for this level describe the location and sizes of memory partitions, any error checking methods, and geometry information (sectors, tracks, cylinders) for disk-like partitions.

- Level 3 specifies the generic, logical data organization at a higher level. The options here are DOS file system or other "block-replaceable" organization, flash file system, the Execute-In-Place (XIP) format for applications stored in ROM, and vendor-specific organizations.

- Level 4 is defined to allow system-specific standards to be defined. Currently, level-4 compatibility is defined only for DOS environments, but proprietary formats are allowed at this level.

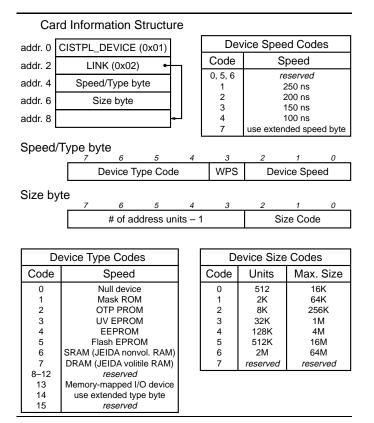

Figure 3 shows an example of a CIS tuple: a device information tuple that describes a contiguous block of memory address space. The standard requires that the

# For More Information

You can join the PCMCIA as an affiliate member for \$1000 per year, which entitles you to information only. Associate members, at \$2500 per year, get voting rights on standards issues and are eligible for five of the 14 board seats. Executive members, at \$10,000 per year, get voting rights on organizational issues as well as standards and are eligible for the other nine board seats. There are currently 18 executive members and over 200 associate and affiliate members.

The PCMCIA card specification 2.01 is sold along with the card and socket services specifications and mass storage specifications for \$195. Also available are the JEIDA 88-pin DRAM card standard 1.0 (\$95); the PC Card '92 Showbook (\$195); and the PCMCIA Resources Reference Guide (\$12.50). Contact PCMCIA, 1030G East Duane Ave., Sunnyvale, CA 94086; 408/720-0107; fax 408/720-9416.

For information on Intel's ExCA specification, call 800/628-8686 (or 503/629-7354).

PCMCIA interface chips are offered by several vendors, including Databook, Intel, Cirrus Logic, and Vadem; we'll review this chips in a future article. In addition to interface chips, Databook (607/277-4817) provides system software and development support, including PCMCIA interfaces for desktop PCs.

AP Research provides a variety of PCMCIA-related market research services. Call them at 408/253-6567 for details, or fax to 408/253-5794.

There is even a free magazine devoted to memory cards: *Memory Card Systems and Design*, from Cardiff Publishing. Call 303/220-0600 or fax to 303/773-9716 for a subscription qualification card.

first tuple in the CIS be a device-information tuple describing common memory (a device-info tuple for attribute memory may follow). Each entry in this tuple consists of at least two bytes; the device type and speed fields may be extended with additional bytes if necessary. The WPS field indicates whether or not the writeprotect switch on the card controls writing into the devices described by the entry.

A device-information tuple will have as many entries as necessary to fully describe the card's addressable memory. As an example, a card might include common memory made up of 128K of 100-ns SRAM, followed by an 872K hole, followed by 1M of 150-ns flash memory. The device-information tuple in this case would have three, two-byte entries with fields set according to the tables in Figure 3 (the second tuple would specify a null device). In this case, no extension bytes would be needed. If the SRAM had an access time not in the table, an extended speed code byte would be required.

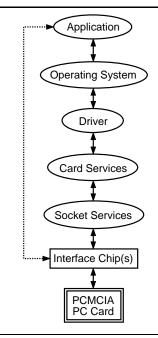

Figure 4. The software layers involved in a PCMCIA system.

## Software in the System

The information coded into the CIS is used by the system in a variety of ways. Some of the information is used to configure the timing and voltage characteristics of the system's card-interface hardware. Chip vendors are moving quickly to provide chip sets to implement the card-to-system interface. In the same way that a PC clone has a BIOS tailored to its PC chip set, a system with PCMCIA slots needs specific driver software to read device information from the CIS and configure its PC Card interface chips.

This low-level PCMCIA driver software is called *socket services* in PCMCIA-speak. BIOS vendors are already starting to offer socket services support to their customers.

At a higher level, it makes sense to present the system with a more structured view of PC Cards, especially memory cards, to allow generic device drivers and utility programs to work correctly with the cards. This layer of system software is called *card services* and, at a minimum, provides basic "read/write/copy/erase" functions.

Figure 4 shows how the layers of software fit together in a system. It is still possible, of course, to bypass this software hierarchy and talk directly to the interface chips to get to the devices on a card.

The ideal situation is for a system to implement card and socket services and for the card to carry its own drivers. Today, a couple of production systems have implemented partial card services, but no cards currently contain drivers. So, a system must either recognize a card specifically, the card must be supported

#### MICROPROCESSOR REPORT

generically, or the user must install and run some support software. Recognizing a card specifically can lead to higher performance by eliminating layers of software.

The idea of card and socket services came from Intel during its early work on ExCA. Intel contributed these layers to PCMCIA, and PCMCIA is now in charge of maintaining the definition of card and socket services.

Intel continued to develop its ExCA standard as a vendor-specific, x86 implementation of PCMCIA 2.01. ExCA is Intel's trademark and as such, ExCA hardware and software components are under Intel's control and use of the name can be policed.

To cash in on its ExCA definition, Intel has its own 82365 memory-mapped interface chip. Some companies, such as Vadem and Cirrus Logic, have register- and/or pin-compatible chips, while others, such as Databook, have chips that adhere to the ExCA hardware functional requirements while differing architecturally. Thus, it is possible for other companies to build ExCA-compatible hardware that is not identical at the register level. This is consistent with Intel's view of ExCA as a base level of capability upon which others can add value.

### **ROM-Based Application Code**

The PCMCIA standard defines a high-level card format for embedding executable code in PC Cards called Execute In Place (XIP). Depending on its type, an XIP partition is mapped into the system's address space using either linear addressing or the LIM (Lotus/Intel/-Microsoft) 4.0 memory mapping scheme, which uses a 16K address window. The layout of an XIP partition is modeled after the DOS FAT file system. The XIP specification includes an XIP application programming interface (API) to manipulate the XIP directory.

The major advantage of XIP is that it allows an application to be executed directly from the card; it is not necessary to load the application into system RAM. For some low-end systems, this will lower system cost by reducing the RAM requirements.

### **Evaluation and Conclusions**

The PCMCIA physical standards create exciting possibilities. The cards are pleasingly small yet the various thicknesses allow a wide range of devices, including rotating media, to be packed on a card. It is conceivable that two 1.3" disk drives could be packaged side-by-side on a single PC Card. Some manufacturers are even trying to fit drives into Type-II PC Cards.

One problem with rotating media is power consumption, especially the current drawn during motor startup. This is one of the strongest advantages of flash memory over disk drives. PCMCIA cards are appropriate for a wide variety of purposes beyond memory and I/O expansion in portable equipment. A PC-Card modem, for example, makes just as much sense for a desktop computer as it does for a portable computer. Currently, PC Cards carry a 20% to 100% price premium over equivalent ISA cards; as volume increases, the price difference should disappear. Since PC Cards should be cheaper and easier to use they have the significant advantage that peripherals can be installed by the end user without opening up the computer enclosure—they could become the preferred I/O expansion method for desktops.

Imagine copiers and fax machines with PCMCIA slots. Documents could be prepared on a computer and transferred to a PC Card. When travelling with a portable computer, it would be unnecessary to hassle with a fax modem or connecting to a network to gain access to a printer.

One problem with PCMCIA is that its bus structure is overly primitive. Because it evolved from a direct RAM interface, it lacks a clean set of bus timing signals. The 26bit address bus should be more than adequate for the majority of PC Card applications, but the 16-bit data bus width may limit the performance of applications that execute code directly from card memory. The standards committee could have easily used one of the many excellent existing buses to guide their design. For example, multiplexing address and data would have allowed the use of 32bit addresses and data and would have actually reduced pin count. While a drastic change in the bus definition would have rendered all existing PC Cards incompatible, the tiny size of the existing installed base hardly seems a compelling reason to stick with such a mediocre bus.

In addition to the effect PCMCIA will have on portable systems, the stage is now set for a revolution in the bus structures of desktop computers. Along with PCI or VL-Bus for high-speed peripherals, PCMCIA could eliminate the need for ISA, EISA, and MCA backplane buses.

Today, compatibility among PCMCIA cards and systems is a mess. To achieve its potential as the ultimate in ease-of-use for add-in cards, broad plug-and-play compatibility is essential. While today's products fall short of this goal, most of the necessary standards are in place and the software support continues to mature. As card services and ExCA implementations become widespread, compatibility should improve dramatically. Riding the wave of portable computing products, PCM-CIA is poised to become the most significant new expansion standard in the 1990s. ◆

A future article (see 070103.PDF) will delve into PCMCIA chips.