### Chapter 3 The K6 3D Microarchitecture

In this chapter, we will explore three main aspects of the microarchitecture of the K6 3D in more detail: its scheduler, its operation commit unit, and its register renaming scheme. As specific microarchitectural concepts are introduced, pseudo-RTL code is given for typical chunks of logic that could be used to implement these concepts.

### ROAD MAP OF CHAPTER 3

| Section                      | Audience                                          |

|------------------------------|---------------------------------------------------|

| All sections in this chapter | Practitioners, University Professors and Students |

| Chapter Summary              | All                                               |

### In Chapter 2 we showed that the scheduler:

- 1. is tightly coupled to the execution units.

- 2. is tightly coupled to the OCU.

- 3. maintains information concerning Ops in multiple execution pipelines.

- 4. issues Ops to the execution units for execution.

- 5. provides the Op information to the execution units at the times required.

- 6. does register and status flag dependency checking.

- 7. forwards results as required for the execution of dependent Ops.

- 8. holds the results from completed Ops until the results are committed or aborted.

- 9. deletes Op information as required.

### THE SCHEDULER: AN EXPANDED DESCRIPTION

In accomplishing this the scheduler can initiate, among other things:

- 1. four Op issues, to Load Unit, Store Unit, Register Unit X, and Register Unit Y.

- 2. nine register operand "fetches": two each for Load Unit, Registrant X, and Register Unit Y and three for the Store Unit, including immediate values for Register Unit X and Register Unit Y.

- 3. two displacement "fetches," for Load Unit and Store Unit.

- 4. outputs to nine register operand buses.

- 5. one status operand fetch, for Register Unit X.

- 6. BRCOND Op resolution and mispredicted branch handling.

- 7. LdOp and StOp ordering and relative age determination for pipeline Stage 2 LdOps and StOps.

We will now examine how all of this is done.

### LOADING THE SCHEDULER

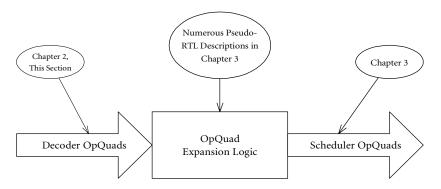

As OpQuads are loaded into the scheduler, they pass through the OpQuad Expansion Logic discussed in the "Decoder and Scheduler OpQuads" section in Chapter 2 and shown in Figure 2.8 on page 127. The OpQuad Expansion Logic expands the decoder OpQuads into scheduler OpQuads. Decoder OpQuads are 152 bits wide and scheduler OpQuads are 578 bits wide. Different types of processing occur during the expansion of decoder OpQuads:

- 1. a few Op fields are simply passed through unchanged.

- 2. some Op fields are modified based on the values contained in other fields.

- 3. some Op fields are replaced by physically different fields.

- 4. new fields are derived from existing ones.

As explained in the section titled "Execution Pipelines" beginning on page 158 and as shown in Figure 2.8 (cited above), Figure 2.6 on page 115 and Figure 2.10 on page 139, OpQuad Templates, fetched from the OpQuad ROM, are translated into decoder OpQuads in the environment substitution logic preceding the OpQuad Expansion Logic.

Whatever its source, the *scheduler* OpQuad formed by the OpQuad Expansion Logic is loaded into the scheduler whenever Row 0 (the top row) of the scheduler's buffer is empty or contains an OpQuad that is shifting to Row 1. If no scheduler OpQuad is available when the OpQuad in the top row shifts down, an *invalid* OpQuad is loaded into Row 0.

It might be useful at this point for you to review the scheduler diagram given in Figure 2.9 on page 130 and the three diagrams related to the decoder, i.e. Figure 2.6 on page 115, Figure 2.8 on page 127, and Figure 2.10 on page 139.

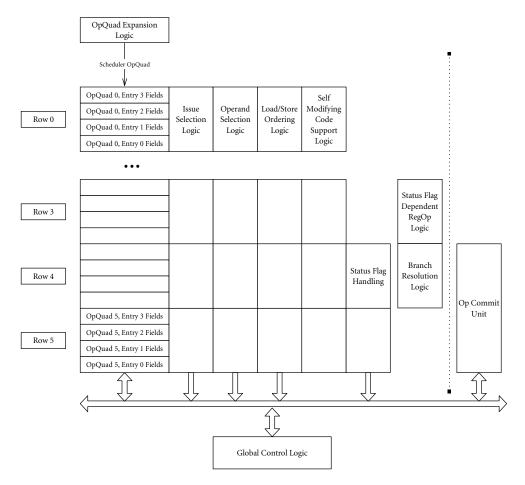

In Figure 2.9 on page 130, the scheduler's centralized buffer<sup>22</sup> is represented as consisting of six rows, each row having four entries—one entry for each Op in the scheduler OpQuad stored in that row. Each of these entries includes:

scheduler entry

static and dynamic fields

- 1. a number of static and dynamic fields, i.e., values stored in storage elements.

- 2. various portions of logic dedicated to specific scheduler functions—e.g., the *issue selection* logic, the *operand selection* logic, the *load/store ordering* logic, and the *self-modifying code support* logic.

The entries in Rows 3, 4, and 5 in Figure 2.9 also contain status flagdependent RegOp synchronization logic, branch resolution logic, and status flag fetch logic. All twenty-four Op entries are otherwise essentially identical.

Most of each entry's storage elements contain values of static fields. These fields are initialized when the Op is loaded into the scheduler and maintain their value until the Op is retired. Their contents can never change from their initial values. Other storage elements for an entry contain values of dynamic fields which can be reloaded with new values before the Op is retired.

Finally, other storage elements store values for fields, referred to as OpQuad fields that are associated with a scheduler OpQuad taken as a whole. Most OpQuad fields are static; however, some OpQuad fields are dynamic.

OpQuad fields

### **DEFINITION**

### Static Fields and Dynamic Fields

Some fields in an Op entry in the scheduler's buffer retain the same value throughout execution of the Op and are called static fields. Other fields can be changed as the Op proceeds through the scheduler and are called dynamic fields.

When taken on an OpQuad basis, the scheduler's storage elements can be thought of as forming a shift register that is six rows deep. Each clock cycle, an OpQuad that is not held up in a row shifts down to the next row if the next row is empty or contains an OpQuad that is also shifting downward. The OpQuad in the bottom row shifts out of the scheduler if all operations associated with the bottom row have been committed or aborted.

<sup>&</sup>lt;sup>22</sup> Instruction windows, reservation stations, and centralized buffers were introduced in the section titled "Superscalar Design" beginning on page 74.

### **Historical Comment and Suggested Readings**

### Early Environment Substitution Techniques

Designers of some early microprogrammable machines recognized that a number of microcode sequences used to emulate instruction set architectures were quite similar, differing, for example, only in the specific registers manipulated. To take advantage of this situation, the specific registers used in the microcode sequence were specified in auxiliary registers whose values were "merged" with the microcode sequence as it was being executed. Such implementations seem to be precursors to both OpQuad Template environment substitution and to the use of dynamic fields. See, for example, "Scheme-79—Lisp on a Chip," by Gerald Jay Sussman, Jack Holloway, Guy Lewis Steel, Jr., and Alan Bell, in *Computer*, July 1981, pp. 10-21.

The entries in the scheduler's buffer store information regarding the Ops that are awaiting execution, being executed, or have completed execution. How and when the information in the storage elements is modified is central to the operation of the scheduler. For example, the value of the State Field of an entry changes as an Op proceeds through the scheduler to indicate if the Op has been issued, is in a specific stage of execution, or has been completed.

### **Notation**

### OpQuad (without a modifier)

From now on the term "OpQuad" will be used without the modifier "decoder" or "scheduler," unless either is needed for clarity. It should be clear from the context if it refers to a decoder OpQuad or a scheduler OpQuad. In the current section, we are discussing scheduler OpQuads.

The scheduler issues Ops, provides Op information to the execution units at a specific time when required, holds the results from completed Ops until the results are committed or aborted, and forwards the results for the execution of other Ops as required. Each scheduler entry holds the register and status flags results from its associated Op. Each dynamic field storage element must be able to be loaded both from the appropriate preceding storage element and from a relevant data source. Further, the loading of data into a storage element and the shifting of the present or new data into a different storage element must be able to happen simultaneously (during the same cycle) and independently (from a control perspective).

### **DESIGN NOTE**

### Scheduler Entries Hold Register and Status Flags Results

Each scheduler entry holds the register and status flags results produced, if any, by the execution of its associated Op. This is a key element of the K6's implicit register renaming scheme discussed later in this chapter.

### SHIFTING OPFIELDS FROM ROW TO ROW

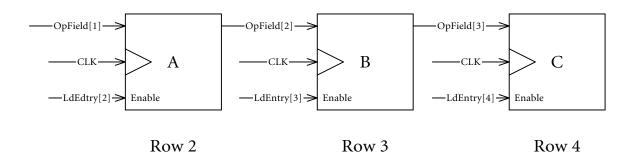

Figure 3.1 on page 187 shows portions of the scheduler's buffer that represent parts of an entry in Row 3 and its connection to Rows 2 and 4. Figure 3.1 shows a storage element for one of that entry's static fields while Figure 3.2 on page 191 shows a storage element for one of its dynamic fields. Both storage elements are edge-triggered flip-flops. Row 3 contains identical storage elements for every bit of each dynamic and static field for all four entries in Row 3 (i.e., the four Ops in Row 3). What this figure represents then is one of the four Ops (and the same Op) in each of the three rows. The other rows in the buffer are similar or identical to Row 3 and are connected in series with Row 3.

Let's look into this example in more detail. In Figure 3.1, flip-flops A, B, and C store one bit of the same static field in Rows 2, 3, and 4. This bit value shifts from flip-flop A to flip-flop B to flip-flop C as the OpQuad shifts from Row 2 to Row 3 to Row 4. The global control logic generates signals LdEntry[i], one for each row to control whether shifts to the corresponding rows occur or not. Thus, the LdEntry[i] signals can be thought of as the OpQuad shift control signals.

LdEntry[i] signals

Figure 3.1 Example of One Bit of a Static Field

The rows are shifted at the rising edge of the clock signal CLK. For example, a signal LdEntry[3] either enables or disables flip-flop B, and a

signal LdEntry[4] either enables or disables flip-flop C. When an OpQuad is held up in Row 4, signal LdEntry[4] is deasserted so that flip-flop C retains its value. The independence of signals LdEntry[i] allows filling of empty OpQuad entries above a held-up OpQuad. For example, even though an OpQuad is held up in Row 4, signal LdEntry[3] can be asserted so that a value OpField[2] from Row 2 shifts into Row 3 at the rising edge of clock signal CLK. Empty rows may result if the decoder is unable to provide an OpQuad every cycle—due to a branch target cache miss, for example. Empty rows are created only as a result of the decoder being unable to provide an OpQuad and by an abort cycle. Empty rows are never created by shifting lower OpQuads down while holding higher non-empty OpQuads in place since, in such cases, all the rows below the row being held will also be held from shifting.

### **NOTATION**

### OpQuadY, OpQY, and OpX

We will, from time to time, use the following notation to refer to *scheduler* OpQuads: OpQuadY, where Y = 0 to 5. For example, OpQuad1 identifies the OpQuad in Row1 of the scheduler, OpQuad2 the OpQuad in Row 2, etc. Additionally, we will use the following notation to refer to scheduler Op entries: OpX, where X = 0 to 23. For example, X = 0 identifies the youngest Op in the scheduler and X = 23 identifies the oldest Op in the scheduler. Thus OpQuad4, for example, contains Op16, Op17, Op18, and Op19. Moreover, the notation OpQuadY may be abbreviated OpQY in some contexts.

### PSEUDO-RTL DESCRIPTIONS

As was mentioned in Chapter 1 and reinforced in Chapter 2, in order to assist you in understanding exactly how the microarchitecture realizes some of its functions (as well as to encourage you to simulate various chunks of logic), we give pseudo-RTL descriptions of the operation of portions of circuitry implementing specific functions. We believe the pseudo-RTL descriptions are intuitive. The first such example will be an RTL description for the operation of the circuitry implementing the shifting of data from one static field storage element to another, as shown in Figure 3.1. Such descriptions played a very important part in the overall design and simulation of the microprocessor as described in Chapter 1. First, a word about notation.

### **Notation**

### Pseudo-RTL Descriptions

A pseudo-RTL description may use signals described in other pseudo-RTL descriptions without further explanation or reference to the other descriptions since such references should be reasonably obvious from the context. Signals given in the descriptions are asserted or active high unless expressly indicated otherwise. The following notation is used in the pseudo-RTL descriptions in this text:

Signals connected via a "P", " ", and "%" are combined as a logical AND such as could be implemented by an AND gate. Signals connected via a "+" are combined as a logical OR such as could be implemented by an OR gate. Signals connected via a "^" are combined as a logical exclusive OR such as could be implemented by an XOR gate. "~" indicates the complement or inverse of a signal such as would be provided by an inverter.

Either if (a) x = b else x = c or if x = (a) ?b:c indicate a multiplexer with an output signal x equal to signal b if signal a is asserted and an output signal x equal to c otherwise. If "else x = c" is omitted, the signal xis unaffected if signal a is low (i.e., signal a forces signal x to a value if and only if a is asserted, otherwise signal x maintains its value as determined thus far, by preceding assignments to x. Another notation which represents a multiplexer is:

x = switch (A) case A1: x1case A2: x2 . . . case An: an

where output signal x has values x1 or x2 or ... xn depending on the value of a multi-bit select signal A.

The notation "xxOp.yyy" refers to an input signal to the Op decoder indicating a value from a field yyy defined for an Op of type xxOp. For example, "RegOp.Src1" refers to bits in an operation at the same position as the Src1 field of a RegOp.

Most signals described change each clock cycle. The notation "@clk:" indicates a signal is latched into a register at an edge-of-signal clock for use in a subsequent clock cycle.

Finally, it should be clear that the logic described by the pseudo RTLdescriptions can be implemented in a variety of ways.

### **Suggested Readings**

### Digital and Integrated Circuit Design

For readers who have little or no background in electronic circuits, we recommend reading a copy of the small but very well done introduction to the subject by Niklaus Wirth, Digital Circuit Design for Computer Science Students, An Introductory Textbook, Springer-Verlag, 1995. Wirth, as many of the readers know, designed a number of popular programming languages, among them Pascal and Modula. In this book he uses an easy-to-understand hardware description language called Lola.

For electronic, electrical, and computer engineers who would like an introduction to the myriad of tools and techniques used in the design, manufacture, and test of integrated circuits, we recommend Peter R. Shepherd's book, *Integrated Circuit Design*, *Fabrication and Test*, McGraw-Hill, 1996.

### STATIC FIELD STORAGE ELEMENT SHIFTING OPERATION

The following pseudo-RTL description defines the operation of circuitry for the shifting of data from one static field storage element to another, as shown in Figure 3.1.

### PSEUDO-RTL DESCRIPTION

### Shifting Data from One Static Field Storage Element to Another

```

@clk: if (LdEntry[i])

// OpQuad shift control

OpField[i] = OpField[i-1]; // conditionally shift in preceding

// OpField Value

```

### DYNAMIC FIELD STORAGE ELEMENT OPERATION

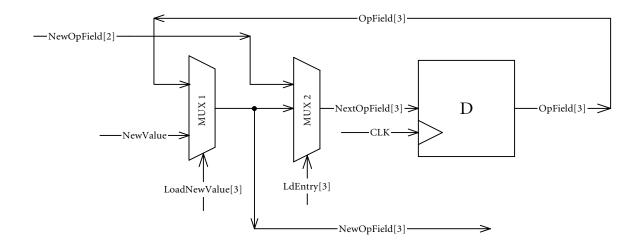

Dynamic fields, shown in Figure 3.2, are more complicated to handle than static fields because new data from outside the buffer may be inserted into a dynamic field while the OpQuad is being shifted or re-circulated.

Two independent events are happening here, so let's expand on them to clarify this last statement:

- 1. the value of a dynamic field may or may not take on a new value.

- 2. the OpQuad may or may not shift to the next row.

Row 3

Figure 3.2 Example of One Bit of a Dynamic Field

In the example discussed here and shown in Figure 3.2, the dynamic field is called OpField and its value is stored in flip-flop D. A chunk of logic outside the scheduler generates the NewValue<sup>23</sup> and LoadNewValue[3] signals. If a NewValue has been generated, the LoadNewValue[3] signal selects it as the output of the MUX 1 multiplexer, otherwise the old value of OpField[3] is selected as the output. Obviously, selecting the old value is equivalent to saying that the dynamic field did not change. The output of the MUX 1 multiplexer is called NewOpField[3]. The NewOpField[3] output could have been called *Potentially\_Changed\_Dynamic\_OpField*[3] to reflect more precisely what we just explained, but that would have been too unwieldy a name to be used in the figure.

The MUX 2 multiplexer selects whether or not the OpQuad shifts. If OpQuad[2] can shift from Row[2] to Row[3] and become OpQuad [3], then the LdEntry[3] signal selects the NewOpField[2] value from OpQuad[2] as the output of the MUX 2 multiplexer and the shift occurs at the rising edge of the clock signal CLK. Otherwise, the NewOpField[3] value is selected as the output and no shift occurs. The output of the MUX 2 multiplexer in Figure 3.2 is called NextOpField[3]. It could have been called *Potentially\_Shifted\_OpQuad*, to reflect more precisely what we just explained. The LdEntry[3] signal will be discussed shortly. First, it will

The signal NewValue can be a signal common to all twenty-four Op entries or may be specific to each Op.

be useful to summarize the actions that occur when a valid OpQuad either shifts or does not shift:

- 1. <u>the shift occurs</u>: This means that OpQuad[2] shifts from Row[2] to Row[3] and OpQuad[3] shifts from Row[3] to Row[4]. By definition, all of the static and dynamic fields of OpQuad [3] take on the values of those same fields from OpQuad[2]. And, all of the static and dynamic fields of OpQuad[4] take on the values of those same fields from OpQuad[3]. Note that the value of the dynamic field OpField[3] of OpQuad[3] is sent to Row 4, via the output of the MUX 1 multiplexer.<sup>24</sup>

- 2. the shift does not occur: This means that OpQuad[2] stays in Row[2] only if it is valid; if it is invalid, it will be replaced with whatever is in OpQuad[1]. OpQuad[3] stays in Row[3]. This in turn means that the output of the MUX 2 multiplexer is NewOpField[3] from OpQuad[3] and not NewOpField[2] from OpQuad[2].

In summary, MUX 1 is used to conditionally choose the NextOpField value and MUX 2 is used to conditionally advance the OpQuad through the buffer. The following pseudo-RTL description defines the operation of the circuitry implementing the operations associated with dynamic fields. It should be reasonably obvious how one could have written the following description, given Figure 3.2. However, the figure represents only one implementation strategy to realize the description.

```

PSEUDO-RTL DESCRIPTION

Dynamic Field Operation

if (LoadNewValue[i])

// logic to conditionally

NewOpField[i] = NewValue[i];

// select a value for the

else

// dynamic field

NewOpField[i] = OpField[i];

if (LdEntry[i])

// logic to conditionally

NextOpField[i] = NewOpField[i-1]; // advance the OpQuads

else

NextOpField[i] = NewOpField[i];

@clk: OpField[i] = NextOpField[i]

// simple flip-flop

```

The output of the MUX 1 multiplexer in Row[3] is an input to the MUX 2 multiplexer in Row[4].

Let's summarize what we have learned so far. The scheduler can be viewed as a shift register in which OpQuads are loaded into the top, gradually shift downward from row to row, and eventually unloaded from the bottom. However, the scheduler is not quite exactly controlled as a true shift register since each scheduler row has its own independent shift control signal, LdEntry[i]. We will now examine these signals in more detail.

### Simulators on CD-ROM

One way to test your understanding of the above concepts is to simulate the chunk of logic described by the previous two pseudo-RTL descruptions. To encourage you to do this, we have provided three simulators on the CD-ROM. Each has an extensive reference manual with it.

### THE LDENTRY SIGNALS: SHIFTING THE OPQUADS

The LdEntry[i] signals determine if the OpQuad in Row[i-1] shifts into Row[i]. In general, OpQuads always shift down whenever there is space below. That is, as long as there is at least one empty row below a given OpQuad, or the bottom row of the scheduler is being unloaded, then the OpQuad can shift down to the next row, the OpQuad above can shift down into the given OpQuad's row from above, and so on. However, situations can exist that prevent OpQuads from shifting. The situations that can hold up OpQuads basically fall into five categories:

- 1. OpQuads containing Ops that are dependent on status flags as part of their processing, i.e., BRCOND Ops and cc-dependent RegOps.

- 2. OpQuads that contain nonabortable RegOps.

- 3. OpQuads that are being considered for commitment by the OCU and contain one or more Ops that have not yet completed execution.

- 4. OpQuads containing multiple StOps in an OpQuad.<sup>25</sup>

- 5. OpQuads above the bottom row of the scheduler that cannot shift.

We will examine each of these categories separately:

1. <u>1st Category</u>: It was pointed out in the section titled "The Scheduler" beginning on page 128 that "... some Ops (such as the evaluation of conditional branches and RegOps that depend on status

More than one StOp in an OpQuad does not guarantee a hold up since, as we will see later, the OCU can look ahead into the second OpQuad row from the bottom to get a "head start" on committing StOps.

flags) are executed when the Ops reach a particular row of the buffer." Conditional branches, for example, are held in Row[3] until they are resolved and only then are they allowed to advance. If the branch is resolved as correctly predicted, processing proceeds normally. However, if the branch is resolved as mispredicted in Row[3], an appropriate restart signal is asserted that causes the upper portion of the machine to be flushed and then restarted to begin fetching instructions from the not-predicted path. The flushing of the upper portion is done as part of the resolution of the branch versus as part of the abort cycle since the abort cycle will be initiated later when the OpQuad reaches the bottom of the scheduler. If Ops are generated before the lower portion of the machine can accept them, then these Ops are held until they can be loaded into the scheduler. The BrAbort signal is asserted when the OpQuad containing a mispredicted branch reaches the bottom row of the scheduler. CC-dependent RegOps are also held in Row[3] until the necessary status flag operand value(s) are successfully obtained, and only then are they allowed to advance or shift down into lower rows.

- 2. <u>2nd Category</u>: There are four nonabortable RegOps, WRDR, WRDL, WRXXX, and WRDLP. Nonabortable RegOps that cannot yet proceed into the Execution Stage of the RegOp pipeline are held when they reach Row[4] until they can execute.

- 3. <u>3rd Category</u>: Because of the out-of-order execution nature of the processor, or due simply to execution latencies and serial dependencies between Ops, an Op might reach the bottom row of the scheduler before the other Ops associated with the OpQuad have completed execution. It must wait there while the other Ops are still executing.

- 4. <u>4th Category</u>: Consider a situation in which there are four StOps, two in each of two consecutive OpQuads. The first StOp will commit from OpQuad4, the second from OpQuad5 (the first OpQuad retires without delay), the third and fourth from OpQuad5 and thus shifting of the second OpQuad out of the scheduler is delayed for one cycle.

- 5. <u>5th Category:</u> There can be instances when OpQuads cannot shift because all rows below contain valid OpQuads and they are not able to shift. Conversely, an OpQuad is generally able to shift if there is an invalid OpQuad immediately below it or if all of the OpQuads below it are able to shift down.

The pseudo-RTL description that follows summarizes the equations determining which OpQuad can advance at the next clock cycle boundary. The code reflects the five categories discussed above as constraints on the

LdEntry signals that advance the OpQuads. While it may be apparent to some readers, what might not be obvious to others that there is the potential for some "deadlock" situations to occur. For example, you do not want to hold OpQuad[4] or OpQuad[5] if a branch has been detected as mispredicted or it will never reach the bottom row of the scheduler to initiate the abort cycle.

A few words about the notation for signals in the description are in order. The LdEntry[i], SC\_MisPred, BrAbort, and trap pending flag have all been introduced in the preceding paragraph. The Q4PendLdStAbort signal indicates that there is a LdOp or a StOp in OpQuad4 which has a pending exception waiting to be recognized by the OCU (once it gets into OpQuad[5]) and then cause an abort cycle. The OpQV[i], i = 0 to 5, signals represent the state of valid bit of OpQuad[i]. The OpQRetire signal originates from the OCU and, if asserted, indicates when a valid OpQuad in the bottom scheduler can be retired. The HoldOpQ45 signal, if asserted, holds up both OpQuad[4] and OpQuad[5]. HoldOpQ3 and HoldOpQ4A correspond to BRCOND resolution and cc-dependent RegOps, both of these situations are in Category 1 above. The HoldOpQ4B signals correspond to Category 2 above. Both Category 3 and Category 4 are handled via the OpRetire signal. Category 5 is handled via the OpV[i] signals.

The scheduler generates signals that indicate whether it will be able to accept a new OpQuad at the end of the current cycle. This is shown in the following pseudo-RTL description.

# Advancing OpQuads in the Scheduler HoldOpQ45 = (HoldOpQ3 | HoldOpQ4A | HoldOpQ4B) & ~(SC\_MisPred | Q4PendLdStAbort | "trap pending") LdEntry[5] = (OpQRetire | ~OpQV[5]) & ~HoldOpQ45 LdEntry[4] = (OpQRetire | ~OpQV[5] | ~OpQV[4]) & ~HoldOpQ45 LdEntry[3] = LdEntry[4] | ~OpQV[3] LdEntry[2] = LdEntry[4] | ~OpQV[3] | ~OpQV[2] LdEntry[1] = LdEntry[4] | ~OpQV[3] | ~OpQV[2] | ~OpQV[1] LdEntry[0] = LdEntry[4] | ~OpQV[3] | ~OpQV[2] | ~OpQV[1] | ~OpQV[0] | BrAbort

The signal "~LdEntry[0]" indicates that OpQuad[0] is full and not shifting and thus the scheduler does not have enough room to accept a new OpQuad. The signal "SC\_MisPred & ~BrAbort" indicates that there is a pending mispredicted branch and while the upper portion of the processor has been restarted and may have a new OpQuad ready, that the scheduler cannot accept it until the abort cycle is started.

```

PSEUDO-RTL DESCRIPTION

SchedFull and SchedEmpty Signals

SchedFull = ~LdEntry[0] | SC_MisPred & ~BrAbort

SchedEmpty = ~(OpQV[0] | OpQV[1] | OpQV[2] | OpQV[3] | OpQV[4] | OpQV[5])

```

We will now look at the static, dynamic, and OpQuad fields in more detail.

### STATIC AND DYNAMIC FIELDS

The static and dynamic fields in an entry are shown in Table 3.1 and Table 3.2 respectively. These fields are related to but not identical to the fields of the associated *decoder* OpQuad Op formats shown in Table 2.22, "Decoder OpQuad LdOp and StOp Format," Table 2.30, "Decoder OpQuad RegOp Format," Table 2.38, "Decoder OpQuad SpecOp Format," and Table 2.42, "Decoder OpQuad LIMM Op Format." Indeed, if we return to the following diagram given in Chapter 2, we see that the relationship between these fields is established by the OpQuad expansion logic:

The eleven static fields require a total of 45 bits per Op entry. The sixteen dynamic fields require a total of 65 bits per Op entry.

Table 3.1 STATIC FIELDS PER OP ENTRY

| Field Identifier | Bits/Entry |

|------------------|------------|

| Type[2:0]        | 3          |

| Imm              | 1          |

| Src1Reg[4:0]     | 5          |

| Src2Reg[4:0]     | 5          |

| DestReg[4:0]     | 5          |

| SrcStReg[4:0]    | 5          |

| Src1BM[1:0]      | 2          |

| Src2BM[1:0]      | 2          |

| Src12BM[2]       | 1          |

| SrcStBM[2:0]     | 3          |

| OpInfo[12:0]     | 13         |

Table 3.2 DYNAMIC FIELDS PER OP ENTRY

| FIELD IDENTIFIER   | Bits/Entry |

|--------------------|------------|

| State[3:0]         | 4          |

| ExecX              | 1          |

| DestBM[2:0]        | 3          |

| DestVal[31:0]      | 32         |

| StatMod[3:0]       | 4          |

| StatVal[7:0]       | 8          |

| OprndMatch LUsrc1  | 1          |

| OprndMatch LUsrc2  | 1          |

| OprndMatch SUsrc1  | 1          |

| OprndMatch SUsrc2  | 1          |

| OprndMatch SUsrcSt | 1          |

| OprndMatch RUXsrc1 | 1          |

| OprndMatch RUXsrc2 | 1          |

| OprndMatch RUYsrc1 | 1          |

| OprndMatch RUYsrc2 | 1          |

| DBN[3:0]           | 4          |

Additionally, the OpQuad fields, which are also stored in the buffer on a per OpQuad basis, are shown in Table 3.3. The thirteen OpQuad fields require a total of 138 bits.

Table 3.3 OPQUAD FIELDS PER OPQUAD

| Field Identifier | Static/Dynamic | Bits/OpQuad |

|------------------|----------------|-------------|

| Emcode           | static         | 1           |

| Eret             | static         | 1           |

| FaultPC[31:0]    | static         | 32          |

| BPTInfo[14:0]    | static         | 15          |

| RASPtr[2:0]      | static         | 3           |

| LimViol          | dynamic        | 1           |

| OpQV             | dynamic        | 1           |

| OpQFpOp          | static         | 1           |

| ILen0[2:0]       | static         | 3           |

| Smc1stAddr       | static         | 20          |

| Smc1stPg         | static         | 20          |

| SMC2ndAddr       | static         | 20          |

| Smc2ndPg         | static         | 20          |

Thus, a scheduler OpQuad requires a total of 45\*4 + 65\*4 + 180 = 578 bits.

The initial values of the static and dynamic fields depend on the corresponding Op loaded into that entry. As mentioned earlier, the OpQuad Expansion Logic modifies some fields from the Op based on other fields, derives new fields from existing ones, replaces some fields with physically different fields, and passes a few fields through unchanged. The OpQuad fields are generated from information corresponding to the OpQuad as a whole.

### AN OP ENTRY'S STATIC FIELDS IN MORE DETAIL

Each scheduler entry contains the following eleven static fields:

- 1. Type[2:0]

- 2. Imm

- 3. Src1Reg[4:0]

- 4. Src2Reg[4:0]

- 5. SrcStReg[4:0]

- 6. DestReg[4:0]

- 7. Src1BM[1:0]

- 8. Src2BM[1:0]

- 9. Src12BM[2]

- 10. SrcStBM[2:0]

- 11. OpInfo[12:0]

In the following discussion, all signals are actively high. Before proceeding, we make an additional comment about notation.

### **Notation**

### Decoder OpQuad Field Notation

There are many references to various decoder OpQuad fields in the pseudo-RTL description. We believe the notation identifying them, such as:

- 1. RegOp.Src1 (the Src1 field of the RegOp)

- 2. LdStOp.Data (the Op Data field of the LdOp or StOp)

- 3. SpecOp.Dest (the Op Dest field of the SpecOp)

- 4. LdOp.Type[1] (bit 1 of the Type field of the LdOp)

is quite intuitive if the reader examines the decoder OpQuad Op formats cited above.

### Static Field Type(2:0)

The static field Type[2:0] specifies the type of Op for the entry, particularly for issue selection purposes. Possible types include: a SpecOp; a LdOp; a StOp which references memory or generates a faultable address; a RegOp executable only by RUX; and a RegOp executable by either RUX or RUY. Floating-point operations (FpOps) are a type of SpecOp executed by the floating-point unit. This can be summarized in the following table:

Table 3.4 OP Type Specified by the Type Field

| Type(2:0) | Type of Op                                                                                      |  |  |

|-----------|-------------------------------------------------------------------------------------------------|--|--|

| 000       | a SpecOp—not issued to an execution unit                                                        |  |  |

| 010       | a LdOp—issued to the Load Unit                                                                  |  |  |

| 10x       | applies to all StOps                                                                            |  |  |

| 100       | a StOp that does not reference memory—issued to the Store Unit                                  |  |  |

| 101       | a StOp that references memory or at least can result in a memory fault—issued to the Store Unit |  |  |

| 110       | a RegOp that can only be executed by RUX—issued to RUX                                          |  |  |

| 111       | a RegOp that can be executed by RUX or RUY—issued to either RUX or to RUY                       |  |  |

The pseudo-RTL description that follows defines the chunk of circuitry in the OpQuad Expansion Logic that generates a value for the static field Type. In the equations in the description, fields in the *scheduler* OpQuad appear on the left-hand side of the equations and fields from the decoder OpQuad appear on the right-hand side. For example, in the description below the equation Type[2] = LdStOp.Type[3] means that bit three of the Type field of the *decoder* LdStOp is assigned to bit two of the static field Type of the scheduler Op entry. "RUYD" is a signal from a special register bit that inhibits use of the second register unit RUY for silicon debugging purposes; see Table 2.11 on page 88.

```

PSEUDO-RTL DESCRIPTION

Static Field Type

switch(OpId)

case RegOp:

Type[2:1] = 2'b11

Type[0] = \sim (RegOp.R1 \mid RUYD)

case LdStOp:

Type[2] = LdStOp.Type[3]

Type[1] = \sim LdStOp.Type[3]

Type[0] = LdStOp.Type[3] & \sim (LdStOp.Type[2] &

LdStOp.Type[1])

default:

Type[2:0] = 3'b000

```

### Static Field Imm

For RegOps, the static field Imm indicates that the Src2 operand is an immediate value (being temporarily held in the DestVal field of the Op entry) instead of a register. For LdStOps, the static field Imm is not used.

```

PSEUDO-RTL DESCRIPTION

Static Field Imm

Imm = RegOp.I

// don't care if not RegOp

```

### Static Fields Src1Reg(4:0), Src2Reg(4:0), & SrcStReg(4:0)

Some Ops can have up to two input values (obtained from registers). StOps, which actually write to memory, have a third input value, the data to be stored.

### Articles on CD-ROM

Chapter 3 of the AMD application note, AMD-K6 3D Processor Code Optimization, gives several examples of address register operands, data register operands, and store data register operands. This application note is on the CD-ROM.

Fields Src1Reg[4:0], Src2Reg[4:0], and SrcStReg[4:0] hold register numbers identifying the registers which an Op uses. Src1Reg[4:0] holds the register number of the first source operand Src1, Src2Reg[4:0] the register number of the second source operand Src2, and SrcStReg[4:0] the register number of the store data operand in the case of StOps. The following three pseudo-RTL descriptions define the circuitry in the OpQuad Expansion Logic that generates values for the static fields Src1Reg, Src2Reg, and Src-StReg:

```

PSEUDO-RTL DESCRIPTIONS

Static Fields Src1Reg, Src2Reg, and SrcStReg

// Field Src1Reg

if (OpId = RegOp)

Src1Reg[4:0] = RegOp.Src1

Src1Reg[2] &= ~(LdStOp.DSz=1B) // do byte register conversion

else

Src1Reg[4:0] = {1'b0,LdStOp.Base} // don't care if not RegOp or LdStOp

// Field Src2Reg

if (OpId = RegOp)

Src2Reg[4:0] = RegOp.Src2

Src2Reg[2] &= ~(LdStOp.DSz=1B) // do byte register conversion

else

Src2Reg = {1'b0,LdSt0p.Index} // don't care if not Reg0p or LdSt0p

// Field SrcStReg

SrcStReg[4:0] = LdStOp.Data

SrcStReg[2] &= ~(LdStOp.DSz=1B & LdStOp.DataReg=t0)

// don't care if not StOp

```

### Static Field DestReg(4:0)

Static Field DestReg[4:0] holds a register number identifying the destination register of the Op. The following pseudo-RTL description defines the circuitry in the OpQuad Expansion Logic that generates a value for the static field DestReg:

### Static Fields Src1BM(1:0), Src2BM(1:0), & Src12BM(2)

The x86 instruction can operate on individual bytes and 16-bit words as well as 32-bit double words and, correspondingly, can modify just parts of 32-bit registers. The K6 3D's microarchitecture reflects this ability. Static fields Src1BM[1:0], Src2BM[1:0], and Src12BM[2] specify the sizes and locations of the operands. The "BM" is used as an abbreviation for the phrase "byte marks" and these three fields indicate which bytes of operand registers Src1 and Src2 must be "valid" for execution of the Op that will use values from these registers—i.e., which fields in the source registers must have correct, up-to-date values in them so the Op can proceed.

Src12BM functions as both Src1BM[2] and Src2BM[2]. A "0" in Src12BM means that the high-order 16-bits of neither source register will be used. A "1" in Src12BM[2] specifies that the high-order 16-bits of *both* source registers will be used. That is, a "1" for a BM indicates that the corresponding register part *will* be used as it is presumed to be "valid." The Src!BM and Src2BM fields indicate if the byte positioned at bit [15:8] in the Src register or the byte positioned at bits [7:0] will be used if they contain a valid value. The byte positioned at [15:8] is specified by a "1" and the byte positioned at [7:0] is specified by a "0." Thus, bits 2, 1, and 0 of the SrcBM fields correspond to bits [31:16], [15:8], and [7:0] respectively. The following pseudo-RTL description defines the OpQuad Expansion Logic circuitry that generates values for the Src1BM[1:0], Src2BM[1:0], and Src12BM[2] fields.

### PSEUDO-RTL DESCRIPTIONS Static Fields Src1BM, Src2BM, and Src12BM if (OpId = RegOp) $Src1BM[0] = \sim (RegOp.DSz = 1B) \mid \sim RegOp.Src1[2]$ $Src1BM[1] = \sim (RegOp.DSz = 1B) \mid RegOp.Src1[2]$ $Src2BM[0] = \sim (RegOp.DSz = 1B) \mid \sim RegOp.Src2[2] \mid RegOp.I$ $Src2BM[1] = \sim (ReqOp.DSz = 1B) \mid ReqOp.Src2[2] \& \sim ReqOp.I$ if (RegOp.Type = 6'b10001x)Src2BM[1] = Src1BM[1] = 1'b0 // if ZEXT, SEXTSrc12BM[2] = (RegOp.DSz = 4B)if ((RegOp.Type = 6'b10001x) | (RegOp.Type = 6'b111x00))Src12BM[2] = 1'b0 // if ZEXT,SEXT,CHKS else// else LdStOp or don't care Src1BM[1:0] = Src2BM[1:0] = 2'b11Src12BM[2] = (LdStOp.ASz = 4B) // don't-care if LIMM SrcStBM[0] = ~(LdStOp.DSz=1B) | ~LdStOp.Data[2] SrcStBM[1] = ~(LdStOp.DSz=1B) | LdStOp.Data[2] SrcStBM[2] = (LdStOp.DSz=4B)SrcStBM[2..0] = 3'b000// CDA,CIA,LEA Ops// don't care if not StOp

### Static Field SrcStBM(2:0)

Static Field SrcStBM[2:0] indicates which bytes of the store data operand are required for completion of a StOp. The bit correspondence is the same as for Src1BM or Src2BM. The following pseudo-RTL description defines the circuitry in the OpQuad Expansion Logic that generates a value for the static field SrcStBM:

```

PSEUDO-RTL DESCRIPTION

Static Field SrcStBM

if (LdStOp.Type = 4'bx0xx) // STxxx Ops

SrcStBM[0] = ~(LdStOp.DSz = 1B) | ~LdStOp.Data[2]

SrcStBM[1] = ~(LdStOp.DSz = 1B) | LdStOp.Data[2]

SrcStBM[2] = (LdStOp.DSz = 4B)

SrcStBM[2:0] = 3'b000// CDA,CIA,LEA Ops

// don't care if not StOp

```

### Static Field OpInfo(12:0)

The static field OpInfo[12:0] holds additional information about the Op for either the execution units or the OCU depending on whether the operation is executable or not. OpInfo is the union of three possible field definitions, depending on whether the Op is a RegOp, a LdStOp, or a SpecOp:

for a RegOp, field OpInfo contains a concatenation of the following bits from the Op template: six bits from the Op Type field; four bits from the Op Ext field; the Op R1 field; and two bits indicating an effective data size DataSz for the operation.

| Table 3.5 | OPINFO | Data | FOR A | REGOP |

|-----------|--------|------|-------|-------|

|-----------|--------|------|-------|-------|

| Op Template | Description                                             |  |

|-------------|---------------------------------------------------------|--|

| Type[5:0]   | :0] copy of the original Op Type field                  |  |

| Ext[3:0]    | copy of the original Op Ext field                       |  |

| R1          | copy of the original Op R1 field                        |  |

| DataSz[1:0] | effective data size of the Op (one, two, or four bytes) |  |

2. for a LdStOp, field OpInfo contains a concatenation of the following bits from the Op template: four bits from the Op Type field; two bits from the Op ISF field; four bits from the Op Seg field; two bits indicating the effective data size DataSz for the operation; and a bit AddrSz indicating a 16-bit or a 32-bit effective address size for the address calculation.

Table 3.6 OPINFO DATA FOR A LDSTOP

| Op template | Description                                        |  |

|-------------|----------------------------------------------------|--|

| Type[3:0]   | copy of the original Op Type field                 |  |

| ISF[1:0]    | copy of the original Op ISF field                  |  |

| Seg[3:0]    | copy of the original Op Seg field                  |  |

| DataSz[1:0] | effective data size for the memory transfer        |  |

| AddrSz      | effective address size for the address calculation |  |

3. for a SpecOp, the OpInfo field contains a concatenation of the following bits from the Op template: four bits from the Op Type field and five bits from the Op CC field.

Table 3.7 OPINFO DATA FOR A SPECOP

| Op template Description |                                    |  |

|-------------------------|------------------------------------|--|

| Type[3:0]               | copy of the original Op Type field |  |

| CC[4:0]                 | copy of the original Op CC field   |  |

The following pseudo-RTL description defines the OpQuad Expansion Logic circuitry that generates a value for the OpInfo Static field:

```

PSEUDO-RTL DESCRIPTION

Static Field OpInfo

OpInfo[12] = Op[35]

// prevent LIMM from looking like various exception Ops

OpInfo[11:8] = (OpId = LIMMOp) ? 4'b1111 : Op[34:31]

OpInfo[7:0] = {Op[30:25], Op[23:22]}

```

### AN OP ENTRY'S DYNAMIC FIELDS IN MORE DETAIL

The entry's dynamic fields are initialized by the operation decoder but can then change during execution of Ops. Typically, each entry contains logic for changing the values in dynamic fields as required. Each scheduler entry contains the following eight dynamic fields:

- 1. State[3:0].

- 2. Exec1.

- 3. DestBM[2:0].

- 4. DestVal[31:0].

- 5. StatMod[3:0].

- 6. StatVal[7:0].

- 7. OprndMatch\_XXsrcY.

- 8. DBN[3:0].

These fields are discussed in the following paragraphs:

### Dynamic Field State (3:0)

The dynamic field State[3:0] indicates an operation's execution state with respect to the execution unit pipelines. In Figure 2.16 on page 165 and Figure 2.19 on page 168, the stages S2, S1, and S0 are alternate signal names for State[3:0]. The State[3:0] bits are updated as the Op is successfully issued or advances out of a pipeline stage. The updating can be viewed as shifting a field of ones across four bits.

Table 3.8 Interpretations of the State Field

| \$3 | <b>\$2</b> | \$1 | SO SO | Indicates the Op is       |

|-----|------------|-----|-------|---------------------------|

| 0   | 0          | 0   | 0     | unissued / not yet issued |

| 0   | 0          | 0   | 1     | in operand fetch stage    |

| 0   | 0          | 1   | 1     | in execution stage 1      |

| 0   | 1          | 1   | 1     | in execution stage 2      |

| 1   | 1          | 1   | 1     | completed                 |

Most Ops enter the scheduler with field State set to 0000 (unissued). The dynamic field State changes after the operation issues to an execution pipeline. Upon completion of the execution pipeline, State is set to 1111 (completed) while the Op awaits to be committed or retired. The state field of every scheduler entry is set to 1111 during abort cycles. Some Ops (e.g., load constant LDK or load 32-bit immediate LIMM) have an initial state field value of 1111 and thus are already completed when loaded into the scheduler. The following pseudo-RTL description defines the circuitry in the OpQuad Expansion Logic that initializes dynamic field State and the circuitry in the scheduler entries that modify field State during execution of the associated operation. Note that "OPQV" in the pseudo-RTL descriptions for the dynamic fields is the OpQuad Valid bit associated with the incoming decoder OpQuad and not the OpQV field of a scheduler OpQuad. The OpQuad Expansion Logic initializes field State[3:0] either as 0000 (unissued) or 1111 (completed) according to the OpId field. Signal SC\_Abort is asserted to abort execution of Ops currently in the scheduler. The signal "Issue Op[i] to XXX" are generated during the Op issue selection scan process; see the section titled "Issue Selection Logic" beginning on page 228.

### PSEUDO-RTL DESCRIPTION Dynamic Field State $State[3:0] = (\sim OpQV |$ (OpId = SpecOp) & ((SpecOp.Type = LDKxx) | (SpecOp.Type = LDxHA)) | (OpId = LIMMOp)) ? 4'b1111 : 4'b0000 Field State (signals S0, S1, S2, and S3) changes during operation execution as follows. if (SOEnbl) SO = ~BumpEntry | SC\_Abort if (S1Enbl) S1 = S0 & ~BumpEntry | SC\_Abort if (S2Enbl) S2 = S1 | SC\_Abort if (S3Enbl) S3 = S2 | S1 & RU | SC\_Abort BumpEntry = RU & ~S1 & S0 & (Exec1 & BumpRUX | ~Exec1 & BumpRUY) SOEnbl = "Issue Op[i] to " & CHP LUAdv0 | "Op[i] to SU " & CHP\_SUAdv0 "Issue Op[i] to RUX" & CHP\_RUXAdv0 | "Issue Op[i] to RUY" & CHP\_RUYAdv0 | SC\_Abort | BumpEntry S1Enbl = LU & CHP LUAdv0 | SU & CHP\_SUAdv0 RU & (Exec1 & CHP\_RUXAdv0 | ~Exec1 & CHP\_RUYAdv0) | SC\_Abort S2Enbl = LU & CHP\_LUAdv1 | SU & CHP\_SUAdv1 | SC\_Abort RU S3Enbl = LU & CHP\_LUAdv2 | SU & CHP\_SUAdv2 | RU | SC\_Abort

### Abort Handling (revisited)

The signal SC Abort in the above pseudo-RTL description warrants special attention. When an abort cycle occurs, the entire scheduler is flushed. All OpQuad entries are invalidated by clearing all of the OpQuad Valid fields (OpQV) and certain fields of all Op entries are also cleared to innocuous values. The latter is necessary since OpQV only affects the control of scheduler OpQuad entry loading and shifting. All other operations within the scheduler ignore OpQV and simply assume that Op entries are always valid and sufficiently well defined.

### **DESIGN NOTE**

### Representation of an Invalid Op

An invalid Op within the scheduler is represented as a valid but innocuous Op. Its State field is set to completed so the Op will not be executed. Its DestBM and StatMod fields are set to indicate that it does not modify any register bytes or status flags. All other fields, in these circumstances, can have any values without causing any "harm" (side effects). An invalid Op is effectively a NoOp.

One important aspect of abort cycle handling within the scheduler occurs after mispredicted BRCOND Ops. In this case, a new OpQuad may be loaded into the scheduler during the abort cycle. This OpQuad is not associated with any of the outstanding OpQuads that all need to be flushed. It is logically the first new OpQuad after the abort. In all other cases, there will be a delay to the reception of the first new OpQuad after abort cycles due to exception conditions.

As discussed in the section titled "Loading the Scheduler" beginning on page 184, in the section titled "Static Field Storage Element Shifting Operation" beginning on page 190 and the section titled "Dynamic Field Storage Element Operation" beginning on page 190, the storage elements within the scheduler are fully synchronous and do not change state in response to inputs until the next cycle boundary. Thus, the following sequence of events occur at the end of the abort cycle. First, certain Op entry fields are changed to innocuous values. Then all, some, or none of the OpQuad entries shift down one position and a new OpQuad is loaded into the top scheduler entry. The shifting of any OpQuads other than OpQuad[0] during an abort cycle is a "don't care" situation. In the case of exception-related aborts, this new OpQuad is also invalidated. In the case of BRCOND-related aborts, this new OpQuad is allowed to be valid and reloading of the top scheduler OpQuad entry is forced.

To improve the clock frequency, there is both an "early" and a "late" version of the abort signal. The late version is logically the same as the early version, but delayed by one cycle using a flip-flop. The late version is called SC\_Abort, and the early version is called SC\_EAbort. SC\_EAbort is used to flush the scheduler immediately; SC\_Abort is used to flush the execution pipelines—this is not performance critical since there will be at least two cycles after SC\_EAbort before an Op can possibly be ready to enter Stage 1 of a pipeline. The SC\_Abort signal was "split off" of SC\_EAbort to reduce the fanout/loading on a critical signal and to also make the longer distance usages non-timing critical. In short, this was done for timing improvement on a critical signal.

### Dynamic Field Exec 1

If the Op is a RegOp, the Exec1 field indicates that register unit RUX (versus RUY) is executing it. This field is set when the Op has successfully been issued to RUX or RUY. The OpQuad Expansion Logic initializes the Exec1 field to low (it is actually a "don't care" before the RegOp is issued). The following pseudo-RTL description defines the logic which sets and changes field Exec1. The signals "Issue Op[i] to RUX" are generated during the Op issue selection scan process; see the section titled "Issue Selection Logic" beginning on page 228.

### PSEUDO-RTL DESCRIPTION

Dynamic Field Exec1

if (SOEnbl) Exec1 = "Issue Op[i] to RUX"

### Dynamic Field DestBM(2:0)

The dynamic field DestBM[2:0] specifies which bytes of the register specified by the DestReg field are modified by the Op. DestBM[2], DestBM[1], and DestBM[0] correspond to bits [31:16], [15:8], and [7:0], respectively. The DestBM field is initialized by the operation decoder and may be cleared during an abort cycle. The logic associated with dynamic field DestBM is given in the following pseudo-RTL description. As in the case of the Src1/2BM fields, "BM" is used as an abbreviation for "byte marks." The equations shown are for integer results. There are similar 64-bit MDestVal fields (one per pair of Ops) for MMX/3D register results.

### Dynamic Field DestVal(31:0)

The dynamic field DestVal[31:0] holds the register result value which has resulted from execution of the Op and is to be committed to DestReg. DestBM indicates which bytes of the result value are valid after the execution of the Op. The DestVal field is loaded when the Op completes execution stage 1 or 2 (depending on the type of Op). For non-executed Ops (e.g., the load constant operation LDK), DestVal is initialized with the appropriate register result value. DestVal can be used for temporary storage before register results are stored when an Op is completed. DestVal initially holds immediate values for RegOps, displacement values for LdStOps, and the alternate (sequential or target) branch program counter (PC) value for a BRCOND Op.

### PSEUDO-RTL DESCRIPTION

```

Dynamic Field DestBM

Initialization by OpQuad Expansion Logic:

if (OpId=LIMMOp)

if (LIMMOp.DestReg = t0)

DestBM[2:0] = 3'b000

else

DestBM[2:0] = 3'b111

elseif (OpId=LdStOp LdStOp.Type = STUPD)

DestBM[1:0] = 2'b11

DestBM[2] = (LdStOp.ASz=4B)

else

DestBM[0] = ~(LdStOp.DSz=1B) | ~LdStOp.Data[2]

DestBM[1] = ~(LdStOp.DSz=1B) | LdStOp.Data[2]

DestBM[2] = (LdStOp.DSz=4B)

if (\sim OpQV \mid (DestReg[4:0] = 5'b01111) \mid // invalid or dest is t0

((OpId = LdStOp) & (LdStOp.Type = ST/STF))) // stores have no dest reg

DestBM = 3'b000

if (SC Abort)

DestBM = 3'b000

```

The DestVal field plays an important role in the K6's implicit renaming strategy. The OpQuad Expansion Logic circuitry used to initialize the DestVal field and the scheduler circuitry logic associated with dynamic field DestVal is given in the following pseudo-RTL description:

### PSEUDO-RTL DESCRIPTION Dynamic Field DestVal The OpQuad Expansion Logic generates the DestVal field according to the following logic: DestVal[31:0] = switch(OpId) case RegOp: sext(RegOp.Imm8) case LdStOp: sext(LdStOp.Disp8) case LIMMOp: {LIMMOp.ImmHi[16:0],LIMMOp.ImmLo[16:0]} case SpecOp: if (SpecOp.Type=BRCOND & ~DEC\_OpQSel\_E) DEC\_AltNextIPC[31:0] else sext(SpecOp.Imm17) Following execution of the Op, the DestVal field changes as follows: if ((~S2 | LU) & ~S3 & S1) DestVal[31:0] = switch (Type) case LU: DC\_DestRes case SU: SU1\_DestRes case (RU & Exec1): RUX\_DestRes case (RU & ~Exec1): RUY\_DestRes where signals DC\_DestRes, SU1\_DestRes, RUX\_DestRes, and RUY\_DestRes are the LU, SU, RUX, and RUY result buses, respectively.

### Dynamic Field StatMod(3:0)

Status flag bits EZF, ECF, OF, SF, AF, PF, and CF may be modified by RegOps. This field specifies which groups of status flags can be modified by the Op as shown in the following table:

Table 3.9 Status Flags Groups Specified by the StatMod Field

| StatMod<br>bit | Status Flags Groups that can be Modified by RegOps |

|----------------|----------------------------------------------------|

| 3              | {EZF, ECF}                                         |

| 2              | {OF}                                               |

| 1              | {SF, ZF, AF, PF}                                   |

| 0              | {CF}                                               |

EZF and ECF are separate "zero" and "carry" flags for use within OpQuad Sequences. When set, they are set in the same way as the architectural ZF and CF flags. The StatMod field is initialized to all zeroes for non-RegOp Ops and is cleared during abort cycles. The logic associated with dynamic field StatMod is given in the following pseudo-RTL description:

### PSEUDO-RTL DESCRIPTION

### Dynamic Field StatMod

Initialization by OpQuad Expansion Logic:

```

StatMod[3:0] = (~OpQV & (OpId=RegOp) & RegOp.SS) ? RegOp.Ext : 4'b0000

```

Logic in the scheduler clears field StatMod during an abort:

```

if (Exec1 & ~S3 & S1 & RUX_NoStatMod | SC_Abort)

StatMod[3:0] = 4'b0000

```

### Dynamic Field StatVal(7:0)

Like the StatMod field, the StatVal field is significant only for RegOps. The StatVal dynamic field stores the Op's status flag results value which are to be committed to status register EFLAGS. StatMod indicates which bits are valid after the RegOp completes execution stage 1. The StatVal[7:0] field is loaded when the RegOp completes execution stage 1. The logic associated with dynamic field StatVal is given in the following pseudo-RTL description. Note that there are no two-cycle RegOps that produce status flag results.

### PSEUDO-RTL DESCRIPTION

### Dynamic Field StatVal

Field StatVal is initially set to zero (i.e StatVal = 8'b00000000) and changes when a RegOp completes execution pipeline Stage 1.

```

if (~S3 & S1)

StatVal[7:0] = Exec1 ? RUX_StatRes[7:0] : RUY_StatRes[7:0]

```

### Dynamic Fields OprndMatch XXsrcY

This set of dynamic fields is associated with the control of transient information that is passed between two adjacent pipeline stages; see, for example, Figure 2.13 on page 160. In the notation, OprndMatch\_XXsrcY, XX is either the Load Unit, the Store Unit, RUX, or RUY, and Y is either 1 or 2. The logic associated with dynamic field OprndMatch\_XXsrcY is given in the following pseudo-RTL description:

### PSEUDO-RTL DESCRIPTION Dynamic Fields OprndMatch XXsrcY match with operand XXsrcY: OprndMatch\_XXsrcY =(busReg[4:0] = DestReg[4:0]) & (busBM[1] & DestBM[1] | busBM[0] & DestBM[1]) where XXsrcY takes on the values LUsrc1, LUsrc2, SUsrc1, SUsrc2, RUXsrc1, RUXsrc2, RUYsrc1, and RUYsrc2, and "bus" refers to OprndInfo\_XXsrcY. The byte mark checking does not include BM[2], as a simplification, since (BM[2] = 1'b1) implies (BM[1] & BM[0]); thus, if (bus.BM[2] = 1'b1), then a match

### Dynamic Field DBN(3:0)

The DBN[3:0] dynamic field holds four data breakpoint status bits Bn (for n = 0 to 3) for a LdStOp. This field is initially all zeroes. When the associated LdStOp executes, the breakpoint bits from the appropriate execution unit are recorded for later trapping. Field DBN is initialized to zero (DBN[3:0] = b0000). Scheduler circuitry changes it during execution as shown in the following pseudo-RTL description:

will be signaled irrespective of DestBM[2].

```

PSEUDO-RTL DESCRIPTION

Dynamic Field DBN

if ((AdvLU2 | AdvSU2) & ~S3 & S2)

DBN[3:0] = (DBN_LU[3:0] \& LU) | (DBN_SU[3:0] \& SU)

```

### THE OPQUAD FIELDS IN MORE DETAIL

In addition to the static and dynamic fields for each Op entry in a row, the scheduler contains fields that are associated with the OpQuad as a whole. Most of these OpQuad fields are static; however, some are dynamic. Logic in each row of the scheduler changes the dynamic OpQuad fields as required. We will now examine the OpQuad fields that were given in Table 3.3 on page 198 in more detail.

### OpQuad Field Emcode

The Emcode field indicates if the OpQuad was fetched from the OpQuad ROM or if it was generated from the hardware decoders. The scheduler logic associated with field Emcode field, which is a static field, is given in the following pseudo-RTL description:

```

PSEUDO-RTL DESCRIPTION

OpQuad Field Emcode

Emcode = DEC_OpQSel_E | DEC_Vec2Emc

// treat initial vectoring OpQuad as part of an

// OpQuad Sequence

```

### OpQuad Field Eret

The Eret field indicates the OpQuad was fetched from the OpQuad ROM and that it is marked as the last OpQuad in an OpQuad Sequence. The scheduler logic associated with the Eret field, which is a static field, is given in the following pseudo-RTL description:

```

PSEUDO-RTL DESCRIPTION

OpQuad Field Eret

Eret = DEC_OpQSel_E & EDR_Eret

```

### OpQuad Field FaultPC(31:0)

Field FaultPC[31:0] holds the logical x86 instruction fault program counter value associated with Ops in the OpQuad. In the case of a dual hardware decode, the FaultPC field holds the value of the PC associated with the first of the two instructions. The OCU uses the FaultPC field when handling fault exceptions for any of the Ops in the OpQuad. The logic associated with the FaultPC field, which is a static field, is given in the following pseudo-RTL description:

```

PSEUDO-RTL DESCRIPTION

OpQuad Field FaultPC

FaultPC = DEC_IPC // the logical PC for the first

// decoded x86 instruction in the

// OpQuad.

```

### OpQuad Field BPTInfo(14:0)

The BPTInfo[14:0] field holds branch prediction table-related information from when the OpQuad was generated. The BPTInfo field is defined only for OpQuads generated by the hardware decoders which contain a BRCOND Op; it is not defined for OpQuads fetched from the OpQuad ROM. The logic associated with field BPTInfo field, which is a static field, is given in the following pseudo-RTL description:

```

PSEUDO-RTL DESCRIPTION

OpQuad Field BPTInfo

BPTInfo = DEC BPTInfo

// information from the

// current BPT access.

```

### OpQuad Field RASPtr(2:0)

The RASPtr[2:0] field points to the top of the return address stack as of when the OpQuad was generated. The RASPtr field is defined for all Opquads but is significant only for OpQuads that contain a BRCOND Op. When a mispredicted BRCOND Op occurs, the RASPtr field is used to restore the decoder's top of Return Address Stack (RAS) pointer to its value as of the mispredicted branch. Note, the K6's RAS is used only for the implementation of x86 RET instructions. A separate one-deep return address stack is implemented in hardware to support one level of OpQuad Sequence subroutine nesting. The logic associated with the RASPtr field, which is a static field, is given in the following pseudo-RTL description:

```

PSEUDO-RTL DESCRIPTION

OpQuad Field RASPtr

RASPtr = DEC RASPtr

// the current return address stack pointer.

```

### **Historical Comment and Suggested Readings**

### Return Address Stacks in Microprogrammable Processors

Standard Computer Corporation's MLP-900 was among the early dynamically microprogrammable processors that supported return address stacks for microcode-level subroutines. The MLP-900 return address stack was also used in the processing of interrupts by automatically saving the return address before branching to the control store address where the class of interrupts to be serviced was located. Additionally, the MLP-900 supported a reasonably complete set of micro-operations that used the return address stack in relatively obvious ways, (e.g., branch and enter a subroutine, conditional branch or return, and branch and increment or decrement). See Harold W. Lawson, Jr's. and Burton K. Smith's article "Functional Characteristics of a Multi-Lingual Processor," in the *Preprints of the 3rd Annual Workshop on Microprogramming*, Buffalo, New York, October 12-13, 1970.

### OpQuad Field LimViol

The LimViol field indicates that the OpQuad contains the decode of a transfer of control instruction for which a code segment limit violation was detected on the target address. The LimViol field is actually loaded one cycle later than all of the other fields above (i.e., during the first cycle that the new OpQuad is resident and valid within the scheduler). For most rows, field LimViol is static; however, this field can be changed in the first row and therefore the field must be considered a dynamic field. The logic associated with the LimViol field is given in the following pseudo-RTL description. The LimViol field is initialized to zero (LimViol = 1'b0). The description reflects the fact that LimViol is loaded one cycle later:

# PSEUDO-RTL DESCRIPTION OpQuad Field LimViol LdLV = LdEntry[0] & ~DEC\_OpQSel\_E // a simple flip// flop if (LdLV) LimViol = DEC\_LimViol

### OpQuad Field OpQV

The OpQV field indicates whether the row contains a valid OpQuad. The OpQV field is used by the global control logic when shifting the OpQuads. Invalid OpQuads may be overwritten if an OpQuad lower in the scheduler is held up. The fields in a row containing an invalid OpQuad have the same values as an aborted OpQuad. An OpQuad can become invalid as a result of an abort.

The OpQuad Expansion Logic initially sets the OpQV field to indicate whether the OpQuad loaded into the top of the scheduler is valid. The logic associated with the OpQV field, which is a dynamic field, is given in the following pseudo-RTL description:

### **PSEUDO-RTL DESCRIPTION** OpQuad Field OpQV OpQV = (DEC\_OpQSel\_E ? EDR\_OpQV : DEC\_OpQV ) & ~ExcpAbort & ~(SC\_MisPred & ~BrAbort) Field OpQV can later be cleared after an abort to invalidate an OpQuad and prevent execution or commitment. if (SC\_Abort) OpQV = 1'b0

### OpQuad Field FPOP

The FPOP field indicates that the OpQuad contains a floating-point operation (an FpOP). The associated pseudo-RTL description is as follows:

```

PSEUDO-RTL DESCRIPTION

OpQuad Field FPOP

FPOP = DEC NPPopV

// indicates that Opquad contains

// a floating-point op

```

### OpQuad Field ILen0(2:0)

In the case of OpQuads produced from dual hardware decodes, the field ILen0 holds the length in bytes of the first of the two decoded x86 instructions. For all other OpQuads, this field is forced to indicate a zero length. The ILen0 field is used to calculate the proper instruction address for faults on the third or fourth Ops within an OpQuad (i.e, as FaultPC + ILen0). The logic associated with the ILen0 field, which is a static field, is given in the following pseudo-RTL description:

## PSEUDO-RTL DESCRIPTION OpQuad Field ILen0 ILen0 = DEC\_ILen0 // instruction length of first // short-decoded instruction

### OpQuad Fields Smc1stAddr, Smc1stPg, Smc2ndAddr, and Smc2ndPg

The fields Smc1stAddr, Smc1stPg, Smc2ndAddr, and Smc2ndPg hold the first and, if there are instructions from more than one cache line in the OpQuad, the second cache-line addresses covered by the instruction bytes of the instruction associated with the OpQuad. These fields are used in the detection of self-modifying code, which consists of writes to any of the bytes of the current instructions. The logic associated with the Smc1stAddr, Smc1stPg, Smc2ndAddr, and Smc2ndPg fields, which are static fields, is given in the following pseudo-RTL description:

```

PSEUDO-RTL DESCRIPTION

OpQuad Fields Smc1stAddr, Smc1stPg, Smc2ndAddr, & Smc2ndPg

Smc1stAddr[11:5] = DEC_Smc1stAddr[11:5] // page and address from first

Smc1stPg[24:12] = DEC_Smc1stPg[24:12] // cache line

Smc2ndAddr[11:5] = DEC_Smc2ndAddr[11:5] // page and address from second

Smc2ndPg[24:12] = DEC_Smc2ndPg[24:12] // cache line

```

### THE SCHEDULER PIPELINE

Physically the scheduler is a large storage structure, holding most of the fields of information describing the Ops that are outstanding in the machine at any point in time. This includes both (a) the static state derived from the original Ops as fetched from ROM or generated by the decoders, and (b) the dynamic state resulting from the processing of these Ops. From a control perspective, however, an alternative and perhaps better view of the scheduler is to view it as a pipelined datapath that generates various bits of control information related to the execution of the Ops through their respective execution unit processing pipelines.

The functioning of the scheduler pipeline and the generation of the appropriate control signals are based on the State field associated with each scheduler entry. As we saw in the section titled "Dynamic Field State[3:0]" beginning on page 205, the bits in an entry's State field reflect the progress of that Op through the appropriate execution unit pipeline.

All changes to the processor state are synchronous with the clock in a very strict manner, (i.e., all state changes effectively occur on the rising edge of the clock). This means, among other things, that processor state changes do not occur in the middle of a cycle and multiple changes to a given element of state do not occur within one cycle or, if they do, the one that occurs on the rising edge of the clock will take effect. In essence, the scheduler, at this level of abstraction, can be thought to be comprised of edge-triggered flip-flops for all storage elements that store processor state information.

The pipelined nature of the processing of Ops is reflected in the structure of the scheduler itself. The overall scheduler and, correspondingly, each Op entry can be divided into many distinct, independent portions (chunks) of logic, each of which is directly associated with a specific processing pipeline stage of a given type of Op or execution pipeline. Correspondingly, from the perspective of a particular processing pipeline, there is a chunk of scheduler logic associated with each pipeline stage that provides key control information for the processing done in that stage and/or for determining when that stage can successfully complete. From the perspective of a given pipeline stage, as viewed across all processing pipelines (at least for the first few common pipeline stages), there are n sets of similar chunks of logic that perform the same function for each pipeline or for each Op source operand of each pipeline.

# **Suggested Review**

It might be useful at this point for you to review several pipeline diagrams shown in Chapter 2 (Figure 2.12, Figure 2.14, Figure 2.15, Figure 2.18, and Figure 2.21) and the text that accompanies them as well as the scheduler diagram, Figure 2.9, and its related discussion.

Each Op goes through a multistage pipeline as it is processed and transitions between several states:

- 1. the first two pipeline stages are common to all Ops and represent Op Issue stage and Operand and Operand Transfer stage.

- 2. the last one or two stages are the actual execute stages.

For integer RegOps there is a single execute stage, corresponding to the fact that all RegOps execute in a single cycle. Further, once an integer RegOp enters this stage, it always successfully completes and exits this stage at the end of the cycle. Some MMX/3D RegOps take two cycles and some can be held up in execute Stage 1. For LdStOps there are two execute stages, during which address calculation, segment and page translation and protection checking, and D-Cache accessing (in the case of LdOps) all take place. Furthermore, LdStOps can be held up for arbitrary periods of time in either stage. Most reasons for holdups apply to the last stage, most notably D-Cache and D-TLB misses, and faults. Holdups in the first of the two execute stages stem typically from misaligned memory references<sup>26</sup> and the second execute stage being occupied and blocked, (i.e., not advancing).

The scheduler has limited involvement with the control of the execute stages of the processing pipelines; it simply keeps track of the state of each Op as it is executed and captures resultant register and status values as and when appropriate. Because of its usefulness at this point, Figure 2.9 is reprinted here:

REPRINTING OF FIGURE 2.9, THE SCHEDULER AND ITS CENTRALIZED BUFFER

Actually there are some miscellaneous additional cases that occur during cache and TLB fill which are not worth describing in any detail. The idea was to give you an example that already appeared in Chapter 2.

The various chunks of scheduler logic shown in this figure, namely the

- 1. issue selection logic

- 2. operand selection logic

- 3. load/store ordering logic

- 4. status flag handling logic

- 5. status flag dependent RegOp logic

- 6. branch resolution logic

- 7. self-modifying code support logic

- 8. global control logic

will be summarized and then discussed in more detail using this pipeline framework in the following sections. We will show how the information in the static and dynamic fields in the scheduler is used during the processing of instructions.

An inspection of Figure 2.12, Figure 2.14, Figure 2.15, and Figure 2.18 shows the scheduler processing in the first two common pipeline stages, where each stage consists of two phases. Each phase nominally occurs during the first and second halves of a cycle. These common stages are shown in Figure 3.3.

| Op Issue                    |                                              | Operand Fetch                 |                              |

|-----------------------------|----------------------------------------------|-------------------------------|------------------------------|

| Stage                       |                                              | Stage                         |                              |

| Issue<br>Selection<br>Phase | Operand<br>Information<br>Broadcast<br>Phase | Operand<br>Selection<br>Phase | Operand<br>Transfer<br>Phase |

Figure 3.3 Common Pipeline Stages for All RegOps, LdOps, AND STOPS

The Issue Selection Logic and the Operand Selection Logic shown in Figure 2.9 are directly related to the Op Issue Stage and the Operand Fetch Stage, respectively.

Recall that we introduced some textual abbreviations in Figure 2.16, Figure 2.19, and Figure 2.20 that help reduce the visual clutter of those already crowded figures. Using "S" to stand for stage and "C" to stand for commit, we introduced the notation  $S_i$  at the left hand side of Figure 2.16 and Figure 2.19 and the notation  $C_i$  in Figure 2.20. We then summarized these pipeline notational correspondences in Table 2.43. We now extend that table to reinforce the fact that neither Figure 2.16 nor Figure 2.19 show the Op Issue Stage.

Table 3.10 Addition of New Row to Table 2.43

| Figure 2.16<br>and Figure 2.19 | Figure 2.12, Figure 2.14<br>and Figure 2.18 |  |

|--------------------------------|---------------------------------------------|--|

| Not shown in either figure     | Op Issue Stage                              |  |

| SO                             | Operand Fetch Stage                         |  |

| S1                             | Execution Stage 1                           |  |

| S2                             | Execution Stage 2                           |  |

| С                              | Commit Stage                                |  |

The use of C1, C2, and C3 in Figure 2.20 reflects the fact that the overall Commit Stage for StOps is composed of several "stages." We will find this useful when discussing the operation of the Store Queue Commit and L1 D-Cache Access logic. The registers shown in Figure 2.16, Figure 2.19, and Figure 2.20 in between the pipeline stages (i.e., S0, S1, S2, C, C1, and C2) are the pipeline registers discussed earlier in this section.

### OP ISSUE STAGE LOGIC OVERVIEW

The Issue Selection Stage Logic supports the requirements of both the Op Issue Selection Phase and the Operand Information Broadcast Phase.

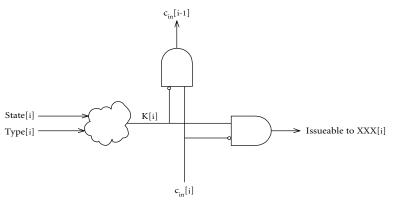

### Issue Selection Phase

During the Op Issue Selection Phase, the scheduler selects the next Ops to enter the LU, the SU, the RUX, and the RUY processing pipelines—(i.e., four Op selections occur). Each cycle, based on the updated State field of all the scheduler Op entries as of the beginning of the cycle, the scheduler performs a selection process to determine the next LdOp, StOp, and the next two RegOps to be issued into the corresponding execution unit processing pipelines. This will be discussed in detail later in this section.

# Operand Information Broadcast Phase

During the Operand Information Broadcast Phase of the cycle, information is broadcast to all scheduler entries and to external logic about each operand required by the Ops that were selected in the Op Issue Selection Phase. The Operand Information Broadcast Phase sets the scheduler up for actually locating where the appropriate operand values need to come from: (a) a scheduler Op entry, (b) the architectural register file, or (c) the results buses of the execution units (i.e., the *bypass* case). Since each of the four Ops may have up to two operands, a total of eight operand values might be involved. The store data operand for StOps represents a ninth register operand to be fetched, but this operand is not fetched until later in the SU pipeline, (i.e., at the latest possible moment before execution completion).

results buses

### **OPERAND FETCH STAGE LOGIC OVERVIEW**

The Operand Selection Logic supports the requirements of both the Operand Selection Phase and the Operand Transfer Phase.

# Operand Selection Phase

During the Operand Selection Phase, the scheduler determines:

- 1. where each of eight operand values actually needs to come from including which specific scheduler Op entry, architectural register, or execution unit result bus.

- 2. the status of each value, (i.e., whether a valid value is or is not available from the designated source).

Based on this information, the scheduler determines which of the current Stage0 Ops will be able to advance into Stage1 of their respective execution pipelines. This determination is made independently for each Op. Only explicit operand dependencies constrain the order with which Ops are actually executed. Different types of Ops are processed through their respective execution unit pipelines in arbitrary order with respect to other types of Ops after explicit operand dependencies are taken into account.

# Operand Transfer Phase

During the Operand Transfer Phase, eight operand values are transferred from the designated sources over the operand buses to the LU, SU, RUX, and RUY execution units. The transfers occur irrespective of whether the values are valid or not. If a value is invalid, then the value will not be used by the execution unit since the associated Op will not have advanced. Once an Op enters pipeline Stage1, the associated execution unit has latched its required operand values and will hold them as long as it remains in Stage1.

operand buses

### displacement buses