# Chapter 2 A Microarchitecture Case Study

e pointed out in Chapter 1 that the first half of this book presents a description of the microarchitecture of the AMD K6 3D microprocessor. In attempting to balance between giving you enough detail and too much detail, we will give a layered description of the microarchitecture. In this chapter we discuss the K6 3D's superscalar design and its multiple execution units, instruction buffers, predecode logic, multiple decoders, scheduler, branch resolution logic, operation commit unit, on-chip L1-Cache and L2-Cache, and other aspects of its microarchitecture. We follow this overview with detailed discussions of three of its main elements—its out-of-order, speculative scheduler, its operation commit unit, and its register renaming scheme in Chapter 3.

This chapter is written for all audiences (university professors and students, practitioners, and technical management). However, there are some subsections that have details that will be of more interest and use to practitioners and those in universities. The *road map* for this chapter identifies these sections.

#### ROAD MAP OF CHAPTER 2

| Section                                                                                                                                                                                                                                                                                                                                             | Audience                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| All major headings in the chapter                                                                                                                                                                                                                                                                                                                   | All                                               |

| The following more detailed subsections: Register Number and Name Mappings Special Registers and Model Specific Registers Formats for Decoder Ops LdOps and StOps perform memory accesses and related operations. They have the following format in a decoder OpQuad: RegOp Field Descriptions SpecOp Field Descriptions LIMM Op Field Descriptions | Practitioners, University Professors and Students |

## AN OVERVIEW OF THE K6 3D MICROPROCESSOR

In this section, we give an overview of how the K6 3D microprocessor works: how it fetches instructions and how they are predecoded and then decoded, how multiple internal operations result from this decoding process, how these operations go through a substantial expansion process before they are loaded into its centralized scheduler, how its pipelines are controlled and what type of work they do at each stage, how the decoding of instructions and the execution of the resulting operations are decoupled from one another, what types of caches the processor has on-chip and how they are organized, how operations are issued, and how and when predicted branches are ultimately resolved. The explanation of the particular design approaches taken within the K6 3D requires knowing a bit about the microarchitecture's internal operation set and the internal representation of operations within the scheduler, so some detail of both of these is also presented.

After completing this overview, you should be well positioned to understand the more detailed discussions of the scheduler, operation commit unit, and register renaming given in Chapter 3. Recall that our intent is to give you enough detail to allow you to simulate some important portions of the microarchitecture and associated platform and systems devices. You can gain a much greater understanding of how these chunks of the design actually work by doing such simulations. Such knowledge is basic to understanding the complex mix of cost and performance trade-off involved in taking the microarchitecture and producing a chip from it within a very aggressive time-to-market constraint.

#### A RANGE OF DESIGN APPROACHES

As stated in Chapter 1, one view of the K6 3D is that it is a high-performance CISC-on-RISC microprocessor. The CISC-component is the x86 instruction set architecture and the underlying RISC-component is known as the Enhanced RISC86 Microarchitecture. The most important technical implication of this constraint is that the K6 3D must be fully x86 binary code compatible, including the MMX multimedia extensions to the x86 instruction set architecture.

#### SUGGESTED READINGS

#### Complete Description of the x86 Instruction Set Architecture

For a complete description of the x86 instruction set architecture see the three-volume *The Intel Architecture Software Developer's Manual: Basic Architecture*, Intel Order Number 243190; *Instruction Set Reference*, Order Number 243191; and the *System Programming Guide*, Order Number 243192. These references also describe the x87 (floating-point) instruction set architecture and the MMX extensions.

The K6 3D also supports AMD-developed instruction set extensions to the MMX instructions, called the 3D instructions, which support high-performance 3D graphics, audio, and physics processing. The resulting microprocessor has a decoupled superscalar microarchitecture that uses many advanced design approaches targeted at achieving high performance. Some of the techniques that are employed in the K6 3D design are: instruction predecoding, multiple x86 instruction issue in a single clock cycle, internal single-clock RISC-like operations, superscalar operation (concurrent use of multiple execution units to execute up to six RISC-like operations per clock cycle), out-of-order execution, data forwarding, implicit register renaming, speculative execution, and the use of in-order retirement to ensure precise interrupts

Video Clips on CD-ROM

Greg Favor, Chief Architect of the K6 3D addresses the following two questions on two related video clips, "What were the principle design objectives chosen for the K6 3D microprocessor?" and "What are the key microarchitectural features incorporated into the K6 3D?"

The K6 3D uses a two-level, dynamic branch direction prediction technique that is integral to its ability to execute instructions speculatively. The branch direction prediction logic makes use of a branch history table, a branch target cache, and a return address stack, all of which combine to achieve a predicted address hit rate of better than 95%. These and other design techniques, such as employing a six-stage pipeline, enable the K6 processor to fetch, decode, issue, execute, complete, and retire multiple x86 instructions per clock. The material in this introduction provides a general overview of the K6 3D microprocessor and will be discussed in more detail in Chapter 3.

#### **DESIGN NOTE**

#### K6 3D Code Optimizations

The coding techniques for optimizing peak performance of the K6 3D include many of those recommended for optimizing the performance of the Intel Pentium and Pentium Pro microprocessors. They also include optimizations specific to the K6 3D's implementation of the MMX and 3D instruction set extensions. The use of the K6 3D code optimizations can result in higher delivered performance than off-the-shelf software non optimized code.

#### A FAMILY OF MICROPROCESSORS

The K6 is a family of microprocessors. The initial member of the family, called the K6 MMX, was introduced (in May 1997) at clock speeds of 166-MHz, 200-MHz, 233-MHz, and 266-MHz, had 8.8 million transistors and was designed in a 0.35-micron process resulting in a 162-mm<sup>2</sup> die-size. These chips have a 66-MHz processor bus. Shrinking to a 0.25-micron process and architectural and microarchitectural enhancements (e.g., the inclusion of the 3D instructions) grew the chip to 9.3-million transistors, yet the die size shrank to 81 mm<sup>2</sup>. This later member of the K6 family, called the K6 3D, supports the 3D instruction set extensions. The K6 3D, extended to have a 256-Mbyte L2-Cache on-chip, is called the K6 3D and it is this processor that is discussed in detail in this book. From time-totime reference will be made to the earlier versions of the K6 family that did not support the 3D instruction set or did not have the L2-Cache on-chip, but the references make clear when this is done. These processors will simply be referred to as the K6 and will be used to describe features that are applicable to both the K6 and the K6 3D.

The characteristics of some of the members of the K6 Family are summarized in the following table. Each family member extends the microprocessor in the row above it.

Table 2.1 K6 FAMILY MEMBERS

| Processor | Clock   | Bus     | Processa | Die-Size | TC <sup>b</sup> | Comments                                   |

|-----------|---------|---------|----------|----------|-----------------|--------------------------------------------|

|           | 166-MHz | 66-MHz  | 0.35     | 162-mm2  |                 | original release                           |

|           | 200-MHz | 66-MHz  | 0.35     | 162-mm2  |                 | higher clock                               |

| K6 MMX    | 233-MHz | 66-MHz  | 0.35     | 162-mm2  | 8.8             | higher clock                               |

|           | 266-MHz | 66-MHz  | 0.35     | 162-mm2  |                 | higher clock                               |

|           | 300-MHz | 66-MHz  | 0.25     | 68-mm2   |                 | K6 MMX shrink                              |

| K6 3D     | 300-MHz | 100-MHz | 0.25     | 81-mm2   | 9.3             | K6 with 3D <sup>c</sup> & MMX <sup>d</sup> |

| 1000      | 350-MHz | 100-MHz | 0.25     | 81-mm2   | 7.5             | higher clock                               |

| K6 3D     | 350-MHz | 100-MHz | 0.25     | 135-mm2  | 21.3            | K6 3D with L2-Cache on-chip                |

| KU 317    | 400-MHz | 100-MHz | 0.25     | 135-mm2  |                 | higher clock                               |

<sup>&</sup>lt;sup>a</sup> in microns

transistor count in millions

also called "AMD-3D Technology"

a superscalar dual-pipeline implementation of the x86 MMX instruction set extensions

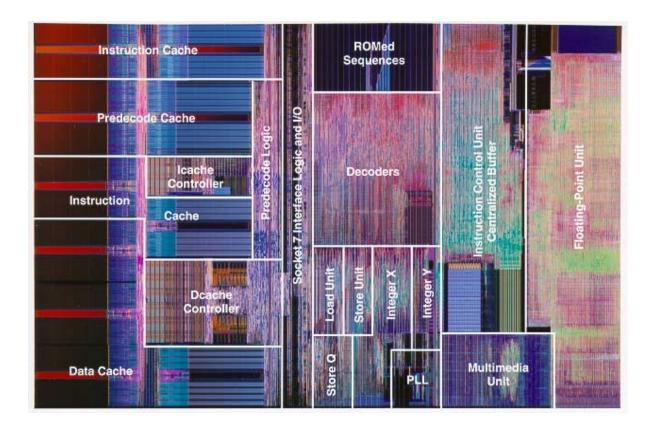

The K6 MMX was initially implemented in a 0.35-micron CMOS process and then in a 0.25-micron CMOS process, using five layers of metal, shallow trench isolation, and tungsten local interconnect. C4 solder bump flip-chip technology is used to assemble the die into a ceramic pin grid array (PGA). The high-performance and small die sizes of these microprocessors are achieved using high-speed custom and macro blocks and placed-and-routed blocks of standard cells. The initial 0.25-micron process version of the K6 MMX can operate at a clock speed of 300-MHz, has a 100-MHz processor bus and its chip sets support AGP (Advanced Graphics Port), USB (Universal Serial Bus), and the IEEE 1394 high-performance serial bus (a.k.a. Firewire), all of which are presented in detail in Chapter 5. A die photograph of a recent version of the K6 and an overlay on top of the photograph showing the approximate placement of various K6 components is given in Figure 2.1.

#### Technical Presentation on CD-ROM

A presentation by Greg Favor, Principal Architect of the K6 3D, on the evolution of the K6 family entitled, "*The AMD-K6 MMX Enhanced Processor Product Roadmap*," can be found on the CD-ROM.

#### Articles on CD-ROM

To learn more about some of the detailed implementation issues of an early version of the K6 3D processor, see "Circuit Techniques in a 266-MHz MMX-Enabled Processor," by Don Draper, Matt Crowley, John Holst, Greg Favor, Albrecht Schoy, Jeff Trull, Amos Ben-Meir, Rajesh Khanna, Dennie Wendell, Ravi Krishna, Joe Nolan, Dhiraj Mallick, Hamid Partovi, Mark Roberts, Mark Johnson, and Thomas Lee. This article, appeared in the November 1997 issue of the *IEEE Journal of Solid-State Circuits*. To learn more about some of the detailed implementation issues of the 0.35-micron version of the K6, see "An x86 Microprocessor with Multimedia Extensions," by Don Draper, Matthew P. Crowley, John Holst, Greg Favor, Albrecht Schoy, Amos Ben-Meir, Jeff Trull, Raj Khanna, Dennie Wendell, Ravi Krishna, Joe Nolan, Hamid Partovi, Mark Johnson, Tom Lee, Dhiraj Mallick, Gene Frydel, Anderson Vuong, Stanley Yu, Reading Maley, and Bruce Kaufmann 1997 *ISSCC Digest of Technical Papers*. You can find the full test versions of both of the above articles on the companion CD-ROM.

#### Microprocessor Fabrication Process Mini-Tutorial on CD-ROM

This video clip, in which Bill Siegle, AMD's Chief Scientist, addresses several questions related to the steps involved in the fabrication of contemporary microprocessor chips, effectively becomes a mini-tutorial on the fabrication process.

Figure 2.1 K6 Die Photograph and Overlay

#### K6 3D BLOCK DIAGRAM

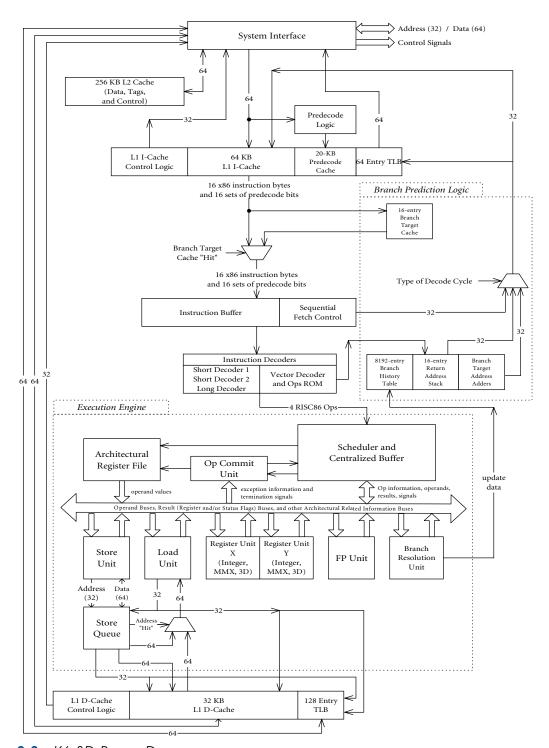

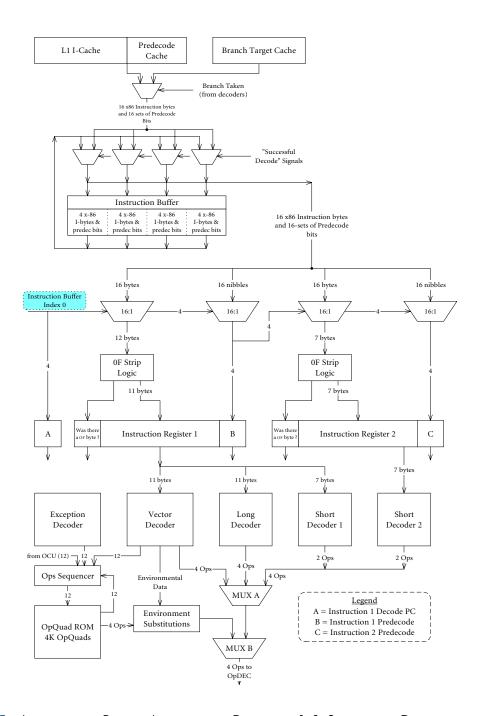

Figure 2.2 is a high-level block diagram of the K6 3D microarchitecture. We will give an overview of its operation first, followed by more detail about each of the elements shown in this figure.

Figure 2.2 K6 3D BLOCK DIAGRAM

We will, from time to time as appropriate, use the term *bus cycle* when referring to external data transfers and *processor cycle* when referring to operations internal to the microprocessor. There is typically a 3X ratio between these two cycles in the K6.

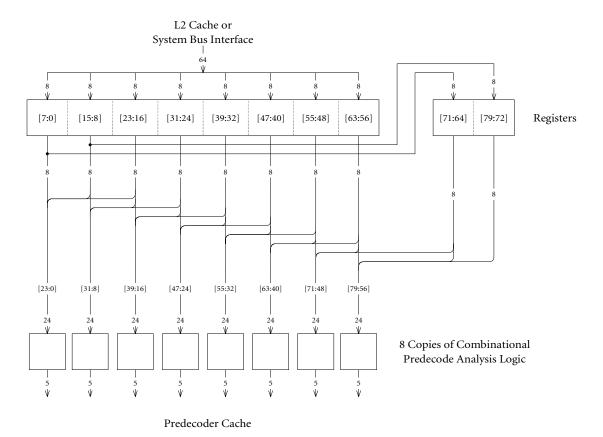

X86 instructions are stored in the main memory. During each bus cycle, up to eight bytes of x86 instructions are fetched from main memory or the on-chip L2-Cache and loaded into the on-chip *L1 Instruction Cache* (the *L1 I-Cache*) during a cache fill. While they are being loaded into the L1 I-Cache, the x86 instruction bytes are predecoded, using predecoded logic, to assist in later, rapid identification of x86 instruction boundaries.

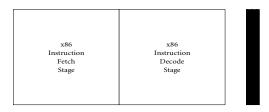

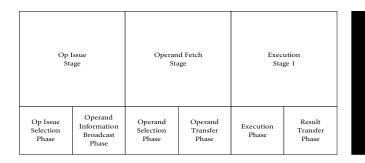

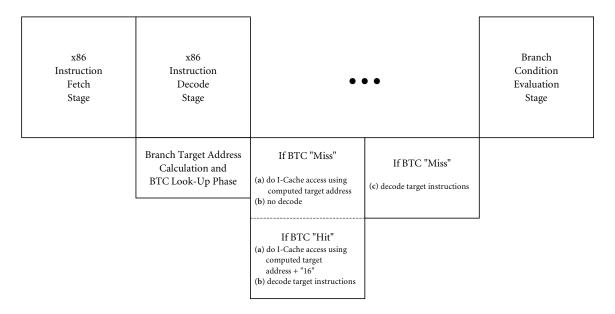

During each processor cycle, the L1 I-Cache or the Branch Target Cache (BTC) places 16 x86 instruction bytes into a 16-byte instruction buffer which directly feeds the instruction decoders. The multiple instruction decoders (two short decoders, a long decoder, and a vector decoder), taken as an aggregate, will be referred to as the decoders. The decoders, using a combination of the predecoded information and the x86 instruction bytes in the instruction buffer, produce and load four RISC-like operations, called *RISC86 operations*, into the scheduler of the execution engine. RISC86 operations are also called *RISC86 Ops*, *Ops*, or merely *operations*. Our usual term will be Ops. Each cycle, the decoders decode up to two x86 instructions to produce and load a set of up to four RISC86 operations into the scheduler.

#### HISTORICAL COMMENT

#### Peter Kogge's Insightful Book

The x86 instruction set architecture began with the Intel 4004 microprocessor, designed in 1969. Architectural innovations such as the use of pipelining, superscalar, speculative, and out-of-order execution were used in a number of mainframe computers at that time. Although these design techniques were not used in early generations of x86 microprocessors, recent members of the x86 family have employed all of them. See Peter M. Kogge's insightful book, *The Architecture of Pipelined Computers*, McGraw-Hill Book Company, 1981, for a detailed technical discussion and an interesting and reasonably complete history of the evolution of these design techniques in many important pre-microprocessor architectures that helped shape many of the current microarchitectural design approaches.

RISC86 Ops are RISC-like, fixed-format, internal Enhanced RISC86 microarchitecture instructions. Taken together, they form the "RISC86 operation set." Generally, all execute in a single clock cycle; register operations have a one-or two-cycle latency and load and store operations have a

two-cycle execution latency. RISC86 Ops can be combined, as required, into sequences of Ops to perform every function of the x86 instruction set.

#### **DESIGN NOTE**

#### Enhanced RISC86 Microarchitecture

The Enhanced RISC86 microarchitecture and its underlying RISC86 operation set are optimized for execution of the x86 instruction set architecture, while adhering to the architectural principles of fixed length encoding, regularized fields, and a large register set, common in most RISC architectures.

Some x86 instructions are decoded (translated) into as few as zero Ops (e.g., a RISC86 NoOp) or one Op (e.g., a RISC86 register-to-register add Op). More complex x86 instructions are decoded into several Ops. A more detailed treatment of the operation set is given later in this chapter and Chapter 3. There are six types of Ops:

Table 2.2 Types of RISC86 Ops

| Types of Ops                                                                     | Mnemonic                    |

|----------------------------------------------------------------------------------|-----------------------------|

| memory load operations                                                           | LdOps                       |

| memory store operations                                                          | StOps                       |

| integer register operations, MMX register operations, and 3D register operations | Integer, MMX, and 3D RegOps |

| floating-point register operations                                               | FpOps                       |

| branch condition evaluations                                                     | BrOps                       |

| special operations (such as load immediate constant into a register)             | SpecOps                     |

When a particular discussion is applicable to both LdOps and StOps, the terms LdStOp or LdStOps will be used, as appropriate. The following simple example gives a series of x86 instructions and corresponding decoded RISC86 Ops using the resources shown in Figure 2.2.

#### EXAMPLE CODE FRAGMENT

| x86 instruction | Type of Op  | Comment                                                                                                                                                                                                                                                                                                 |

|-----------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOV CX,[SP+4]   | LdOp        | The MOV instruction is decoded into a Load Op that requires data to be loaded from memory using the Load Unit.                                                                                                                                                                                          |

| ADD AX,BX       | RegOp       | The add instruction is decoded into an ALU Add Op that can be sent to either Register Unit X or Register Unit Y.                                                                                                                                                                                        |

| CMP CX,[AX]     | LdOp, RegOp | The CMP (compare) instruction is decoded into two Ops. A Load Op requiring data to be loaded from memory using the Load Unit followed by an ALU Sub Op that would be sent to either Register Unit X or Register Unit Y. Static flag values produced by the Sub Op reflect the result of the comparison. |

| JZ TA           | BrOp        | Conditional branch to "TA" (Target Address) based on Zflag = 1                                                                                                                                                                                                                                          |

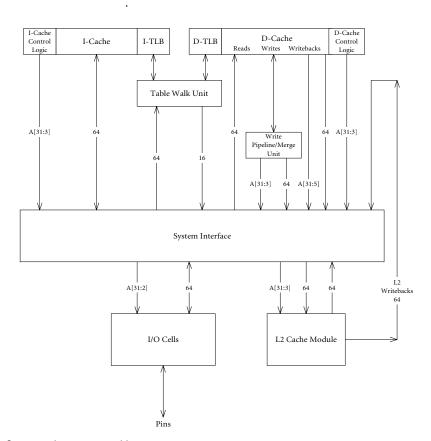

L1-CACHE, L2- CACHE. STORE QUEUE. AND SYSTEM INTERFACE

The execution engine interfaces to the on-chip 64-Kbyte L1-Cache. This cache is split into the 32-Kbyte L1 I-Cache mentioned earlier and a 32-KByte L1 Data Cache (L1 D-Cache). Split caches, such as these, are sometimes referred to as Harvard Architectures. One of the first references to this term can be found in Cragon, H. G., "The Elements of Single-Chip Microcomputer Architecture," Computer, Vol. 13, No. 10, October 1980, pp. 27-41.

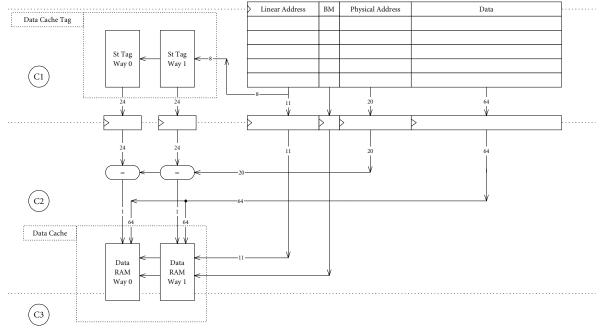

Both caches are 2-way set associative with a 64-byte line size and 32byte subblocking. There are 256 sets in each cache and each set contains two ways (or lines). Cache lines are fetched from main memory or the onchip Level-2 Cache (L2-Cache). using a burst bus transaction of four octets (or four quadwords in x86 terminology). Bus transactions are discussed in detail in Chapter 4.

The L2-Cache is a 256-Kbyte unified cache, is 4-way set associative, and has a 64-byte line-size with 32-byte subblocking. The L2-Cache employs a true LRU replacement algorithm. A store queue is used in conjunction with the L1 D-Cache. *Abortable* state changes are supported by the scheduler and the store queue through the general technique of temporarily storing (a) register and status results in the scheduler entries and (b) memory write data in store queue entries until the associated Ops are committed and retired.

#### **DEFINITIONS**

#### Abortable and Nonabortable

Abortable refers to changes that can be speculatively performed and later backed out of. Nonabortable changes cannot be backed out of once they are performed,

As will be seen in more detail later, the L1 I-Cache supports single cycle accesses. Both of the K6 3D's L1-Caches are interfaced through the system interface to the L2-Cache. The L1-Cache and L2-Cache are key to the scalability and performance of the K6 as the core frequencies increase.

#### HISTORICAL COMMENT AND DESIGN NOTES

#### Cache-Related Issues

In order to increase the access bandwidth, the L1 D-Cache is pipelined. It supports simultaneous loads and stores in a single clock. Bank conflicts are eliminated by performing loads first, followed by stores in a pipelined manner. Each access takes one clock cycle of time; the start of store accesses is offset by half a cycle from the start of load accesses.

Write performance is enhanced using a full write-back policy. Write-back caches are also called copy back, store in, nonstore through, or swapping caches in the literature. When data are written to a specific cache line, its "modified" (or "dirty") bit is set to indicate this. The cache line is actually stored in main memory only when the cache line is replaced. The intent is to reduce the overall traffic on the bus.

In contrast to the K6 3D, the K6 does not have an on-chip L2-Cache. The K6 has full support for an external (off-chip) L2-Cache, including a means for inhibiting the normal operation of its on-chip L1 I-Cache and L1 D-Cache (which are identical to the K6 3D's L1-Caches). This capability allows designers to disable the on-chip L1-Caches while testing the external L2-Cache. A complete description of the K6's L1-Caches and L2-Cache support can be found in the AMD-K6 MMX Processor Data Sheet which is on the companion CD-ROM. This also means that the system interface, shown in Figure 2.2 on page 69 and Figure 2.22 on page 180 for the K6 3D, is somewhat different for the K6.

Cache coherency is maintained using the MESI protocol. More will be said about the L1 and L2 caches later.

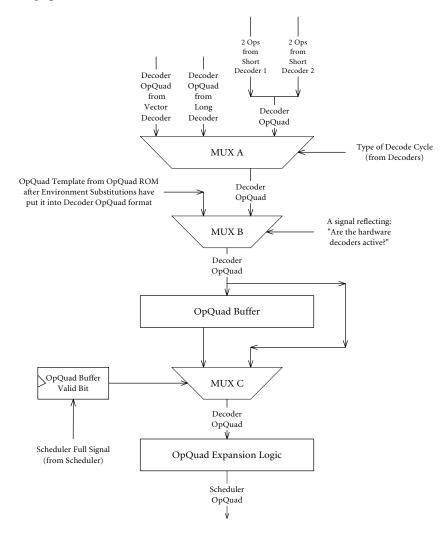

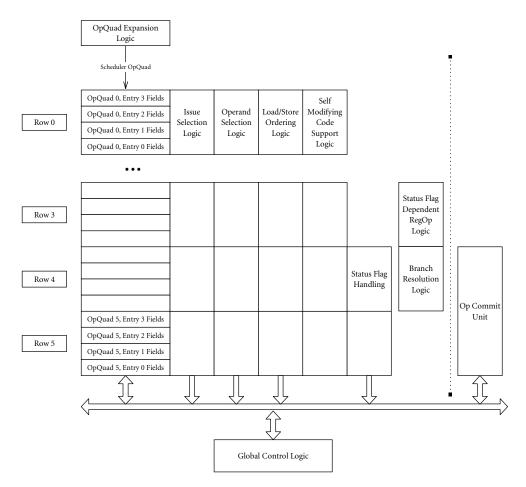

As mentioned earlier, during each processor cycle, the L1 I-Cache can place x86 instruction bytes into a 16-byte instruction buffer which directly feeds the decoders. The decoders produce and load four Ops into the scheduler's centralized buffer. The four Ops taken together are called an OpQuad. The scheduler is the heart of the K6 microarchitecture. It contains the logic necessary to manage out-of-order, speculative execution, data forwarding, implicit register renaming, and the simultaneous issue,

execution, and retirement of multiple Ops per cycle. The scheduler's centralized buffer can hold up to twenty-four Ops. This is equivalent to six to twelve x86 instructions. The scheduler will be discussed in substantial detail in this book because of its importance and unique design.

#### SUPERSCALAR DESIGN

Superscalar processors contain a number of execution units that can operate in parallel. The K6 3D is such a processor. It has six specialized execution units that can operate in parallel and are shown in Figure 2.2 on page 69: the Store Unit (SU), Load Unit (LU), Register Unit X (RUX), Register Unit Y (RUY), Floating-Point Unit (FPU), and the Branch Resolving Unit (BRU). As will be seen, RUX and RUY can execute integer, MMX, and 3D instructions.

The non-3D versions of the K6 actually have seven execution units. These microprocessors have a separate MMX unit that overlaps with the operation of RUX. More will be said later about the differences between the versions of the K6 that support the 3D instructions and those which do not, as appropriate throughout this book.

#### HISTORICAL COMMENT AND SUGGESTED READINGS

#### x86 Instruction Set Architecture MMX Extensions

Intel publicly released many details of its MMX extensions to the x86 instruction set architecture in March, 1996 in a rather extensive San Francisco news release, "Intel Releases MMX™ Technology Details to Software Community to Drive New Multimedia, Game, and Internet Applications." This news release can be found on the Developers' Insight CD-ROM, Intel Corp., April 1997, Reference SKU #273000, Intel Corporation, 5000 West Chandler Blvd. CH6-413, Chandler, AZ 85226. These extensions consist of new instructions and data types aimed at increasing the performance of x86 processors in multimedia applications. Implementations of the instructions can make use of SIMD (single-instruction stream, multipledata stream) techniques to process multiple 8, 16, or 32-bits in a 64-bit data path to achieve highly parallel performance in compute-intensive multimedia code. The instruction set extensions consist of 57 new instructions that support addition, subtraction, multiplication, multiply-accumulates, logical or arithmetic shifts, and several other operations that can be executed on all three sizes of data. See MMX<sup>TM</sup> Technology Technical Overview and the MMX™ Technology Developers' Guide, both which also are on the Developers' Insight CD-ROM cited above. Another source for related material is the Carole Dulong, David Bistry, Mickey Gutman and Mike Julier book, The Complete Guide to MMX Technology, McGraw-Hill, 1997.

> We would like to summarize some of the notations used so far. The following sets of terms, listed in alphabetical order for convenience, are used as synonyms in the text and the companion CD-ROM:

- 1. branch resolving unit and BRU.

- 2. decoders and instruction decoders.

- 3. instruction(s) and x86 instruction(s.)

- 4. K6 3D, K6, K6 microarchitecture, and RISC86® microarchitecture.

- 5. L1 I-Cache and L1 Instruction Cache.

- L1 D-Cache, L1 Data Cache, and L1 Dual-Ported Data Cache.

- operation(s), Ops, RISC86 operation(s), and RISC86 Op(s).

- 8. 3D Ops.

- Register Unit X and RUX.

- 10. Register Unit Y and RUY.

#### HISTORICAL COMMENT AND SUGGESTED READINGS

#### K6 3D Technology

K6 3D Technology consists of a set of extensions to the x86 instruction set architecture. Most of these new instructions can be viewed as being floating-point analogs of the MMX instructions discussed in the preceding "Historical Comment and Suggested Reading" inset. Whereas MMX instructions operate on packed sets of 8-bit, 16-bit, and 32-bit fixed point or integer values (within 64-bit wide MMX registers), the 3D instructions operate on packed pairs of 32-bit single-precision IEEE-compatible floating-point values (also within the same 64-bit wide MMX registers). In both cases these are "single instruction stream multiple data stream" or "SIMD" type instructions.

The 3D instruction set extensions were developed with the goal of greatly accelerating floating-point intensive computations, many of which contain substantial parallelism and thus an opportunity to benefit from SIMD floating-point instructions (in contrast to existing scalar x87 instructions within the x86 instruction set architecture). From an application software perspective, the goal was to greatly accelerate a range of multimedia algorithms, particularly in the area of 3D graphics and games. With the increasing use of 3D graphics, hardware accelerators are becoming more popular. These accelerators focus on backend graphics processing, i.e., the triangle/pixel rendering stages of the 3D graphics processing pipeline. Given this, the front-end stages of the graphics pipeline are becoming the performance bottleneck. These stages, which perform geometry transform, clipping, and lighting computations are all floatingpoint intensive and benefit substantially from the use of 3D instructions. In addition, as games and other multimedia applications evolve toward increasingly more accurate and physics-based modeling of 3D worlds and the interactions between objects in these worlds, the need for even greater levels of floatingpoint performance continues to grow. Ultimately it is expected that physics-based modeling and simulation computations will equal and surpass the traditional 3D graphics processing pipeline in the amount of floating-point computations and performance that is required. Other areas, such as audio and speech processing, and artificial intelligence/neural network algorithms, will also add to this.

An AMD application note describing the MMX extensions and related optimization, AMD-K6 MMX Enhanced x86 Code Optimization, can be found on the companion CD-ROM, as well as a application note related to K6 3D K6 3D optimizations, AMD-K6 3D Processor Code Optimization.

The decoders place four Ops in the scheduler's centralized buffer each cycle. The buffer's size, matched to the typical execution lifetime of Ops, allows the decoders to operate largely independently of the execution units. Such a buffer is often called an instruction window, which we formally define below.

The scheduler's issue logic examines the Ops in the buffer, selecting appropriate ones subject to dependencies and resource constraints. It is capable of issuing up to six Ops, out-of-order, each cycle, independently of the decoders. The execution engine can also execute them out-of-order, independently of the decoders. A microprocessor is said to have a decoupled decode/execution microarchitecture when the decode of instructions takes place independently of the issuing and execution of operations. Thus, the K6 is a decoupled decode/execution superscalar processor.

After completion, Ops are committed in-order by the Op Commit Unit (OCU), shown in Figure 2.2 on page 69. The scheduler effectively serves as a re-order buffer to ensure precise exceptions and x86 compatibility.

#### Historical Comment, Definition, and Suggested Readings

#### Instruction Windows and Reservation Stations

An instruction window allows a scheduler to optimize the execution of operations by issuing them to the appropriate execution units as the units are available and as various dependencies allow. There are two basic ways to implement instruction windows: centralized or distributed.

Distributed instruction windows, typically called *reservation stations*, are located with each functional unit. The reservation stations at the functional units can be (and often are) different in size from one another. Although their individual sizes are smaller, the aggregate size of the reservation stations is typically larger than the size of the single instruction window to achieve the same amount of instruction look ahead.

Centralized instruction windows provide the storage for both the operands and results of the functional units. The K6 scheduler buffer may be viewed as a type of centralized instruction window. More will be said about this later. Note that we have been using the terminology "x86 instruction" and "RISC86 operation." We will use this terminology consistently throughout this book. The K6's scheduler's buffer can be thought of as providing either an instruction window or an Op window since x86 instructions are decoded into RISC86 Ops. We will use the term *centralized buffer* or *buffer* when referring to the K6's Op window.

The first article that the authors are aware of that introduced the use of reservation stations was the insightful and seminal article by R. M. Tomasulo, "An Efficient Algorithm for Exploiting Multiple Arithmetic Units," IBM Journal of Research and Development, Vol. 11, January 1967, pp. 25-33. The full text version of this article is on the companion CD-ROM. Similarly, the first

article we are aware of which uses a form of centralized instruction window is James E. Thornton's article, "Parallel Operation in the Control Data 6600," Proc. AFIPS Fall Joint Computer Conference, Part. II, 1964, pp. 33-40, in which the scoreboard of the CDC 6000 is described.

As is seen later, we use the terms *retired*, *committed*, and *removed* in a particular way in this book. Retiring an operation does not imply the results of the operation are either permanent or non permanent. We will use the term *committed* to mean that the results of an operation have been made permanent and the operation retired from the scheduler. *Retiring* means removal from the scheduler with or without the commitment of operation results, whichever is appropriate. Timing-wise, commitment and retirement often happen simultaneously. We will use the term *removed* to mean the operation is retired from the scheduler without making permanent changes.

#### **DEFINITIONS**

### Decoupled Decode and Execution Decoupled Execution and Commitment

A microprocessor is said to have a decoupled decode/execution microarchitecture when the decode of instructions takes place independently of the issuing and execution of operations.

However, microprocessors that support out-of-order execution have an equally important decoupling. In such processors, results are often produced out-of-program-order as the various operations may issue out-of-order and may take different amounts of time to complete. The process of commitment (i.e., making permanent changes in the architecture's state) is decoupled from the execution of the operations. This allows the facility that commits the results to re-order them in program order. A microprocessor is said to have a decoupled execution/commitment microarchitecture when the execution of operations takes place independently of the commitment of the results of these operations.

As we mentioned when discussing the K6 3D block diagram, we said it has six specialized execution units that can operate in parallel: the Load Unit (LU), Store Unit (SU), Register Unit X (RUX), Register Unit Y (RUY), Floating-Point Unit (FPU), and the Branch Resolving Unit (BRU).

THE EXECUTION UNITS

The LU and the SU are pipelined execution units. Before summarizing their functionality, we need to review some aspects of x86 address calculations.

#### **x86 Address Calculations**

#### Physical, Virtual and Logical Addresses

The x86 instruction set architecture defines a word as two bytes or sixteen bits. A double word is four bytes or thirty-two bits. The phrase "double word" is often abbreviated as "dword." The x86 architecture treats physical memory as a linear array of bytes. Each byte has a unique address which is known as its *physical address*. Since the x86 instruction set architecture uses byte addressing, memory is organized and accessed as a sequence of bytes. No matter if one or more bytes are being accessed in the x86's address space, a byte address is used to locate the first byte of the set of bytes to be accessed.

Programs that execute on the x86 use a two-part address which is translated, or mapped, into physical addresses. The translation is done by an address translation mechanism and the two-part addresses are often called *virtual addresses* because these addresses do not correspond directly to a physical address, but correspond indirectly to one through the address translation mechanism. Virtual addresses are sometimes called *logical addresses*. The virtual-to-physical mapping mechanism also provides for both memory protection and the determination of a *valid* address (i.e., that an address is present in memory).

The two-part virtual address consists of a 16-bit segment selector and a 32-bit offset. The x86 employs a two-stage mapping mechanism to translate the two-part selector and offset virtual address into a physical address. The virtual address is first translated via a segmentation mapping mechanism into a 32-bit *linear address*. The linear address is then translated into a 32-bit *physical address* via a page mapping mechanism. Thus, the two well-known virtual memory mapping techniques—segmentation and paging—are used. For the specific segmentation and paging techniques defined for the x86 instruction set architecture, see "Programming the 80386," by John H. Crawford and Patrick P. Gelsinger, Sybex, 1987.

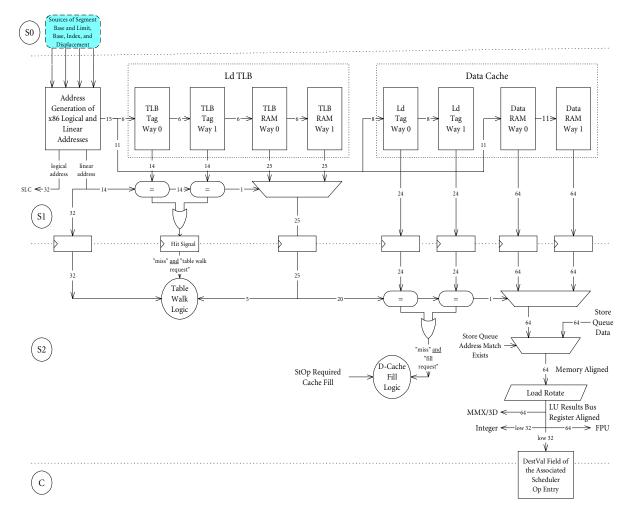

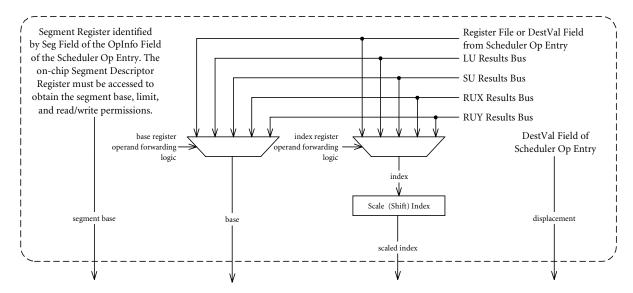

Given this brief background in the text inset, we can return our discussion of the LU. The LU performs data memory reads. When the LU unit receives its operand values, it first performs the general calculation,

base register + scaled index register + displacement yielding the x86 architecturally defined logical address, adds this to the segment base address to produce the architecturally defined linear address which is checked against the segment limit. The linear address is also translated to a physical address by the LU using the data translation lookaside buffer, i.e., data-TLB or D-TLB. The physical address is sent to the store queue and to L1 D-Cache in parallel. Typically data is received from the L1 D-Cache and, assuming a cache hit occurs, the data coming out of the L1 D-Cache is driven onto the LU's result bus. However, if the address matches a store queue entry then the store queue entry takes priority over a hit in the cache and data for the store queue entry is driven onto the LU's result bus. Both the L1 D-Cache and store queue "hit" analyses are based on the comparison of physical addresses received from the data-TLB, even though the D-Cache indexing is based on linear address bits.

We will see later that the LU is pipelined. The LU's pipelined design has the advantage of limiting the penalty for misaligned data loads to a latency of one cycle longer. In the x86 instruction set architecture, a misaligned access occurs either when an 8-byte (a quadword) access is made to an address that is not on an 8-byte boundary, or when a word or a double word access is made to an address that is not on a 4-byte boundary. Misaligned accesses are discussed in more detail later in this chapter, see "Faults, Traps, Abort Cycles, and the Pipelines" on page 168. Data are available from the LU after only two clocks or three clocks in the case of a misaligned access.

#### **DESIGN NOTE**

#### Linearly Indexed and Physically Tagged L1 Cache

Both the L1 I-Cache and the L1 D-Cache are linearly indexed and physically tagged. The L2 Cache is physically indexed and physically tagged. These concepts will be discussed later.

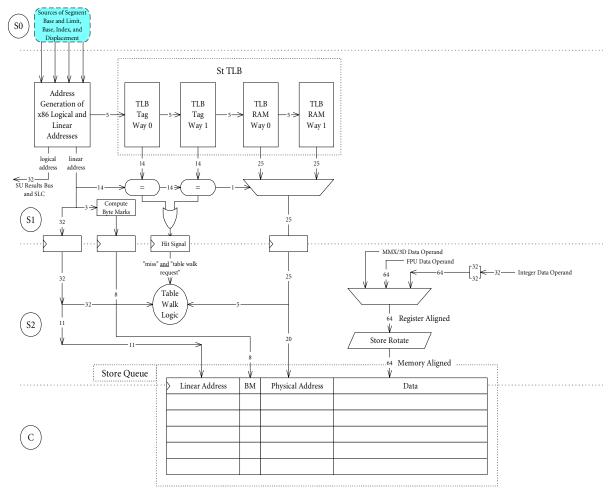

The SU performs address calculations for all store operations as well as for the load effective address and push operations. Logical and linear address calculations and translation to a physical address finish by fetching the memory write data from a register. Upon completion, the SU creates an entry in the store queue to hold the memory write address and data information. The store queue serves to buffer memory writes until they can be committed into the L1 D-Cache. Forwarding of write data from a store queue entry to dependent LdOps is supported. We will learn later that these entries are not valid until the very next cycle after the StOp execution completes. We will also learn the SU is also pipelined

#### **DESIGN NOTE**

#### Memory Aligned and Register Aligned Data

Data stored in the L1 D-Cache and store queue are memory aligned. This means that byte[0] of the 64-bit wide bus always carries bytes where the lower three bits are zero, so they are effectively memory byte addresses. However, data that ends up on the result bus must be register aligned. If a one-byte read is being done, the one valid byte must be on the low byte of the bus, if a two-byte read is being done, then two valid bytes must be on the lower two bytes of the bus, and so on. The K6 employs byte rotators to convert (or map) between these two alignments. See Figure 2.16 on page 165 and Figure 2.19 on page 168.

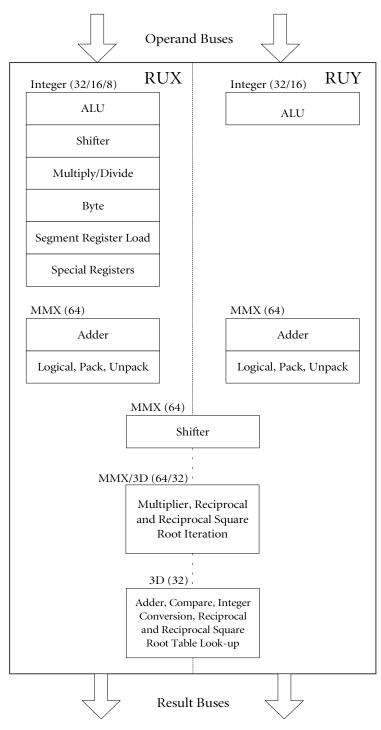

The RUX (Register Unit X) supports all integer ALU operations—multiplies, divides (signed and unsigned), shifts, and rotates. It can also perform MMX and 3D operations. The RUY (Register Unit Y) can operate on the basic word and double word integer ALU operations—ADD, AND, CMP, OR, SUB, XOR, zero-extend and sign-extend operations. It can also perform MMX and 3D operations. In fact, RUX and RUY share arithmetic resources to execute some of the MMX operations and all of the 3D operations. The relationship between RUX and RUY and the integer, MMX, and 3D operations that each register unit supports is shown in Figure 2.3. The K6 3D has two pipelines for executing integer, MMX, and 3D RegOps.

Generally speaking, RUX and RUY are symmetric pipelines. This means that any Op can issue to either pipeline. The one exception is that some of the integer Ops can only be executed by the RUX pipeline as shown in Figure 2.3.

Figure 2.3 RUX AND RUY EXECUTION UNITS

Leaving these Ops aside, the scheduler can issue an Op to either pipeline. Duplicate resources for an Op are either available or they are not available, (e.g., there are two integer ALUs and two MMX adders, but there is only one MMX multiplier). An Op that has duplicate resources available to it can proceed down either pipeline irrespective of what operations may be processing down the other pipeline. In particular, there can be two such Ops simultaneously in execution, one proceeding down each of the two pipelines. Ops that have only one copy of the execution logic available can proceed down the appropriate pipeline. Two such Ops can proceed down both pipelines but cannot start to execute simultaneously which means that one of the OPs incurs a one-cycle *pipeline stall*.

3D instructions can be considered to be a floating-point analog of the integer MMX instructions. Their primary purpose is to provide high-performance floating-point vector operations to enhance performance on 3D graphics-oriented applications. The 3D instructions that operate in a vector fashion operate on two sets of 32-bit single-precision floating-point numbers in parallel. The FPU, in contrast, operates internally on a single pair of floating-point numbers that have an 80-bit representation in accordance with the IEEE floating-point standard (see IEEE Standard for Binary Floating-Point Arithmetic, ANSI/IEEE Standard No. 754, 1988). The 3D floating-point operations are realized in RUX and RUY. All non-3D floating-point operations are executed in the FPU. More will be said shortly about the last of the six execution units, the BRU (Branch Resolving Unit), and the branch direction prediction logic which are shown in Figure 2.3 on page 81.

#### **Historical Comment and Suggested Readings**

#### The K6 Floating-Point Unit

The FPU, in all members of the K6 family of microprocessors, is a direct descendant of the FPU-core that appeared in the NexGen Nx586 microprocessors, which was designed to be instruction set architecture compatible with the Intel x87 floating-point unit. (The x87 instruction set architecture is the instruction set architecture of the x87 floating-point unit.) Thus the K6 family of microprocessors uses some concepts native to the Nx586, such as tags (see the Nx586 Databook cited below). There are a number of important design implications that arise from the decision to use this core. For example, the FPU operates out of its own register file with its own rename registers. The x87 has two 80-bit operands coming in and one 80-bit result coming out in addition to architecturally defined floating-point flag bits that reside in the architecturally defined floating-point status word register. Further, floating-point operations may also modify an architecturally defined top-of-stack pointer field. See *Nx586 Processor Databook*, NexGen Inc., Preliminary, December 6, 1994, Order # NxDOC-DB001-03-W.

#### **LATENCIES**

A brief word about *latencies*. In the K6 3D, register operations fall into one of three categories: those that have a latency of one cycle, those that have a latency of two cycles, and those (like divide) that have a latency of more than two cycles. In general, all integer operations and all of the non multiply MMX instructions have a single cycle latency. MMX multiply operations have a two-cycle latency. All of the 3D operations have a two-cycle latency. Subject to dependencies and execution resource contention, two RegOps can start execution each clock regardless of whether they are onecycle and/or two-cycle operations. For example, a 3D multiply and a 3D add can begin execution each clock cycle. At most one two-cycle latency Op, for which there are not duplicated execution resources (such as an MMX multiply), can be initiated in each cycle. One of the Ops of a pair of Ops wanting to start execution must be delayed if the Ops use a shared execution resource. This results in a delay of one cycle. Back-to-back twocycle latency Ops that use different execution resources (such as an MMX multiply and a 3D add) can be initiated in the same cycle, one in the RUX pipeline and one in the RUY pipeline. It is important to know instruction latencies when examining instruction dependencies.

Example Code Fragments on CD-ROM

The following two application notes on the CD-ROM contain a number of examples of the timings and latencies of the execution behavior of several code fragments as a function of decode constraints, dependencies, and resource constraints, "AMD-K6 3D Processor Code Optimization," and "AMD-K6 MMX Enhanced Processor x86 Code Optimization."

The details of the inputs and outputs of RUX and RUY on the operand and result buses in Figure 2.3, as well as the inputs and outputs for each of the execution units shown in Figure 2.2 on page 69, will be discussed in later sections of this chapter. Briefly, for example, RUX and RUY take their inputs from the register operand buses, execute the required Ops producing register and status flag result values, and drive them out onto the corresponding register result and status flag buses. It is up to the scheduler to keep track of which result and status flag values are scheduled (or marked) to actually be modified.

#### STATUS FLAGS, FAULTS, TRAPS, INTERRUPTS, AND ABORT CYCLES

The x86 instruction set architecture supports a register called the EFLAGS register that contains a number of x86 status and control flags (see for

example, Intel's publication, the Intel Architecture Software Developer's Manual, Volume 3: System programming Guide for a complete listing of all x86 status and control flags, exceptions, and interrupts). The values of these flags are used to control various functions in the processor. The x86 instruction set architecture defines a set of arithmetic status flags and a set of processor control flags. The x86 instruction set architecture also defines and supports exceptions and interrupts, both of which typically result in a transfer of control outside of the currently executing instruction stream. X86 exceptions occur when an unusual or invalid situation is detected during the execution of an instruction. There are two types of x86 exceptions defined, x86 faults and x86 traps. The difference between x86 faults and x86 traps is that an instruction is either aborted (x86 fault) or completed (x86 trap) before the processing of the exception. An interrupt is defined by the x86 instruction set architecture as an event external to the processor. Therefore, interrupts occur asynchronously to the execution of instructions within the processor; i.e., an interrupt has no relation to the specific instruction executing when the interrupt is recognized. X86 exceptions and interrupts are handled at instruction boundaries; that is "in between" two instructions versus within an instruction. Some x86 exceptions and x86 interrupts are given in the following table:

Sample of x86 Fault and Trap Exceptions

| x86 Exception Name     | Туре  |

|------------------------|-------|

| Divide Error           | Fault |

| Instruction Breakpoint | Fault |

| Data Breakpoint        | Trap  |

| Segment Not Present    | Fault |

| Page Fault             | Fault |

| General Protection     | Fault |

In particular, note that the x86 instruction set architecture treats an instruction breakpoint as a fault and a data breakpoint as a trap.

It is important to know which execution units can set status flags, which can cause exceptions or traps, and how status flags, faults, traps, and interrupts are treated. We will always use the preface "x86" to identify an architectural status flag, fault, trap, or interrupt, such as an "x86 trap." Without this modifier, these terms will always be referring to the K63D microarchitecture. Furthermore, we typically will not use the word "exception" but rather use "fault" or "trap" or both, as appropriate. All x86 faults, x86 traps, and x86 interrupts are ultimately handled by microarchitectural

fault and trap handling mechanisms. Interrupts will be discussed later in this chapter.

Only integer RegOps can produce status flag values. At the microarchitecture level, the K6 3D has eight status flags—the six x86 instruction set architecture visible flags and two flags for use within sequences of Ops used in the implementation of complex instructions. All integer RegOps that have a defined behavior for status flags also have the option of modifying the status flags.

A fault or trap at the microarchitectural level causes an abort cycle that then leads to the execution of a sequence of Ops which ultimately turns the abort action into an architecturally defined exception. The only execution units that can produce faults are the LU, the SU, and the FPU. In other words, RegOps can never fault: only LdOps, StOps, and FpOps can fault. RegOps can modify status flag values. The microprocessor must support the x87 architecturally defined floating-point flag bits that reside in the architecturally defined floating-point status word register.

#### **DESIGN NOTE**

#### Microarchitectural Faults and Traps

In addition to supporting all of the x86 architectural exceptions and interrupts, the K6 3D supports some microarchitectural faults and traps which are:

Fault Op Tque Fault Self-Modifying Code Check Trap

An abort cycle causes the invocation of a fault handler to determine what caused the fault or trap and act appropriately. Traps are handled somewhat differently than faults. When an x86 trap occurs (such as a data breakpoint trap), information associated with it is loaded into the scheduler and associated with the Op that caused it. Then, when that Op is going to be committed, the Op Commit Unit recognizes that a trap has been detected and sets a pending trap flip-flop. In effect, traps are accumulated as pending traps until the end of an x86 instruction is reached. The Op Commit Unit can recognize that it is retiring the last of all of the Ops associated with a given instruction. If there are any pending traps at the end of the commitment of an instruction, a "fault" is recognized at the beginning of the next instruction which, in turn, causes an abort cycle.

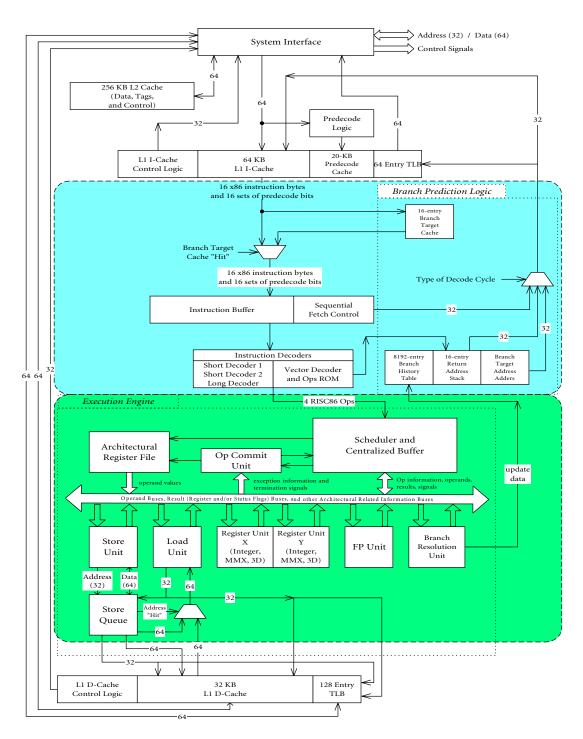

It is useful to think of the microprocessor consisting of an *upper portion* and a *lower portion* when explaining the abort cycle. This is shown in Figure 2.4 where the two portions are shaded differently. When an *abort cycle* is required, the following sequence of actions could occur to

upper and lower portions of the processor

complete the Ops in the scheduler that should be completed, with the non completed Ops being discarded:

- 1. let all Ops older than the Op that initiated the abort cycle commit and retire by allowing them to naturally progress down to the bottom row of the scheduler's buffer. The commitment of this Op and all younger Ops is inhibited.

- 2. when all older Ops have been committed, the entire machine, i.e., both the upper portion and the lower portion, can then be flushed.

- 3. after the flushing has been completed, instruction fetching and decoding can begin at the appropriate point.

#### **DESIGN NOTE**

#### Restarting the Upper Portion of the Processor

Restarting the upper portion of the processor does not affect the operation of the L1 I-Cache, therefore it is not included in the upper portion shown in Figure 2.4 on page 87. Likewise, restarting the lower portion does not affect the L1 D-Cache, so it is not part of the lower portion. If, for example, the L1 I-Cache (or the L1 D-Cache) is processing a "miss," then it is irrevocably committed to the processing of the miss.

This sequence is a direct result of a cost/performance trade-off. It allows for a simplified scheduler design. Several things are happening at the same time that need to be understood to appreciate this statement. On the one hand, the scheduler does not require logic in each entry to determine whether or not the associated Op should be flushed. When the flushing action occurs, all Ops in the scheduler will be marked "invalid." In this design approach, we will learn that a potential latency of one to two cycles in the flush action has been accepted while a simplification in the scheduler circuitry has been achieved.

Figure 2.4 Upper and Lower Portions of the Processor

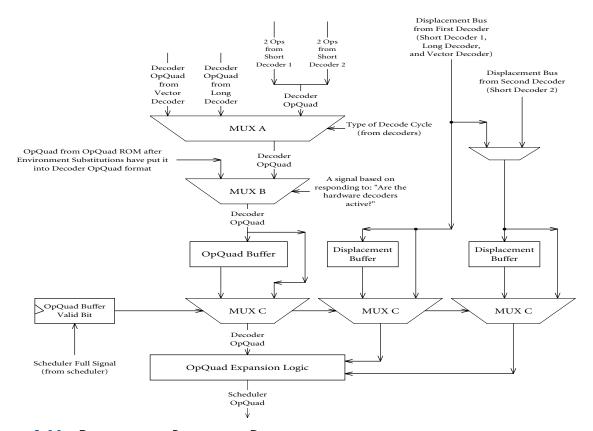

Importantly, for a BrOp-related abort, the K6 modifies the above sequence to reduce the flush performance penalty. The upper portion of the machine can be flushed while the older Ops are being completed. If Ops are generated before the lower portion of the machine can accept them (e.g., the lower portion of the processor may be in the process of invalidating the younger Ops in the scheduler), then these Ops are held until they can be consumed (see the OpQuad Buffer in Figure 2.8 on page 127.) The point is that since the fetch, decode, and execution of the Ops in the execution units are decoupled, the process of fetching and decoding the required instructions can be overlapped (done concurrently) with the completion and flushing of the appropriate Ops. More will be said about this in the section titled "Handling Faults, Traps, and Precise Interrupts" beginning on page 175.

#### ARCHITECTURAL AND MICROARCHITECTURAL REGISTERS

X86 instructions obtain their operands from and place their results in either the architectural registers or main memory. The execution units, in turn, must access these operands and produce the required results.

#### **DEFINITIONS**

#### Architectural and Microarchitectural Register Files

An architecture has a set of registers accessible by its instruction set for storing values associated with operand values, status flags, and other architectural state-related information. This set of registers is often called the *architectural register set* or *architectural register file*. The values stored in it at any instant in time are called the *architectural machine state* or *instruction set architecture machine state*. The microarchitecture typically has a different number of registers, most often a larger number, that are used not only to store the architectural machine state but also to store *microarchitectural machine state*, i.e., operand values, status flags, and state information that is used exclusively in the microarchitecture and not visible to the instruction set architecture.

The K6 3D must support all of the registers defined by the x86 instruction set architecture. These registers include:

- 1. eight 32-bit integer general purpose registers.

- 2. six 16-bit segment selector registers and associated segment descriptor registers.

- 3. one 32-bit (EIP) instruction pointer register.

- 4. x87 floating-point unit registers (a stack of eight 80-bit internal floating-point registers, a 16-bit status word register, a 16-bit control word register, and a 16-bit tag word register).

- 5. eight 64-bit MMX registers which, from an instruction set architecture perspective, are aliased with the eight FPU stack registers.

- 6. one 32-bit EFLAGS register.

- 7. five 32-bit control registers.

- 8. eight 32-bit debug (breakpoint) registers.

- 9. memory management registers, namely the x86 Global Descriptor Table Register, the Local Descriptor Table Register, the Interrupt Descriptor Table Register, and the Task Register. <sup>16</sup>

The K6 3D supports the 3D registers associated with the 3D instruction extensions to the x86 instruction set architecture. The 3D registers are conceptually and physically one and the same as the MMX registers identified in the above list. In addition, the K6 3D supports a number of special registers which are described in the section titled "Special Registers and Model Specific Registers" beginning on page 94.

#### Integer Registers

The K6 has twenty-four 32-bit integer registers in the integer architectural/microarchitectural register file plus it has twenty-four 32-bit integer renaming registers. The twenty-four registers in the integer architectural/microarchitectural register file consist of eight architecture registers that correspond to the x86 32-bit general purpose registers (EAX, EBX, ECX, EDX, EBP, ESP, ESI, and EDI) and sixteen microarchitecture scratch registers (t0 through t15). The twenty-four renaming registers are located in the scheduler's twenty-four Op entries—one per entry.

The x86's 32-bit integer architectural register set supports addressing, for byte operations, of either of the lower two bytes of half of some, but not all, of the registers. Based on a register size specification, the 3-bit register numbers within x86 instructions are interpreted as either high (H) or low (L) byte registers or as word or double-word registers. The relationship between these interpretations is seen in the following table.

For example, the Global Descriptor Table Register holds the 32-bit base address and 16-bit segment limit for the currently active Global Descriptor Table.

| 32-Bit Name<br>(dword) | 16-bit Name<br>(word) | 8-bit Name<br>(high order<br>byte) | 8-bit Name<br>(low order<br>byte) |

|------------------------|-----------------------|------------------------------------|-----------------------------------|

| EAX                    | AX                    | АН                                 | AL                                |

| EBX                    | BX                    | ВН                                 | BL                                |

| ECX                    | CX                    | СН                                 | CL                                |

| EDX                    | DX                    | DH                                 | DL                                |

| EDI                    | DI                    | _                                  | _                                 |

| ESI                    | SI                    | _                                  | _                                 |

| ESP                    | SP                    |                                    | _                                 |

| EBP                    | BP                    | _                                  | _                                 |

Table 2.3 x86 General Purpose Register Names and Sizes

The integer microarchitecture register set also supports similar addressing of the lower two bytes of half of these scratch registers: registers +1 through +4 and registers +8 through +11. This is similar to the way in which byte addressing is supported in the x86 instruction set architecture registers.

#### The x87 Floating-Point Registers

As noted above, the x86 floating-point unit has eight 80-bit internal floating-point registers, a 16-bit status word register, a 16-bit control word register, and a 16-bit tag word register. The eight data registers are 80-bits wide registers and comply with the IEEE floating-point standard extended precision format. As such, the x87 instruction set architecture views them as 80-bit registers. The K6 FPU does its own local register renaming for all of its registers.

#### MMX and 3D Registers

The x86 MMX register set consists of eight 64-bit registers which the MMX instructions access directly using the register names MM0 through MM7. Although the eight MMX registers are defined in the x86 instruction set architecture as separate registers, they are aliased to the eight registers in the FPU data register stack. The MMX registers are mapped onto the lower sixty-four bits of the x87 registers, with the upper sixteen bits defined to effectively be all ones. The 3D instructions, being floating-point

analogs of the MMX instructions, also use and share the MMX registers with the MMX instructions. Subsequently, we will call these registers the MMX/3D registers.

There are nine MMX/3D 64-bit architecture/microarchitecture registers and twelve MMX/3D 64-bit renaming registers. The nine architectural/microarchitectural registers consist of eight that correspond to the x86 architecture MMX 64-bit registers (MM0 through MM7) and one microarchitecture scratch 64-bit register (MMt1).

#### **DESIGN NOTE**

#### Number of MMX Registers

The K6 has six 64-bit MMX renaming registers which reflects its singlepipeline implementation. The K63D, which also supports the 3D instruction set extensions to the x86 instruction set architecture, has twelve 64-bit MMX/3D renaming registers, which reflects its dual-pipeline implementation.

A presentation by Lance Smith, giving an overview of a non-3D version of the K6, is entitled, "The AMD-K6 Processor: Microarchitecture Overview and Product Update," and can be found on the CD-ROM.

#### REGISTER NUMBER AND NAME MAPPINGS

X86 instructions specify general registers via a 3-bit register number. In the microarchitecture, the K6 adds two leading 0's to the x86's 3-bit register number to form a 5-bit internal architecture/microarchitecture register number. Table 2.4 gives the correspondence between these 5-bit numbers and the various integer, MMX/3D, and scratch registers. The interpretation of a register number as either an integer or an MMX/3D register is, obviously, based on the instruction that is accessing the register. The uses of reg, regm, MMreg, and MMregm are explained in Chapter 3.

Table 2.4 Register Number/Name Correspondence

| Register<br>Number | 32-bit<br>Register<br>Name | 1-Byte<br>Register<br>Name | 64-bit<br>MMX/3D<br>Register Name |

|--------------------|----------------------------|----------------------------|-----------------------------------|

| 00000              | EAX                        | AL                         | MMreg                             |

| 00001              | ECX                        | CL                         | MMreg                             |

| 00010              | EDX                        | DL                         | MMreg                             |

| 00011              | EBX                        | BL                         | MMreg                             |

| 00100              | ESP                        | AH                         | MMregm                            |

| 00101              | EBP                        | СН                         | MMregm                            |

| 00110              | ESI                        | DH                         | MMregm                            |

| 00111              | EDI                        | ВН                         | MMregm                            |

| 01000              | t1                         | t1L                        | MMt1                              |

| 01001              | t2                         | t2L                        | —                                 |

| 01010              | t3                         | t3L                        | —                                 |

| 01011              | t4                         | t4L                        | —                                 |

| 01100              | t5                         | t1H                        | —                                 |

| 01101              | t6                         | t2H                        | —                                 |

| 01110              | t7                         | t3H                        | _                                 |

| 01111              | t0/_ <sup>a</sup>          | t4H                        | —                                 |

| 10000              | t8                         | t8L                        | —                                 |

| 10001              | t9                         | t9L                        | —                                 |

| 10010              | t10                        | t10L                       | _                                 |

| 10011              | t11                        | t11L                       | —                                 |

| 10100              | t12                        | t8H                        | _                                 |

| 10101              | t13                        | t9H                        | _                                 |

| 10110              | t14                        | t10H                       | _                                 |

| 10111              | t15                        | t11H                       | _                                 |

| 11000              | reg                        | reg                        | MM0                               |

| 11001              | reg                        | reg                        | MM1                               |

| Register<br>Number | 32-bit<br>Register<br>Name | 1-Byte<br>Register<br>Name | 64-bit<br>MMX/3D<br>Register Name |

|--------------------|----------------------------|----------------------------|-----------------------------------|

| 11010              | reg                        | reg                        | MM2                               |

| 11011              | reg                        | reg                        | MM3                               |

| 11100              | regm                       | regm                       | MM4                               |

| 11101              | regm                       | regm                       | MM5                               |

| 11110              | regm                       | regm                       | MM6                               |

| 11111              | regm                       | regm                       | MM7                               |

Table 2.4 Register Number/Name Correspondence (Cont)

#### **DESIGN NOTE**

#### Register Size Specification

In the section titled "Formats for Decoder Ops" beginning on page 142, we will learn that the register size, from an Op perspective, is specified by either the ASz or DSz field of the Op. ASz is used for base and index registers in LdStOps. DSz is used for the data register in LdStOps and the source operand and result or destination registers in RegOps. The scratch integer register set supports addressing of the lower two bytes of half of these registers: t1-t4 and t8-t11.

The combination of the integer architectural/microarchitectural register file and the MMX/3D architectural/microarchitectural file will be called thet Architectural Register File and is shown in Figure 2.2 on page 69. The K6 3D's implicit renaming scheme is discussed in Chapter 3. The microarchitectural and renaming registers just discussed are not the only microarchitectural registers in the K6 3D. There are additional special registers that the scheduler, OCU, and execution units use in many aspects of their work. We will now describe these special registers as some of them are referenced in the pseudo-RTL descriptions that appear in Chapter 3. You may want to skim this section now, but revisit it from time to time when reading Chapter 3.

architectural/microarchitectural register file

<sup>&</sup>lt;sup>a</sup> The "t0" and "\_" mnemonics are synonymous. "\_" is used when an operand or result value is a "don't care." t0 is like the "traditional" RISC R0 register.

#### HISTORICAL COMMENT, DEFINITION AND SUGGESTED READINGS

#### Register Renaming

Register mapping is the process of associating specific microarchitectural (physical) registers with specific architectural (virtual) registers. The mapping can be *static* (bound before execution) or *dynamic* (done at execution time). If the process is dynamic, i.e., the "renaming" (re-mapping) occurs during execution, it is called *register renaming*. The mappings must be *complete*, i.e., each architectural register having a valid value must have a corresponding microarchitectural register mapped to it at each point in time when that valid value is associated with the architectural register. Register renaming can be used to remove various types of dependencies (in particular, write-after-read and write-after-write dependencies).

Although register renaming has been used recently by a number of microprocessor vendors including Intel and AMD, its use is not new with microprocessors—see, for example, the 1967 Tomasulo article referenced below. At the same time though, microprocessors did not begin employing this technique until over 20 years after being used in mainframes. According to Peuto:

"The MIPS R2000 in 1986 was the first microprocessor to implement a simple pipeline with branch prediction favoring the branch-taken path. This pipeline was adopted for the 80486 in 1989. Register renaming and instruction scheduling, both concepts from the 360/91, were used by Intel for Pentium Pro in 1995, after several RISC micro-processors had already adopted them."

For a detailed discussion concerning a register renaming scheme, see R. M. Tomasulo, "An Efficient Algorithm for Exploiting Multiple Arithmetic Units," IBM Journal of Research and Development, Vol. 11, January 1967, pp. 25-33. A copy of this article is the companion CD-ROM. See also: Mike Johnson, Superscalar Microprocessor Design, Prentice Hall. 1991 and

David A. Patterson and John L. Hennessy, Computer Architecture: A Quantitative Approach, 2<sup>nd</sup> Edition, Morgan Kaufmann Publishers, Inc. 1996. A related article, "The Microprocessors Follow Mainframe Path," by Bernard L. Peuto, in *Microprocessor Report*, April 21, 1997, is also on the CD-ROM,

#### SPECIAL REGISTERS AND MODEL SPECIFIC REGISTERS

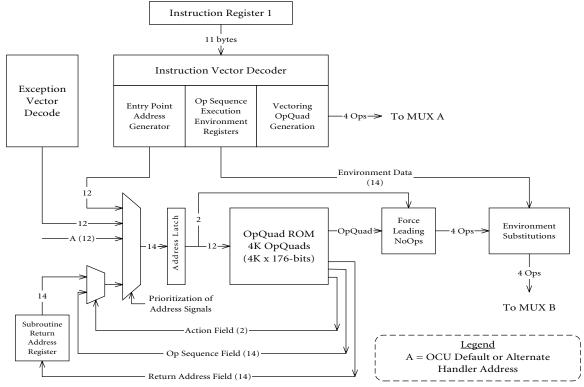

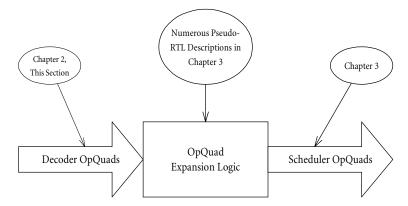

The special registers shown in the RUX pipeline of Figure 2.3 on page 81 are not accessible from x86 instructions. They are accessible only through special RegOps in OpQuad Sequences. What are OpQuads? The instruction decoders, during a decode cycle, always produce a group of four Ops which is called an *OpQuad* (see Figure 2.6 on page 115). What are OpQuad Sequences? A sequence of OpQuads fetched from an on-chip ROM (called the OpQuad ROM) is called an OpQuad Sequence. Only the hardware decodes of common/simple instructions produce a single OpQuad. OpQuad sequences result from the decode of more complex instructions. OpQuads and OpQuad sequences are discussed in considerably more detail in the section titled "OpQuad Sequences" beginning on page 137.

#### Video Clip on CD-ROM

Greg Favor, Principal Architect of the K6 3D, addresses the following question in this video clip, "Why do you translate x86 instructions into RSIC86 Op sequences?"

The special registers are used for a variety of purposes including internal configuration, debugging, and the processing of traps. Although the special registers are not meant for general use, some of them contain information that is made available to BIOS and operating system implementers via reads and writes to what are termed *model-specific registers*.

#### SUGGESTED READINGS

#### Model-Specific Registers

Discussions of the K6 3D and K6 model-specific registers and the instructions that access the data in them, RDMSR (Read Model-Specific Register) and WRMSR (Write Model Specific Register), can be found in the AMD K86 Family BIOS Design Application Note on the CD-ROM.

Some of the special registers reside physically within the RUX, others are external to the RUX in other execution units, other blocks of the machine, or in a special scratchpad memory. In general, when the special registers external to the RUX and in other blocks of the machine are read in an OpQuad Sequence, two reads are required. The first read loads a temporary internal RUX register from the external unit. The second read delivers the data to its destination from this temporary register.

The following codes will be used in the "Access" column in the tables that follow:

INTERPRETATION FOR THE ACCESS COLUMN

| Access | Interpretation                                                              |

|--------|-----------------------------------------------------------------------------|

| R      | Read-only special registers                                                 |

| W      | Write-only special registers                                                |

| R/W    | Readable and writable special registers                                     |

| E/W    | Write-only special registers; readable copy maintained in scratchpad memory |

scratchpad memory

Additionally, all "Reserved" bits are read as zero and should be written with either a zero for forward compatibility with software use of these bits. Some x86 architectural registers (e.g., some of the CRxx, DRxx, and TRx registers plus other registers such as TR and data segment selector registers) are maintained only in scratchpad memory and are thus R/W scratchpad memory locations. Special registers in scratchpad memory are read using a single LdOP versus one or two RegOPs. Such registers are not included in the tables that follow.

Table 2.5 SRO, GENERAL CONTROL AND STATUS REGISTER

| Bit | Name      | Function                                                                                                | Access |

|-----|-----------|---------------------------------------------------------------------------------------------------------|--------|

| 0:1 | CPL       | Copy of architectural current privilege level (CPL)                                                     | R      |

| 2   | IOS       | I/O sensitivity status                                                                                  | R      |

| 3   | V86       | V86 mode = EFlags.VM && CR0.PE                                                                          | R      |

| 4   | REAL      | Real Mode = !CR0.PE                                                                                     | R      |

| 5   | EWBE      | External write buffer empty                                                                             | R      |

| 6   | BusBsy    | Indicates if there are any active/asserted internal requests for bus cycles in the processor system bus | R      |

| 7   | PMSP      | POP memory base = SP (from OpQuad Sequence environment)                                                 | R      |

| 8   | FLUSHP    | FLUSH# request pending                                                                                  | R      |

| 9   | SMIP      | SMI# request pending                                                                                    | R      |

| 10  | INITP     | INIT request pending                                                                                    | R      |

| 11  | NMIP      | NMI request pending                                                                                     | R      |

| 12  | INTRP     | INTR request pending                                                                                    | R      |

| 13  | STPCLKP   | STPCLK request pending                                                                                  | R      |

| 14  | VME       | Virtual Mode Extension                                                                                  | R/W    |

| 15  | PVI       | Protected Virtual Interrupt                                                                             | R/W    |

| 16  | ClrFLUSHP | Clear FLUSH# edge latch                                                                                 | W      |

| 17  | ClrSMIP   | Clear SMI# edge latch                                                                                   | W      |

| 18  | ClrINITP  | Clear INIT edge latch                                                                                   | W      |

| 19  | ClrNMIP   | Clear NMI edge latch                                                                                    | W      |

| 20  | ClrISTF   | Clear INTR/STPCLK# temporary mask flag                                                                  | W      |

| 21  | ClrBSNTF  | Clear IBrkPt/SMI#/NMI temporary mask flg                                                                | W      |

| Bit | Name    | Function                                | Access |

|-----|---------|-----------------------------------------|--------|

| 22  | NF      | NMI mask flag                           | R/W    |

| 23  | RIF     | Halt instruction fetch                  | W      |

| 24  | SMIACT  | System management mode active           | R/W    |