# Chapter 1 Microprocessors, Platforms, and Systems

his chapter examines the process of designing and implementing a microprocessor and then examines issues that arise in the process of designing and implementing a 3D graphics PC platform. Toward the end of the chapter, several Eckert-Mauchly award winners share their insights regarding important references in the field of computer architecture. Although this chapter is written for each of the books intended audiences, there are some subsections that have details that will be of more interest and use to practitioners and those in universities. The following *road map* for this chapter identifies these sections.

#### ROAD MAP OF CHAPTER 1

| Section                                                                                                                                                                                                                             | Audience                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| The following are more detailed subsections:  Model at the Gate and Circuit Levels Gate and Circuit Level Simulation and Hardware Emulation Generate Netlists and Physical Layout Mask Generation, Wafer Fabrication, and Packaging | Practitioners, University Professors, and Students |

What makes microprocessors especially difficult to design and implement are their complex nature, large size as measured in the number of electronic devices required in their implementation and the number of highly dependent trade-offs that must be made to achieve given size, yield, voltage, power, temperature, price, and performance points. The situation

DESIGNING AND IMPLEMENTING A MICROPROCESSOR

<sup>&</sup>lt;sup>1</sup> See the Preface

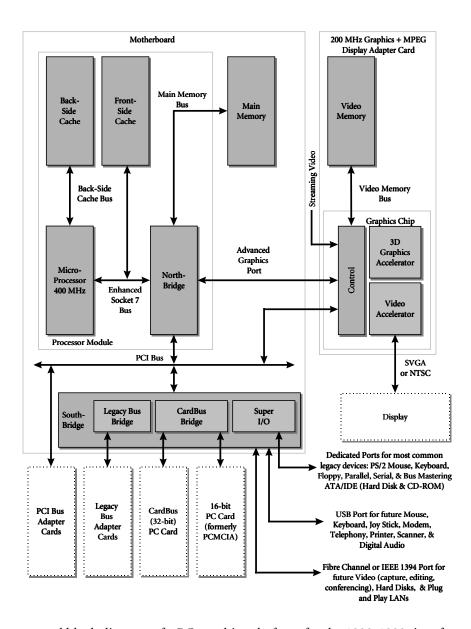

hardware-software co-design

is complicated by the fact that the performance of the microprocessor *should not* be looked at independently of how it is integrated into a platform and a system. Issues such as the performance characteristics (bandwidth, latency, clock rate, etc.) of the core logic chipset, the memory architecture, the number and types of buses and their characteristics, and the I/O device support integrated onto the motherboard must be considered in a number of the design trade-offs. It makes little sense to have the fastest microprocessor in the world integrated into a system with an inappropriate bus or memory architecture or I/O support.

This implies that the core logic chipset, bus, memory architecture, and motherboard design teams must work intimately with the microprocessor design team. Each of these system elements is also significantly impacted by the rate of increases in clock speed and circuit density as well as important changes in packaging technology. Instead of advocating *hardware-software co-design*, we advocate *hardware-system co-design*. The "hardware" component of hardware-software co-design often refers only to processor design. Even when used in this restricted context, the hardware-software co-design process has substantive advantages when contrasted with the approach used just a few years ago of designing a processor without on-going, detailed interactions with software teams, such as compiler writers and operating systems implementers, that ultimately leads to the co-evolution, testing, and integration of the processor and the software.

#### ARTICLE ON CD-ROM

An insightful article that clearly shows the dependent nature of processor and compiler design is, "Compiler Technology for Future Microprocessors," by Wen-Mei Hwu, Richard E. Hank, Daniel M. Lavery, Grant E. Haab, John C. Gyllenhaal, and David I. August, *Proceedings of the IEEE*, December 1995.

hardware-system co-design

We use the term *hardware-system co-design* to extend these notions to include on-going, detailed interactions with the teams involved in the design of the core logic chipset, the BIOS, the bus and memory architectures, the motherboard and any special device controller chips that will be integrated on the motherboard, (e.g., graphics controller chip, a high-speed FAX-data-voice modem chip, or a high-performance network controller chip). The second half of this book deals with many of these issues. In the first half, we focus on the microarchitecture of the microprocessor.

#### WHAT NEEDS TO BE DONE?

How do you go about implementing a microprocessor? What needs to be done can be stated quite simply: We need to take the high-level instruction set architecture representation or model of the microprocessor's architecture and transform it into a correctly working, high-performance silicon chip that will have a long, failure-free life. Doing that is, of course, not so simple.

Models play an integral role in the transformation process. Models are used to explore and analyze alternative design solutions and to verify behavioral (functional) specifications, compatibility requirements, and adherence to standards. A model—a representation of the microprocessor expressed in some language—is typically implemented in a simulator, emulator, or a combination of both. The model can represent the microprocessor at the architecture, microarchitecture, logical implementation, or chip level, or it can span one or more of these levels. While computer architects typically tend to deal with issues at the architecture and microarchitecture levels, digital design engineers tend to be more directly involved with issues at the logical implementation and chip levels. As a result, these two groups often approach the modeling and simulations issues from different perspectives and often with a different set of terminology and tools. For example, some digital system designers might refer to the levels of abstraction shown in Table 1.1 when discussing the modeling and simulation of digital systems:

We use the terms "representation" and "model" interchangeably in this discussion.

Table 1.1 Levels of Abstraction Comparison

| Digital Design<br>Engineer's Level | Examples of Modeled Entity                              | Approximate Equivalence to Computer Architect's Level |

|------------------------------------|---------------------------------------------------------|-------------------------------------------------------|

| system level                       | pipelines, instruction decoders, and TLBs               | microarchitecture                                     |

| register transfer level (RTL)      | registers, buses, multiplexers, and combinational logic | microarchitecture<br>and logical implementation       |

| gate level or<br>logic level       | library cells of AND,<br>OR, etc. gates                 | logical implementation                                |

| transistor level                   | transistors in various process technologies             | chip                                                  |

| layout level                       | geometries, transistor placements                       | chip                                                  |

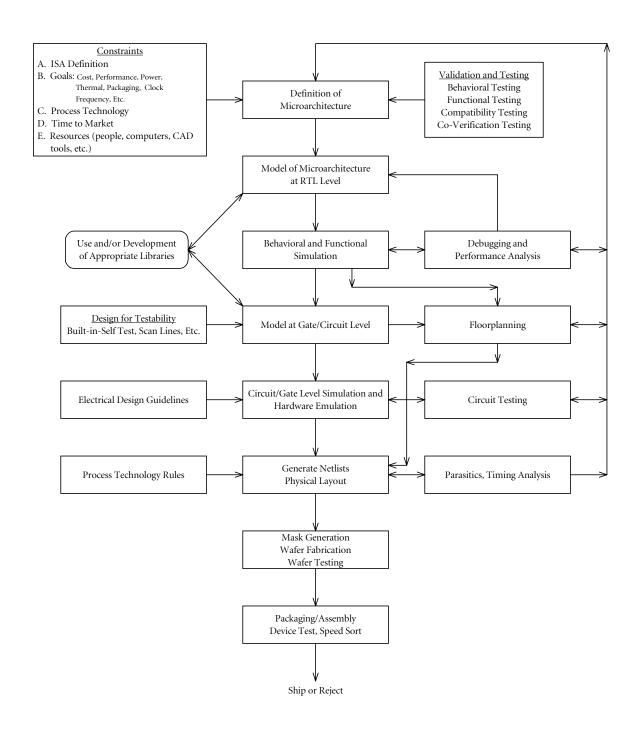

These levels of abstractions (sometimes also called stages) are shown in more detail in Figure 1.1. The differences between the terminology and tools each group employs are lessening because:

- the size and complexity of the microprocessors and the impact of the implementation-related issues on the cost/performance of the overall system require these groups to work closer together, with the result that the boundaries between some of the adjacent stages in the design process are becoming increasingly blurred.

- the decreasing cost of high-performance computer platforms has precipitated a movement of electronic design automation tools from specialized workstations to more widely available desktop platforms resulting in an increase in the power and scope of these tools.

Let us now take a look at the design and implementation process represented in Figure 1.1 in more detail.

#### **CONSTRAINTS**

We assume that the instruction set architecture to be implemented has been previously defined. Thus the design and implementation process does not start with the design of the instruction set architecture but with the design of the microarchitecture, (i.e., the set of resources and methods used to implement the instruction set architecture). Recall from the earlier definition of the term microarchitecture that it includes the way in which these resources are organized as well as the design techniques used to reach the target cost and performance goals. Presumably, the instruction set architecture has been designed with an intimate knowledge of what the programs implemented actually do, (e.g., knowing what systems resources are used and how frequently, and knowing what memory bandwidth various classes of algorithms require). Knowing what programs do is absolutely essential to identifying what resources and instructions are required in the architecture.

It cannot be emphasized strongly enough the importance of understanding what the processor is doing when it executes specific benchmarks or workloads. This assumes that the benchmarks and workloads are truly representative of how the system will be used. This assumption, however, is one that is difficult to meet. Not only must suitable workloads be created, but representative traces from those workloads must also be developed. Using bad trace data in good performance models has been the cause of more than one processor's performance deficiencies. Moreover, deciding on what workloads are representative of current (or future) target markets can be extremely difficult.

The detailed analysis of performance data and the subsequent use of that analysis in the design process is the cornerstone of many, if not most, architectural design decisions.

Figure 1.1 Design Process

The design of specific workloads and benchmarks is an art in itself.

Even given these difficulties with developing good performance models and good trace data, it is safe to say that the detailed analysis of performance data and the subsequent use of that analysis is the cornerstone of many, if not most, central architectural design decisions. Some examples are data from address traces that yields information about such things as the frequency of occurrence of conditional branches, address modes, exception conditions, and interrupts.

The workloads and benchmarks and subsequent analysis may be targeted at a specific component of the processor (e.g., the integer unit or the floating-point unit), a group of components (e.g., the chunks of logic involved in the fetching, predicating, and decoding of instructions), the entire processor itself, or the processor interconnected with one or more of its external system components (e.g., the chipset or off-chip cache). The design of specific workloads and benchmarks is an art in itself as often millions of instruction executions are needed to gain some understanding of the specific behavior you are attempting to study. Both the architect and the digital systems engineer need to know where the bottlenecks are in their respective models of the microprocessor in order to remove these bottlenecks.

Clearly, one of the most important constraints placed on the microarchitecture design team is the definition of the instruction set architecture that they need to support. For the K6 3D microarchitecture, it is the widely used x86 instruction set architecture. Indeed, one view of the K6 3D is that it is a high-performance CISC-on-RISC microprocessor. The CISC-component is the x86 instruction set architecture, while the underlying RISC-component is known as the Enhanced RISC86 microarchitecture. The most important implication of this constraint is that the K6 must be fully x86 binary code compatible, including code using the x86 MMX multimedia instruction set extensions. We will learn later that the K6 3D also provides an additional set of AMD-developed instruction set extensions called the AMD-3D instructions which support high-performance 3D graphics, audio, and physics-based modeling and simulation processing.

#### VIDEO ON CD-ROM

Amos Ben-Meir, Principal Designer of the K6 3D, addresses two questions of interest in this video clip: "What is needed to design state-of-the art microprocessors?" and "What were the design methods that enabled the K6 3D to be implemented in such a short period of time?"

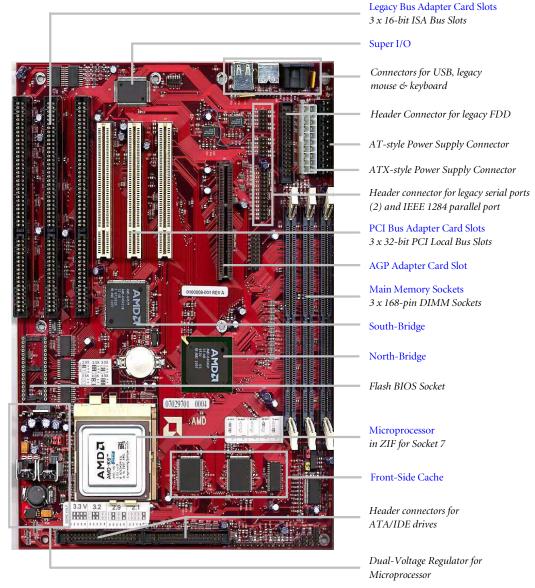

Other constraints, both from a platform and performance point of view have to do with systems-related issues. Among the design goals for the K6 3D processor were explicit objectives for it to be Socket 7 compatible

and for it to fit within the electrical, power and thermal specifications, and the EMI envelope of the Intel Pentium processor. If it were successful in meeting these objectives, it could readily integrate into industry-standard Pentium-compatible motherboards, chipsets, power supplies, and thermal designs.

#### COMPARATIVE ANALYSIS

#### Socket 7 Compatible

Socket 7 compatible means that the system bus interface is compatible with the industry-standard 64-bit Pentium P55C bus protocol and motherboard socket. One of the most important differences between the K6 and Intel's Pentium Pro and Pentium II processors is the way in which the microprocessor chips connect to the rest of the system and the system bus interface.

The K6, like the Intel Pentium and the Intel Pentium MMX (P55C), are "Socket 7 compatible" as defined above. However the Intel Pentium Pro and the Intel Pentium II (Klamath) use a different bus interface or protocol (called the P6 bus interface) and each uses a different physical motherboard connector. The Intel Pentium Pro uses a dual-cavity PGA packaging technology. The Intel Pentium II uses Intel's Single Edge Cartridge (SEC) technology and its Slot 1 and Slot 2 connectors. These issues and their design implications (e.g., the way in which the L2-Cache is interfaced to the system and the performance issues involved) are discussed in Chapter 4 and Chapter 6.

The analysis of the instruction set architecture is based on knowledge of typical application and system software, typical coding practice, behavior or nature of code generated by various compilers, and analysis of instruction and data reference traces of actual software. On this last point, which is one of the most significant inputs to the microarchitecture development process, the following elements are key:

- the capability to capture traces of the execution of any and all code, (e.g., privileged OS code, device driver code, and application code).

- 2. the capability to use long traces—ten million to one billion instructions long.

- the need to have an accurate and detailed trace-driven performance model of the design that can output a wide variety of performance-related statistics and that can be readily changed to explore alternative design options.

## **TESTING**

During the design process, we undertake different types of testing—functional (i.e., behavioral) testing, structural testing, compatibility testing, and performance testing. There are basically three different levels of testing that need to be considered for each of these types. The testing of:

- 1. the design (i.e., verifying the design realizes the instruction set architecture without any errors).

- 2. the logical implementation (i.e., verifying the logical implementation realizes the design without any errors).

- 3. the chip (i.e., verifying the physical device realizes the logical implementation without any errors).

# Functional (Behavioral) Testing

Functional (behavioral) testing is a method for verifying design correctness via simulation. A "block" or "component" representing a set of functions or system behavior is modeled. A simulator is constructed for the model. An input stimulus is applied to the block's inputs and the block's outputs are compared with the expected outputs. Trace buffers are used to chronicle the behavior of the block, permitting examination of the behavior for an arbitrary period of time prior to matching results. Such computer modeling of the design is begun at an early stage in the design process to verify design concepts in a top-down fashion. Functional testing is continued as more detail is added to the design and changes are made.

Initially the simulations are strictly at a highly abstract behavioral level and are performed on large blocks that model major functional areas of the design. As design implementation progresses, the original blocks are usually hierarchically decomposed into sub-blocks. The model is managed to track the design hierarchy and thus becomes more detailed over time. Testing is generally performed first on each new sub-block and then interactions between blocks are confirmed.

#### **DEFINITION**

#### Test Vector

Test vectors are the collection of values of input stimulus and expected output results for each sequential stage of simulation. The test vectors are intended to cover all inputs and outputs (pins entering or leaving) each block being tested. Test vectors for larger blocks don't need to include I/Os of smaller blocks that do not appear at the boundary of the larger block.

The development of test vectors is time-consuming and may be naively omitted from project scheduling or its extent may be underestimated. Writing the vectors generally requires a detailed knowledge of the blocks being tested. Often the logic designer of the blocks must write the vectors or at least define an initial template for others to follow. Insuring comprehensive testing coverage for large complex blocks is a specialized field, because exhaustive testing of all possible combinations of inputs may not be practical. Once confidence in the test vectors is obtained, vectors may be used in gate-level or other lower-level simulations, to verify bottom-up design correctness.

Functional simulators are generally restricted to behavioral modeling. When the gate-level design of a block is synthesized or manually designed, it too can be modeled using a gate-level simulation. Gate-level simulators generally can handle the simulation of sub-blocks that have behavioral descriptions. Thus some blocks may be at a gate-level, while others are still using a behavioral model. Often the focus is on verifying the gate-level design of a particular block, and blocks providing stimulus to or sampling outputs from the block of interest need only be behaviorally modeled.

# Design for Testability

A digital circuit is an implementation of the specification of a desired function, (i.e., it exhibits a desired behavior). A microprocessor is a collection of hundreds of thousands of such circuits. Given the complexity of the resulting microprocessor chips, the testing of them must be integral in their design from the onset. Incorporating testing technology into a design from its inception is often referred to as "design for testability" or DFT. Using DFT techniques invariably reduces costs and design time.

There have been a number of important DFT advances made at the logical implementation and chip level, such as boundary scan testing, full operational scan of internal state elements (e.g., flip-flops), built-in self-test (BIST), test vector generation, signature analysis, and observers. A number of these approaches required additional circuitry to be included in the design, solely for the testing function, reducing the amount of the total gates on the chip that are available to implement the microprocessor. Thus, another trade-off emerges regarding the distribution of gates between functionality and testing and the benefits from the use of DFT techniques.

A substantive treatment of testing—dealing with issues such as fault modeling, fault manifestation,<sup>2</sup> fault detection (controllability and

For example, at the chip level one needs to conjecture how fabrication faults such as holes in insulating layers, bridging connections in metal layers, missed contacts, and poor control of etching will be manifested so that it is possible to test for them.

observability), test design, test data (collection and generation), and test coverage—is well beyond the scope of this book. Particularly since each of these topics needs to be discussed in the context of testing the design, the implementation, and the chip. However, a number of fundamental ideas are presented so the reader has an appreciation of the issues involved.

# **Suggested Readings**

#### Design for Testability

- 1. H. P. G. Vranken, M. F. Willeman, and R. C. van Wuijswinkel, "Design for Testability in Hardware-Software Systems," *IEEE Design & Test of Computers*, Vol. 13, No. 3, Fall 1996, pp. 79-87.

- 2. K. P. Parker, The Boundary Scan Handbook, Kluwer Academic Publishers, 1992.

- 3. IEEE Standard 1149.1-1990, *Test Access Port and Boundary Scan Architecture*, January 1992 and the associated standard, 1149.1b, *Boundary Scan Description Language (BSDL)*, 1991.

- 4. M. Tegethoff, "IEEE Standard 1149.1: Where Are We? Where From Here?" *IEEE Design & Test of Computers*, Vol. 12, No. 2, Summer 1995, pp. 53-59.

- 5. B. T. Murray and J. P. Hayes, "Testing ICs: Getting to the Core of the Problem," Computer, November 1996.

- 6. V. D. Agrawal and C. R. Kime and K. K. Saluja, "A Tutorial on Built-in Self-Test, Part 1: Principles," *IEEE Design & Test of Computers*, Vol. 10., No. 1, May 1993, pp. 73-82.

- 7. V. D. Agrawal and C.R. Kime and K. K. Saluja, "A Tutorial on Built-in Self-Test, Part 2: Applications," *IEEE Design & Test of Computers*, Vol. 10., No. 2, June 1993, pp. 69-77.

You can find the full text versions of *Part 1* and *Part 2* of the Agrawal, Kime, and Saluja tutorial as well as the Murray and Hayes article, on the companion CD-ROM.

# Compatibility Testing

The difficulty of achieving x86 architectural compatibility is generally underestimated. The business issues surrounding compatibility are generally equally underestimated. We will see that these business issues contribute directly to the technical difficulties in achieving compatibility.

From a business perspective, x86 compatibility is an absolute requirement. First of all, if it is perceived that the affected microprocessors are flawed merchandise, there is the real possibility of being held liable to recall or field-replace the flawed units. Equally important however, is that consumers simply will not accept a microprocessor if there is a lack of confidence that the microprocessor will not successfully run popular or legacy software. This latter problem is aggravated by the fact that the program-

mers of such software may have relied on unintended and undocumented behaviors, which historically have been prevalent in x86 microprocessors.

Undocumented or imprecisely documented behaviors are at the center of the difficulty in achieving compatibility. The user and programming manuals for x86 microprocessors have historically not compared with documents like the *IBM/370 Principles of Operation* manuals. The x86 manuals have generally been little more than abstractions that approximate the exact behavior of the microprocessor. Such x86 manuals cannot be considered as formal reference documents, written and edited with extreme care, and thereby suitable for design purposes.

Generally speaking, the first vendor to implement a commercially successful microprocessor will de facto determine its behavior for all implementations to follow. Even if part of that initial behavior includes unintended and undocumented artifacts, the earliest implementation defines the compatibility requirements for all other vendors. The first vendor does not need to reverse engineer the behavior, at least not until a subsequent generation's implementation. Even then, this vendor has knowledge of the exact logic underlying the original implementation, and can use that to retroactively deduce the precise behavior. The second implementer to market the instruction set architecture of the microprocessor does not have these luxuries.

Designers take great risks when making extensions to instruction sets. If the extensions are not useful, they will increase the cost of the processor without returning benefit. If the extensions are useful, but implemented inefficiently, they leave room for competitors to make improvements. The x86 architecture has had a number of extensions over its history. An early extension was the introduction of the 80286 instruction set, which extended the addressable memory from 1-MByte to 16-MBytes. This extension was not very successful. It failed to support compatibility with the underlying 8086 architecture in a way that could be used efficiently in practice. Some commercial software used the larger memory model, but two key operating systems at the time, Microsoft's Windows and IBM's OS/2, were unable to produce widely accepted versions using these extensions. Subsequent instruction set extensions embodied in the 80386 architecture provided an efficient 8086 emulation mode, and that enabled new operating systems to run 80386 and legacy 8086 code with equal efficiency.

One of the lessons to be learned from these examples is that instruction set extensions should be done in concert with the development of both the operating systems and important software applications that will use them. This suggests that computer architects and software designers should sit down together to determine what the extensions should do and how they should be implemented (see *hardware-software co-design* and *hardware-system co-design* on page 2). From a competitive point of view, this means that some proprietary information has to be shared across the

Compatibility must not only deal with "official" or "publicly" documented features, but must also deal with "unofficial" and "undocumented" features and with behaviors in obscure cases.

industry with some partners while kept secret from companies in the business of designing competitive microprocessors.

The ideal strategy is to publicly announce the instruction set extensions and the operating systems and applications software use of the extensions at the same time. In reality, the software announcements usually always follow the availability of the instruction set extensions, often by as much as a year. As an example, the x86 MMX instruction set extensions were announced in the spring of 1997. By early 1998, very little MMX software had been released, although a large number of the potential developers who could make use of the extensions had committed to use them in their applications. So, it looks promising that these extensions will indeed succeed.

On the other hand, the 80286 instruction set extensions were never truly successful. Yet they were used by enough software to force 80286 compatibility to a component of x86 designs through the 1990s and possibly beyond. Virtually all 80286 applications that were running in the late 1990s had long ago been converted to the 80386 memory model. But the possibility that some still exist for the 80286 memory model creates what amounts to a tax on the x86 architecture to support software that, in all probability, is no longer in use. Given this background into some of the problems involved in extending an instruction set, let us return to the issues regarding compatibility testing.

Because the published x86 documentation is not adequate for compatible design, design houses for x86 processors must make a large investment in time to develop extensive compatibility test suites. These suites are used to compare their parts against the de facto standard Intel x86 microprocessors. The compatibility suites exercise the functionality of individual instructions and inter-instruction interactions. Many tests are written that create result arrays in memory. Comparison of the result arrays for the microprocessor with the device under test, is more efficient than tests that require comparison of register values. Subsequent to such tests, compatibility testing includes extensive trials of major applications and operating systems. Comprehensive system tests are also performed using a wide range of peripherals. After much internal testing, outside compatibility laboratories are employed to give independent certification, and hence added credibility that the microprocessor is indeed compatible.

Clearly part of the difficulty in compatibility testing stems from x86 architectural complexity, particularly in the context of high-performance implementations, which act to further complicate compatibility testing. Some x86 architectural complexity issues are well known. These include the existence of complex instructions with variable-length instructions, non uniform instruction decoding, many address modes and inherently multiple cycle operations; a segmented addressing model, requiring con-

compatibility test suites

tinual effective and linear address calculations; precise interrupts; and IEEE compatible floating-point.

The foregoing well-known complexity issues are just the beginning. Beyond these are many more problems. Historically, x86 programmers have exploited the use of self-modifying code. Compatibility requires close monitoring for store-into-instruction stream events and extensive design efforts to ensure instruction cache coherency, which must extend over multiple levels of cache hierarchy, deep into the branch prediction, prefetch, and instruction decode logic. The x86 has multiple operating modes, including real-mode, virtual 86 mode, segmentation without paging, and segmentation with paging. Paging involves a 2-level translation with a TLB and also introduces additional user and supervisor-like protection features. Beyond addressing issues, segmentation has extensive protection model features, including the use of selectors and segment descriptors, call-gate transitions between protection levels, task-gate transitions between tasks, protected stack operations, and virtualized I/O. Miscellaneous x86 complexity that complicates compatibility testing stems from the existence of a "System Management" mode for facilitating system power management, instruction prefix operations, non uniform register operations (8-bit, 16-bit, and 32-bit operations), and the implicit instruction use of dedicated registers.

Because the K6 3D executes x86 instructions directly, a significant compatibility effort was undertaken from the very beginning of the project to ensure its x86 binary code compatibility. Its verification included all of the steps above plus validation for several major operating systems environments. Some of the validation steps were simplified because of tools and experience in building three earlier generations of x86 processors, but no steps were omitted..

VIDEO ON THE COMPANION CD-ROM

There is a video interview on the CD-ROM with Warren Stapleton, Leader of Model Development and Verification of the K6 3D and Anu Mitra, Verification Manager of the K6 3D in which they discuss the design process employed and the extensive role verification played in the project from its inception.

#### DEFINING A PROCESSOR'S INSTRUCTION SET ARCHITECTURE

The genesis of a processor's instruction set architecture is often quite informal in nature—ranging from discussions where diagrams are drawn on backs of envelopes to talking one or two people into writing a report or a white paper discussing what might be done.

# **Historical Comment and Suggested Reading**

#### The von Neumann Machine

Two of the most significant papers in the history of computer architecture are related to what is called the "von Neumann machine." They are:

- 1. John von Neumann, "The First Draft of a Report on the EDVAC," Moore School of Electrical Engineering, University of Pennsylvania, June 30, 1945, republished in the IEEE Annals of the History of Computing, 1993.

- 2. Arthur W. Burks, Herman H. Goldstine, and John von Neumann, "Preliminary Discussion of the Logical Design of an Electronic Computing Instrument," report prepared for U.S. Army Ordnance Dept., 1946, reprinted in Datamation, Vol. 8, No. 9, pp. 24-31, September 1962 (Part I) and Datamation, Vol. 8, No. 10, pp. 36-41, October, 1962 (Part II).

An interesting augmentation to the von Neumann paper cited above can be found in:

3. M. D. Godfrey and D. F. Henry, "The Computer as von Neumann Planned It," IEEE Annals of the History of Computing, 1993.

An historical account of RISC technology within IBM, a good deal of which is relevant to topics discussed in this book, can be found in:

4. John Cocke and V. Markstein, "The Evolution of RISC Technology at IBM," IBM Journal of Research and Development, January 1990.

Complete full-text versions of *each* of the above important, historical articles can be found on the companion CD-ROM. We encourage you to read each of them.

> These modest beginnings often lead to forming a small group of people to undertake both analytical studies and simulations to explore the feasibility of some of the newer concepts inherent in the design, to define some aspects of the instruction set architecture with a bit more rigor, to examine the implications of a number of the design constraints. If the results of these efforts are promising, a project to design and implement the processor is typically launched, consistent with available resources. It should come as no surprise that a microarchitecture also evolves in a similar way to an instruction set architecture.

> There are a wide variety of factors that influence the nature of the processor's instruction set and the candidate microarchitectures for implementing the resultant instruction set architecture.

Some of the higher-level issues are:

- 1. target applications and operating systems.

- 2. target platform context—e.g., desktop, portable, or server.

- 3. target cost/performance level.

- 4. need to support legacy 16-bit and 32-bit code.

Some of the lower-level issues are:

- 1. target die size and cost.

- 2. target platform/system environment—e.g., external caches, bus speeds, and I/O speeds.

# **Suggested Readings**

#### **Instruction Set Design**

Consider what Michael Flynn on pp. 2-3 in *Computer Architecture*, *Pipelined and Parallel Processor Design*, Jones and Bartlett, 1995 has to say about instruction set design:

"There are always trade-offs in instruction set design. A well-designed instruction set allows variability in implementation technology and is less sensitive to technology changes. As time goes by, even a well-designed set must undergo changes—additions to accommodate new functionality and perhaps a de-emphasis of older features. Thus, at any moment, a successful architecture includes an instruction set consisting of:

- A core of frequently used instructions.

- Some features extending or correcting limitations in the original design.

- Some instructions no longer expected to be used (either superseded or "out-of-vogue"), which remain for reasons of compatibility."

Also, consider Harold Stone's related comments on p. 9 in *High Performance Computer Architecture*, 3rd Edition, Addison Wesley, 1993:

"... The architect should measure the quality of the architecture across a number of applications that characterize how an architecture is to be used. The effectiveness may vary considerably from application to application, and such measurements should reveal where the architecture is truly beneficial to the user and where other approaches are superior.

A computer architecture might well have some minor but costly inherent flaws that escape the scrutiny of its designer. A different designer who can build essentially the same architecture with those flaws repaired can produce a more effective, and therefore more competitive, machine. Architects cannot hide inefficiency by arguing that hardware costs nothing."

Some typical design decisions that need to be made are:

- 1. will the design focus on employing multiple parallel pipelines or fewer, deeper pipelines—i.e., a maximum superscalar versus a maximum frequency approach.

- 2. how many instruction decodes/clock.

- 3. how many functional units and how deeply will they be pipelined.

- 4. how will functions be apportioned or assigned to each pipeline stage.

- 5. what type of caching.

The models employed by the hardware/system co-design teams need to be flexible enough and detailed enough to allow alternatives to this wide range of design issues to be evaluated.

#### MODEL OF THE MICROPROCESSOR AT THE RTL LEVEL

There has been a rich history of the use of both formal and informal textual and graphical representations of computer architecture. In the following extended Historical Comment, Dr. Mario Barbacci of CMU shares some of that history with us.

#### HISTORICAL COMMENT

The Evolution of Architecture Description Languages by Dr. Mario Barbacci **CMU**

Designers and students of computer architectures have always made use of graphical and textual conventions to describe computer architectures. Early notations varied in their degree of formality and descriptive power and were not in widespread use (for reasons that will become apparent later). A significant event in the evolution of architecture description languages took place in 1964 with the publication of a formal description of the recently announced IBM SYSTEM/360 [5]. This description provided a definition for a computer architecture namely, the behavior and the state visible to the programmer:

"This paper presents a precise formal description of a complete computer system, the IBM SYSTEM/ 360. The description is functional: it describes the behavior of the machine as seen by the programmer, irrespective of any particular physical implementation, and expressly specifies the state of every register or facility accessible to the programmer for every moment of system operation at which this information is actually available."

continued on next page...

#### The Evolution of Architecture Description Languages

The description of SYSTEM/360 consisted of a set of programs in APL [7] organized in two sections, the central processing system (nine programs) and the input/output (five programs). The programs were complemented with auxiliary tables that provided, for example, definitions of variables and locations (line numbers) in the programs where the variables are read or written. The legendary terseness of the language makes a study of the description a slow process at best, and the process is not helped by the naming conventions (e.g., "For brevity, single characters are used for all variables except for those which occur infrequently, such as the panel switches occurring in CP, the control panel program.") Nevertheless, this is a milestone in the evolution of Architecture Description Languages and must read for any serious student of the subject.

As integrated circuits increased in density during the 1960's, new computers began to proliferate and it was possible, for the first time, to collect, study, and classify these artifacts, just like one could study plants or animals or rocks. The publication of [3] was the first attempt to organize computer structures into levels, represented with uniform notations:

"The structures that we call computer systems continue to grow in complexity, in size, and in diversity. This book is linked firmly to the nature of this growth. The book is about the upper levels of computer structure: about instruction sets, which define a computer system at the programming level; and about organizations of processors, memories, switches, input-output devices, controllers, and communication links, which provide the ultimate functioning system. These levels are just emerging into well-defined system levels, with developed symbolic techniques of analysis and synthesis and accumulated engineering know-how, all expressed in a crystallized representation."

The book provided a large collection of detailed examples illustrating actual computers. The authors felt that a sufficiently large number of computers had been designed over the previous 25 years that it was possible to systematize the space of computer designs, to provide a framework for the study of computers as a class of artifacts and not as isolated, independent inventions.

The framework consisted of a hierarchy of levels of descriptions complemented by two notations, one for instruction sets, called ISP, and the other for configurations of major components, called PMS.

According to [3] a digital system can be described at many different levels of detail in order to depict structural or behavioral aspects. Thus a system can be described at the gate level as a network of logic gates and flip-flops whose behavior is specified by timing diagrams, Boolean equations, or truth tables. While a complete digital computer could be described at this level, the amount of information to be conveyed would be too extensive for a human designer to comprehend, and higher levels are introduced to abstract details: Combinatorial and Sequential Register Transfer levels.

The existence of digital components capable of interpreting instructions stored in memory (i.e., instruction set processors) motivated Bell and Newell to introduce the programming level of description.

continued on next page...

#### The Evolution of Architecture Description Languages

At the programming level, the basic components are the interpretation cycle, the machine instructions, and operations (all of which are defined as register transfer level operations). The programming level arises from the need to describe the behavior rather than the structure of processors—in particular the behavior as seen by the programmers of the machine (i.e., the goal of Falkoff et al, in the SYSTEM/360 description)

The system levels correspond closely to the technology available for analysis and synthesis of computer systems. During the 1940's and 1950's computer architectures were simple, often linked to one unique implementation, and the need for a description language were satisfied by logic diagrams and Boolean equations. The situation changed with the introduction of SYSTEM/360 because it consisted of a large family of implementation of the same instruction set—the architecture had to be abstracted from the implementation, thus the need for a different notation. In 1971, Bell and Newell characterized the situation thus,

"Each of these levels exists in fact, precisely to the extent that a technology has become well developed. Thus both the circuit level and the lower half of the logic level (combinatorial and sequential circuits) are highly polished technologies. They are what one learns today, if one wants to become a computer engineer. Textbooks exist, courses are taught, and there is a flourishing, cumulative technical literature. As we progress up the systems levels, matters become progressively worse. The register-transfer level is not yet well established, although there is considerable current activity and the next few years may see its universal establishment."

No such consensus was apparent at the programming or system levels although the increased complexity of computer systems was increasing the importance of these higher levels.

One decade later technology advances had led to an explosion in the number of computer types, with a large number of instruction sets and data types, as reflected in a revised and expanded version of [3]. By the time [8] was published, the programming level of description was firmly established and the leading notation, ISPS, a formally defined programming language, based on the original ISP notation had been used in a variety of analysis and synthesis applications. In ISPS [1] a processor is described by declarations of carriers and procedures specifying the behavior of the system:

- 1. information carriers registers and memories used to store programs, data, and other state information.

- 2. instruction set procedures describing the behavior of the processor instructions.

- 3. addressing modes procedures describing the operand and instruction fetch and store operations.

- 4. interpretation cycle typically, the main procedure of an ISP description. It defines the fetch, decode, and execute sequence of a digital processor.

continued on the next page....

#### The Evolution of Architecture Description Languages

The PMS notation remained a graphical language for describing uniprocessor structures but never evolved to the point of being formalized and implemented as a serious design tool.

The story was very different at the lower levels of detail, where a number of notations known collectively as "Hardware Description Languages" continued to be developed and used. Hardware Description Languages (HDL) are notations and languages that facilitate the documentation, design, simulation, and manufacturing of digital computer systems [2]. Most of these languages (see suggested reading material) were used mostly in research and academic environments, as input notations for experimental simulation, analysis, or synthesis tools. In the industrial world, however, additional requirements had to be considered, namely the need to create, modify and support many design and manufacturing details across manufacturers and throughout the product's lifecycle.

To address these requirements, several industry-supported efforts have led to standard formats to represent product data in a standard format. Two of these efforts were the Very High Speed Integrated Circuits Hardware Description Languages (VHDL) [6] and the Electronic Design Interchange Format (EDIF). VHDL and EDIF became standards in 1987 (IEEE Standard, 1076 and EIA RS44 respectively) [4].

In VHDL each hardware entity has an interface and a body or architecture. The interface descriptions consist of input and output ports and various attributes associated with the interface, such as pin names, timing constraints, etc. The body describes the function or the structure of the design. The body may be written as an algorithm or as a combination of algorithms and real hardware representations (e.g., gates, arithmetic-logic units) or made up totally as a structure of real hardware representations.

EDIF provides a hierarchical syntax for data necessary for chip and printed circuit board fabrication. Note that EDIF is a format, not a language. EDIF's primary application is as a means of transferring design data from the design environment to the fabrication environment. The format provides for libraries, cells, views, interfaces, and information on the content within each cell. Test data, mask layout data, physical layout data, connectivity data, and simulation data can be represented in EDIF.

These various standards attempt to answer the needs of the various product life-cycle activities. However, the development of these standards have not been coordinated, and users still need a thorough understanding of the objectives and uses of each standard. The technology of HDLs has not matured to the point that a standard language or format can satisfy the wide diversity of product description requirements, at least for the foreseeable future.

By the early 80's, the dimensions of an emerging level, the network level, were noticed. It had the character of a different level because the performance of a network was far more dependent on operating systems, network topology, protocols, bandwidth, than on the instruction sets of individual processors.

At the time of this writing, 15 years after [8], an explosion on the number of network types, protocols, and communications has taken place. Millions of personal computer users connected to intranets and the Internet have created an enormous demand for new technology. The technology is changing so rapidly that it will be a while before "the level" begins to settle down and "the notation" emerges.

continued on the next page...

#### References: The Evolution of Architecture Description Languages

- 1. [Barbacci 81] Mario R. Barbacci, "Instruction Set Processor Specifications (ISPS): The Notation and its Applications," IEEE Transactions on Computers, C-30, 1, (January), 1981.

- 2. [Barbacci 93] Mario R. Barbacci, Ron Waxman, "Hardware Description Languages," in Encyclopedia of Computer Science, 3rd Edition, Anthony Ralston and Edwin D. Reilly (Eds.), Van Nostrand Reinhold, 1993.

- 3. [Bell and Newell 71] C. Gordon Bell and Allen Newell, Computer Structures: Readings and Examples, McGraw-Hill Book Company, 1971.

- 4. [EDF 87] EIA/EDIF/IS-44 Specification, Electronic Design Interchange Format, Version 2.0.0, May 1987.

- 5. [Falkoff 1964] A.D. Falkoff, K.E. Iverson, E.H. Sussenguth, "A formal description of SYSTEM/ 360," IBM Systems Journal, Vol. 3, No. 3, 1964.

- 6. [IEEE 87] IEEE, "VHDL Language Reference Manual," Standard 1076, December 1987.

- 7. [Iverson 62] Kenneth E. Iverson, A Programming Language, Wiley, 1962.

- 8. [Siewiorek 82], Siewiorek, Daniel P., Bell, C. Gordon and Newell, Allen, Computer Structures: Principles and Examples, McGraw-Hill, 1982.

#### Additional Readings: The Evolution of Architecture Description Languages

- Mario Barbacci, "A Comparison of Register Transfer Languages for Describing Computers and Digital Systems," *IEEE Transactions on Computers*, Vol C-24, No. 2, February 1975, pp. 137-150.

- 2. Robert Piloty, Mario Barbacci, Dominique Borrione, Donald Dietmeyer, Fredrick Hill, Pat Skelly, "CONLAN Report," Lecture Notes in Computer Science, 151, Springer-Verlag.

- 3. Yaohan Chu (Guest Editor), special issue on Computer Hardware Description Languages, Computer, Vol. 7 No. 12, December 1974, pp. 18-22.

- 4. Stephen Y.S. Su (Guest Editor), special issue on Computer Hardware Description Languages, Computer, Vol. 10 No. 6, June 1977, pp. 10-13.

- 5. Mario Barbacci and Takao Uehara (Guest Editors), special issue on Computer Hardware Description languages, Computer, Vol. 18 No. 2, February 1985, pp. 6-8.

- 6. Allen Dewey (Guest Editor), "VHDL and Next-Generation Design Automation," Guest Editor's Introduction to IEEE Design and Test of Computers, Vol. 9, No. 2, June 1992, special issue on VHDL.

- 7. "Three Decades of HDLs," Collections of short notes by various authors: Part 1, "CDL Through TI-HDL," IEEE Design and Test of Computers, Vol. 9, No. 2, June 1992; Part 2, "CONLAN through Verilog," IEEE Design and Test of Computers, Vol. 9, No. 3, September 1992.

Among the important issues to consider when modeling a microprocessor are: what the model will be used for, the type of model required and its representation, the ease of use of the model, and cost. The specific level of abstraction is selected consistent with the goals of the modeling effort. It is not only important to decide how the logic and circuit designs of the actual microprocessor are going to be represented but also how the "simulation environment" within which the microprocessor will be "exercised" will itself be designed and implemented. This is the part of the system that generates stimulus for the model and checks that it is behaving properly. For a microprocessor, the simulation environment must be able to display and check the state of various conditions within the processor and it must accommodate such things as distributing clock signals and modeling of the main memory and system bus architecture and protocols. A software simulator may be coupled to various hardware emulators to form a hardware/software co-simulation environment.

Modeling is a compromise between accuracy (the level of representation, the details described, and the precision with which they are described) and speed. An accurate model of a microprocessor at the physical level would have to model physical device characteristics. A simulation of such a model would be so slow that it would be completely useless for functional compatibility tests. Moreover, there needs to be a tool that can be used to conveniently describe a microprocessor's complex behavior and structure. Specialized high-level programming languages have evolved to meet this need.

# **Suggested Readings**

#### Full-Custom and Semi-Custom Design

From page 3 of the book by Ulrich Golze, (with Peter Blinzer, Elmar Cochlovius, Michael Schafers, and Klaus-Peter Wachsmann), *VLSI Chip Design with the Hardware Description Language VERILOG*, Springer, 1996, which was mentioned earlier, we have:

"In full-custom design, all details of the circuit had now to be designed, the transistors had to be dimensioned and composed to meaningful geometrical layouts which were afterward verified by an analog simulator. A layout is a true-to-scale template for the structures to be produced, however strongly enlarged. ... Around the middle of the 1980s, semi-custom design style became the workhorse of VLSI design. With the user interface again moving upward, the semi-custom design employs optimized library cells, typically logic gates, adders, etc., composes them to logic wiring diagrams (gate netlists, schematics) and simulates them logically. The transformation into a geometric layout is achieved by efficient placement and layout programs. The designer, in general, is not involved with single transistors, he often does not even know the internal structure of the library cells used."

There is substantial debate in the industry about the adequacy of current hardware description languages to handle system-level designs, behavioral and logic synthesis, simulation, and formal verification. See for example, "DAC 97 Panel: Next-Generation HDLs," by L. Lavango and N. Collins, IEEE Design & Test of Computers, July-September, 1997, Vol. 13, No. 3, p. 7.

Programming languages, extended to include notions of time, parallelism and synchronization, and architectural and hardware data structure extensions, have emerged to dominate in semi-custom design. Such languages are called hardware description languages or HDLs. A model, which is the definition of the microprocessor implemented as a program in the HDL, can be simulated by compiling and executing it. Since the program can be written to describe the microprocessor at any level of abstraction, the simulation will be of the microprocessor at that particular level.

#### GOLDEN REPRESENTATION

The HDL description becomes the "golden representation" of the microprocessor. Changes are made to the golden representation, and all other representations must change to match the golden representation. The flow of change is one way, starting with the golden representation. When this representation becomes detailed enough, it can be transformed by a process called *logic synthesis* to be input to the layout and placement stage of the design process.

Independent descriptions of the microprocessor can be made for each level of abstraction. Beginning with its behavioral description and employing step-wise refinement to model more and more of the underlying structure, one could extend the description down to the gate level. These lower-level design representations must be "cross-verified" against the *golden representation* to ensure they are functionally equivalent. Cross-verification is necessary mainly when the lower-level representations are generated in part or totally by hand. If they are completely machine-generated, cross-verification is less necessary unless the software tools that generate the lower-level representations are suspect.

#### ARTICLES ON CD-ROM

A full text version of "Introduction to High-Level Synthesis," by Daniel D. Gajski and Loganath Ramachandran, *IEEE Design & Test of Computers*, Winter 1994 can be found on the companion CD-ROM. Two related articles, "Specification and Design of Embedded Hardware-Software Systems," by Daniel D. Gajski and Frank Vahid, *IEEE Design & Test of Computers*, Spring 1995 and "Introduction to the Scheduling Problem," by Robert A. Walker and Samit Chaudhuri, *IEEE Design & Test*, Summer, 1995 are also on the CD-ROM.

A growing number of digital system designs are currently represented in one of two popular hardware description languages, Verilog or VHDL. Selecting one over the other is seen by some as mostly a matter of religion. However there are some concrete reasons why one might be better suited to a particular design than the other. If Verilog was to be compared to C, then it might be reasonable to say that VHDL is like C++. VHDL is a much more complex language that allows practically all aspects of its definition to be redefined. In most cases VHDL is used with standard packages that define the operators to work in the most logical and expected fashion. A typical complaint is that VHDL is difficult to learn and is a verbose language. Some authors state that one advantage of VHDL is that its simulation semantics are reasonably well defined; thus, most vendors' simulators for VHDL behave exactly the same. However, we caution that the same can be said about Verilog simulators noting that they are based on a de facto definition as evidenced by the Verilog simulator of Cadence Design Systems, Inc. VHDL is the accepted HDL used for military applications and also is often used for describing extensible libraries. On the other hand, Verilog has gained widespread acceptance because it is easy to learn and many consider it more practical. Many engineers say they were able to use Verilog in just a few days. The Verilog language looks familiar because it is like a combination of Pascal and C mixed together with additional constructs to represent hardware design and simulation semantics.

# BEHAVIORAL (FUNCTIONAL) SIMULATION

Unfortunately, hardware designs, like software designs, usually have some errors (bugs). For a complex design like a microprocessor, there are likely to be thousands of bugs that have to be identified and fixed throughout the design process. Obviously any speedup in the process of identifying bugs will shorten the entire design cycle. Simulators typically provide mechanisms for displaying selected design variables, either every cycle or when they change value. This information can be used by other tools that allow the data to be displayed in a more convenient and meaningful manner as either waveforms or state dumps. There are two basic styles of writing simulators to study the behavior of a particular model—cycle-based and event-driven. Cycle-based simulation corresponds to examining model variables "every cycle" whereas event-driven simulation corresponds to examining model variables "when they change."

One of the problems with describing and simulating hardware is that hardware can execute a number of things in parallel. However, these items are resolved at different stages of execution in a simulator. For example, a 3-input AND gate may have only two inputs ready when the simulator has reached the stage of executing the model that represents the AND gate. This means that the evaluation of the AND gate will not produce the final result and will have to be evaluated again once the 3<sup>rd</sup> input is ready.

cycle-based simulation

#### DESIGN NOTE AND SUGGESTED READING

#### Using C++ as an HDL

The K6 family of microprocessors requires a rather large systems-based simulation environment. The team decided that contemporary hardware description languages were not good for the general purpose programming that would be required. They chose to model the microarchitecture using C++ and to then take advantage of this general purpose programming language to represent the entire model (i.e., the design plus the simulation environment). There were a number of advantages to using C++:

- 1. object-oriented nature: The object-oriented nature of the C++ programming language allowed the team to define an elegant way to represent the logic of the design, and was flexible enough to generate complex models of expected behavior.

- 2. *ability to override operators*: One main advantage that HDLs have over programming languages is their ability to manipulate individual bits of data. To overcome this limitation the operator() function was overridden to represent bit and part selection.

- 3. expressiveness: It was possible to write equations in the form of "signal 1(3,2) = signal 2(1,0)" or "signal 1 = signal 2 & signal 3" which are just as convenient as using one of the hardware description languages.

- 4. speed: The K6 3D simulator needed to be very fast. This was another key reason for choosing a compiled language. Minimizing the amount of time to debug a problem, making a modification, recompiling, and verifying that the problem is indeed fixed was key to the success of the project.

- 5. *debugging aids*: design assertions and instrumentation code were easily included in the simulator.

- 6. execution in desktop PCs: ability to run simulations of large systems on desktop PCs and workstations with relatively modest amounts of main memory as well as on servers.

- 7. quick development loop: relatively fast simulate-debug-change-compile loop compared to typical HDL environments.

For a discussion of related issues related to the use of "traditional" programming languages as HDLs, see the article, "Using a Programming Language for Digital System Design," by R. K. Gupta and S. Y. Liao, IEEE Design & Test of Computers, April-June 1997 on the book's companion CD-ROM.

In this video clip, Amos Ben-Meir, Principal Designer of the K6 3D, addresses the question, "Was software simulation used in the verification of the K6 3D?" and Warren Stapleton, the K6 3D's Leader of Model Development and Verification, addresses the question, "Why did the K6 3D team choose to use its own proprietary modeling and simulation tools?"

Given the importance simulation plays in the design and implementation of microprocessors, we have included three simulators on the CD-ROM. In Chapter 3, we give pseudo-RTL descriptions that describe various chunks of microarchitecture logic and recommend the reader simulated them on these simulators.

In *cycle-based* simulation many things (e.g., register loads and signal transitions) can occur in parallel. These actions are "flattened and re-ordered" in order to create the effect of all events occurring in their proper order. Cycle-based simulation eliminates the need to re-evaluate sections of code due to having unresolved terms. Again, this is done by flattening and re-ordering so that everything computes and resolves in one pass through the simulator. In a cycle-based simulation, there are inputs defined and expected outputs derived for every cycle. Cycle-based simulators have difficulty in dealing with multiple clock domains and generally cannot deal with delay simulation at all.

Event-driven simulators take the approach of re-evaluating models every time there is an event on one of the inputs or variables of the model. It is easier to handle multiple clocking domains with this type of simulator, as well as delay simulation. The disadvantage is that this type of simulator is generally slower than cycle-based simulators.

Cycle-accurate model refers to a model describing the behavior of a functional unit down to the cycle level. This means that the functional unit's behavior is modeled accurately enough so that the model's pins behave identically to the "real thing" on a cycle-by-cycle basis. This allows generating test vectors from the model so that the "real thing" can be verified with these. An example of a model that may not be cycle-accurate is a performance model. A performance model may only approximate the cycle behavior since its purpose is to gauge the performance of the functional unit within some range of accuracy.

As mentioned earlier, one of the most important uses of simulators is to verify the behavior of and to debug the system being modeled. event-driven

cycle-accurate

#### HISTORICAL COMMENT

## Verification Technology

From P. Shepherd, *Integrated Circuit Design, Fabrication, and Test*, McGraw-Hill, 1996, pp. 120-121, we learn:

"Before software tools were developed, the verification of a particular circuit design could only be achieved by constructing a prototype circuit. While the design could use standard digital and analogue techniques to design the circuit on paper, it was almost impossible to determine whether the circuit would perform as expected to in practice. .... When built, the circuit would be thoroughly tested and design modifications made on the basis of these tests. The next version of the process was then constructed and the process repeated. Such a technique was very time-consuming and expensive. .... Redesign and rework of the mask set added further delay and expense to the product development."

Debugging a design usually differs significantly from debugging a program. When writing programs, source level debug tools that allow the code to be single stepped while examining individual variables are key to

boosting debug productivity. Although this capability is available in some simulator environments it is not used that often. A good environment for debugging a design should provide fast access to all of the key signal values, in a logically formatted display, after each cycle has completed. Also, many simulators keep a history of selected variables so that one can step backwards in time from an erroneous state to determine the events that forced the system into that state. Keeping in mind the simplicity of most hardware description languages, the bugs are more likely to be conceptual in nature rather than simple coding errors.

#### MODEL AT THE GATE AND CIRCUIT LEVELS

Gate-level models are models that describe the function of a particular block or chip at the gate level. A gate is generally a basic building block of the design that implements a simple Boolean function. The gates are then connected together to create a more complex functional unit. Circuit-level models are typically models that go one level below the gates (i.e., to the transistor level).

#### GATE AND CIRCUIT LEVEL SIMULATION AND HARDWARE EMULATION

The simulation models for the basic gates are generally part of a gate library that contains multiple representations of these gates (in chip design, this is typically layout, timing models, ATPG models, transistor level netlist/schematic and simulation models). When doing gate-level simulation, the functional unit being simulated must already have a netlist with a gate implementation. This netlist can then be simulated with one of the multiple commercial simulators or proprietary in-house simulators.

When doing functional simulation with circuit-level models (transistor-level models), there is usually an abstraction phase where the transistors are translated into gates and then these gates are simulated. This is done to improve the speed of transistor level simulations. There are simulators that are able to simulate at the transistor level, treating the transistor as a 3-node switch and computing the values on each node. This is typically very slow and requires much compute time. In addition, many transistor topologies that have analog behavior do not lend themselves well to switch-level simulation—i.e., it is difficult for the simulator to resolve what the circuit is doing. These analog sections typically require creation of simple RTL or gate models to describe their logic behavior.

#### ARTICLES ON CD-ROM

Full text versions of two articles that deal with the topics discussed in this subsection: see "Circuit Techniques in a 266-MHz MMX-Enabled Processor," by Donald A. Draper, Matt Crowley, John Holst, Greg Favor, Albrecht Schoy, Jeff Trull, Amos Ben-Meir, Rajesh Khanna, Dennie Wendell, Ravi Krishna, Joe Nolan, Dhiraj Mallick, Hamid Partovi, Mark Roberts, Mark Johnson, and Thomas Lee, IEEE Journal of Solid-State Circuits, November 1997 and "An x86 Microprocessor with Multimedia Extensions," by Donald A. Draper, Matthew P. Crowley, John Holst, Greg Favor, Albrecht Schoy, Amos Ben-Meir, Jeff Trull, Raj Khanna, Dennie Wendell, Ravi Krishna, Joe Nolan, Hamid Partovi, Mark Johnson, Tom Lee, Dhiraj Mallick, Gene Frydel, Anderson Vuong, Stanley Yu, Reading Maley, and Bruce Kaufmann 1997 ISSCC Digest of Technical Papers. You can find the full text versions of both of the above articles on the companion CD-ROM.

#### **DEFINITIONS**

#### Co-simulation and Co-verification

Co-simulation and co-verification are terms generally used to describe a situation where two different types of models (gates and RTL for example) are simulated together. Both models receive identical stimulus, then their outputs are compared on every cycle to guarantee that the two models behave identically. The goal of this type of simulation is to prove functional equivalence between two representations of a design.

Hardware emulation is the process of taking a functional unit netlist or a full-chip netlist and building it in some form of real hardware, such as FPGAs and memories. Then that hardware can be plugged into a real system for testing (though at fairly low frequencies, 100's of KHz or a few number of MHz). The hardware can also be used as a very fast simulator provided there is an environment that allows passing stimulus to the emulator and receiving the outputs from the emulator and then comparing the outputs with expected results to check for correctness.

hardware emulation

One of the goals of emulation is to provide a way to run the design in a real-world environment. Usually this means being able to plug the emulator into the actual socket that the chip will plug into and using the complete final product as if it had a real chip installed. This goal can be achieved in several different ways. One approach is simply to build an extremely fast simulator using parallel processors to get the required speed. The more traditional approach is to use a large number of interconnected FPGAs (Field Programmable Gate Arrays) and program them with a version of the gate-level netlist of the design.

#### **DESIGN NOTE**

# Using Emulation in the Design and Testing of the K6 Family of Microprocessors

Hardware emulation was one of the keys to the success of the K6 project. The team programmed interconnected FPGAs with a version of the gate-level netlist of the design. They used the commercially available Quickturn emulation system to do this. What made the K6 emulation unique was that the team was able to get the gate-level design working quite some time before the initial fabrication of the chip. Prior to committing the design to manufacturing they were able to initialize and run all of the available x86 operating systems and run a significant number of standard applications, thus proving their design and its compatibility very early in the design cycle.

In addition to finding a handful of obscure bugs that probably would not have been found with conventional simulation, they were able to verify the built-in engineering debug features of the chip that would have required too many cycles to verify with the C++ model.

There were also some intangible benefits of emulation: The emulation lab provided experience for a multi-disciplined team that included BIOS developers, system experts, and chip designers. This experience was valuable when silicon returned from the fabrication facility. When the team booted the Windows 95 Operating System for the first time in the emulation laboratory the event gave an additional boost to the morale of the entire development team, which helped them get through the last few months before chip tapeout.

#### GENERATE NETLISTS AND PHYSICAL LAYOUT

The gates described at the behavioral level are selected from a library of cells which have been created for optimal realization of the logical functions in a particular process. These cells consist of nands, nors, inverters, flip-flops, latches, multiplexers, and other specialized cells. The first task is defining the physical and electrical characteristics of these cells.

The dimensions and pin placements of the cell needs to be expressed in multiples of the metal pitch, which is defined by the process capabilities. The routing pickup points likewise are determined by the metal pitch, and as many as possible should be placed in the cell to optimize the routing density. The power and ground supplies are designed to minimize the resistive drop to the transistors and to avoid creating excessively high current densities which could lead to early reliability failures due to electromigration. To avoid performance loss due to resistance in the diffusions of the transistors, many metal-to-diffusion contacts need to be used. This is still true even with modern diffusions which use a silicided layer for reducing resistance. Another characteristic of cell design is that the gate resistance combined with the gate capacitance causes a delay of the input signal from the pickup point to the other end of the gate represented by the transistor width. This delay increases as the square of the length of the gate over thin gate oxide. Furthermore, it is a characteristic of the silicidation process that narrower gates form the silicide poorly, resulting in a higher effective sheet resistance, which further aggravates the problem. For this reason, it is necessary to limit the maximum length of gate poly which can be done by using smaller transistors with many legs, by strapping out the poly, or by using pickup points in the center of the gate, between the n-channel and p-channel transistor blocks. All these things impair the routeability of the cell, which needs to be balanced against the performance loss of the poly resistance.

Next, the sizes of the n-channel and p-channel transistor blocks need to be defined. The optimum ratio for speed is in the range of 1.4 to 1.8, for p-channel width relative to n-channel. The switching point will be slightly less than  $V_{\rm DD/2}$ . This switching point should be the same for all gates, whether nands, nors, or other gates. This means that not all the available transistor width in the cell will be used, but this makes timing simulation using the static timing analyzer more accurate. Cells of different drive strengths are required for optimum timing, but for drive strengths beyond three or four times the minimum, buffer cells should be used. It is also possible to have all the cells have versions optimized for both rising and falling edges, although this will lead to an extensive proliferation of the number of cells.

The design of the flip-flops is optimized for speed and other characteristics, such as minimum hold time and setup time. Dynamic logic can be incorporated into the flip-flops to achieve a performance increase. Another specialized design is to put delay cells into the clock input path of the flip-flop to achieve cycle-stealing or delay transfer between critical paths. Similar strategies can be used with level-sensitive transparent latches. To facilitate testing and debugging, the flip-flops need to have scan designed in. This means adding extra logic and routing scan clocks and the scan data in and scan data out, all of which add cost and complexity. But, there is probably no other way to achieve a high level of fault coverage or to be able to debug the chip when there is a logical bug or a pattern sensitivity.

After building the cells, it is very important to characterize them for timing. The first requirement is to determine the maximum delays for the characterizing cell timing

frequency-limiting maximum-delay paths. This is done by simulating the cells with the typical process at nominal voltage and worst-case temperature. The propagation delay needs to be determined for each input to each output path or arc. The delay is simulated as a function of the output loading and the input transition time, and is commonly represented as a matrix from which the actual timing delay is interpolated or extrapolated. In the case of state-dependent delays for cells such as exclusive-or gates, the delay of one arc is dependent on the logical state of the other input. This cannot be known to a static timing analyzer, so the worst-case delay needs to be selected. In the case where there are simultaneously switching inputs, such as from a bus, the delay time is again affected. For example, in a nand gate, if all the inputs switch from low to high within a small specified time of each other, the output delay is significantly increased, as compared to the case in which only one input switches while the other inputs stay high.

It is also necessary to guarantee that min-path, or hold time requirements, are met. The simulation conditions use the fast process corner at high voltage and low temperature. In the case of state-dependent delays, the shortest delay needs to be selected. Similarly for simultaneously switching inputs, the condition for the fastest output needs to be considered. For example, in the case of the nand again, if all of the inputs switch at the same time from high to low, the load is pulled up by all the p-channel transistors in the nand gate, not just one of them.

The above analysis becomes much more complicated for complex gates such as and-or-invert (AOI) cells and all combinations of input timing need to be exhaustively simulated. Similarly, the logical function needs to be verified in comparison to the Verilog or behavioral model by running an exhaustive combination of all possible inputs. This is especially important for complex gates such as tristate drivers and for AOI gates.

#### Full-Custom Macro Blocks

The other major category of physical development involves the full-custom designed macro blocks, such as cache memories, register files, input/output drivers, phase-locked loop and clock distribution systems. As with the standard cells, these blocks need to have their timing characteristics and logical function thoroughly specified and verified. The timing is determined after design and layout of the macro blocks by extracting the capacitance of the nodes and resimulating. The functional verification is accomplished by simulating the circuit and comparing the outputs, vector by vector, with the behavioral model.

The design of arrayed structures, such as memories, requires speed to be balanced with the margin of bit-line signal at the sense amps. This is a very carefully balanced race condition, with the sense-amp strobe arriving not too early before the signal has developed on the bit lines and not too

hold-time requirements