# TR9C1710 GRAPHICS COLOR PALETTE

## PRELIMINARY

## SPECIFICATION

#### **DISTINCTIVE CHARACTERISTICS**

- o Combination Look-up Table and Triple Video DAC

- Directly drives single- and double-terminated

75-ohm transmission lines

- o Displays 256 colors from a palette of 256K colors

- o Asynchronous Microprocessor interface

- o Read and Write contents of Look-up Table

- o VGA, Super VGA, VESA, TIGA™, and 8514/A compatible with enhanced features

- o Unlimited access to Look-up Table; no need to wait for retrace

- o Unlimited access to Mask Register

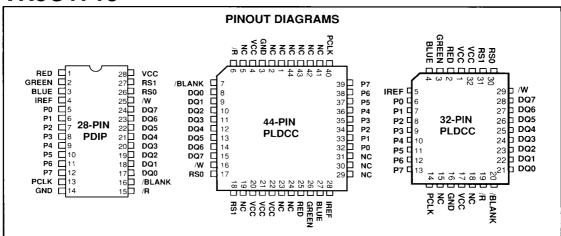

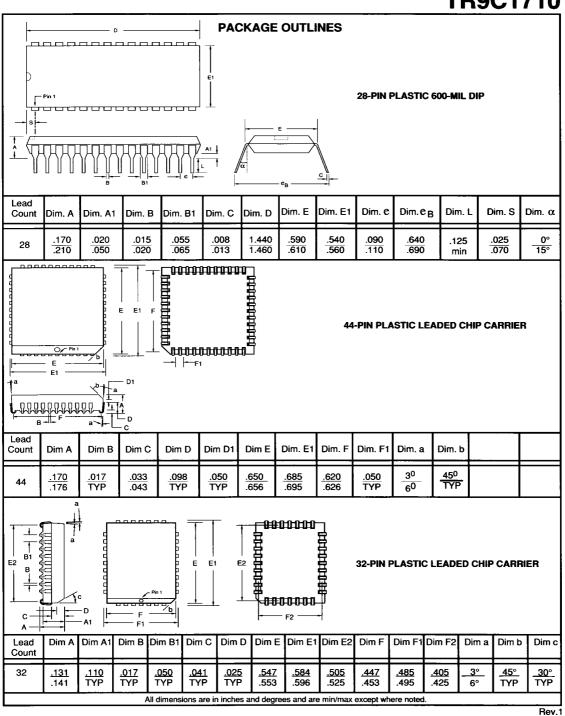

- o 28-pin PDIP and 32- and 44-pin PLDCC Packages

- o Available in 80-, 66-, 50-, and 35-MHz Pixel Rates

- High-Performance CMOS for low operating power

- o TTL-compatible inputs

#### **GENERAL DESCRIPTION**

The TR9C1710 is a monolithic 256-word by 18-bit Look-up Table and Triple Video DAC, with 6-bit DACs. The Look-up Table accepts up to eight bits per pixel from the Frame Buffer and performs a translation into three 6-bit values for conversion into Red, Green, and Blue analog signals. Each of the Video DACs can directly drive a double-terminated 75-ohm transmission line.

The TR9C1710 incorporates a proprietary feature called Pixel Replicate™ that allows both Read and

Write operations to occur to the Look-up Table when the display is active without causing random noise on the screen.

The TR9C1710 is available in standard 28-pin DIP and 32- and 44-pin PLDCC packages and supports the screen resolutions and color capacity necessary for high-performance Personal Desktop Computers and Workstation Graphics systems. The TR9C1710 is fully compatible with VGA and Super-VGA industry standards.

MUSIC™ Semiconductors reserves the right to make changes to this product without notice for the purpose of improving design or performance characteristics. Pixel Replicate™, MUSIC™, and the elements of the MUSIC™ logo are trademarks of MUSIC™ Semiconductors.

September 15, 1991, Rev. 1

#### **PIN DESCRIPTION**

#### Red, Green, Blue (Analog Outputs) (Note 10)

These signals are the outputs of the three video DAC's which drive doubly or singly terminated 75-ohm transmission lines and can directly drive a suitable monitor or video amplifier.

#### REF (Current Reference)

IREF provides a current reference for the TR9C1710's Video DACs. IREF must be driven by an external current sink providing a regulated current. Each current source in the DAC will contribute IREF/30 current to the output. The value for IREF is given by the equation:

$$IREF = \frac{30 \times V_{WHITE}}{63 \times R_{LOAD}}$$

#### P0-P7 (Pixel Address 0-7, TTL Input)

P0-P7 are registered on the rising edge of PCLK and are the addresses used to reference a color value stored in the Look-up Table for conversion to analog video signals. Individual Pixel Address bits are ANDed with the corresponding Mask Register bits.

#### PCLK (Pixel Clock, TTL Input, Rising Edge Active)

The Pixel Clock registers the Pixel Address (P0-P7), transfers data in the internal pipeline, and synchronizes the Microprocessor Port signals. Each Pixel Clock period corresponds to one pixel displayed on the monitor.

#### /BLANK (Blank Control, TTL Input, Active LOW)

The state of the /BLANK input is registered by the rising edge of PCLK. The /BLANK signal is used for blanking the display during retrace. With /BLANK HIGH, the DAC outputs reflect their digital input values. When /BLANK is LOW, the DAC

outputs are forced to the Blanking Level. /BLANK has the same pipeline delay as P0-P7.

#### /R (Read, TTL Input, Active LOW)

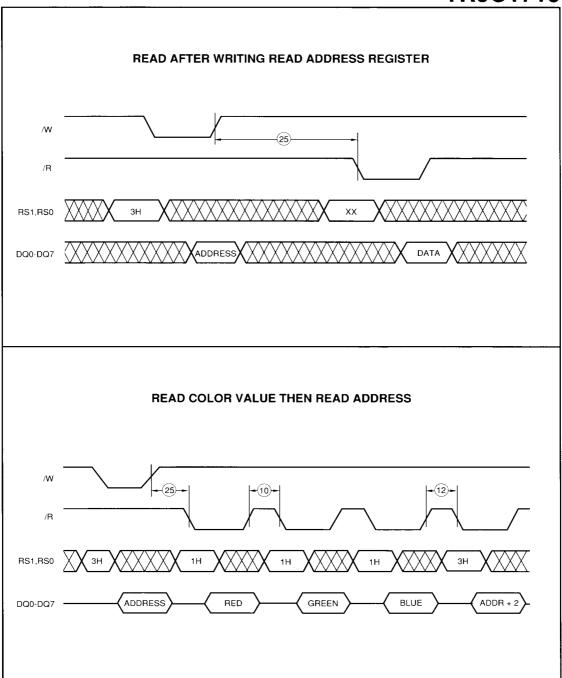

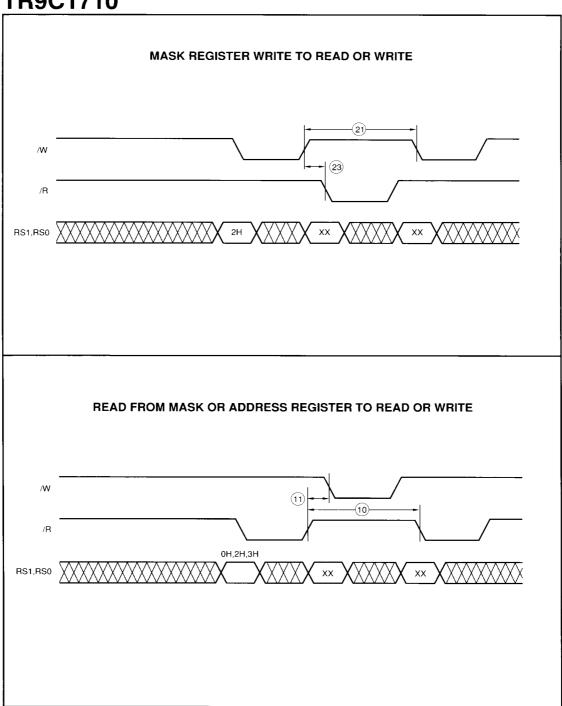

The Falling edge of /R registers the states of RS0-RS1, which are decoded to determine the source of the read data. The outputs become valid after the access time elapses from the falling edge of /R and high-impedance after the rising edge of /R.

#### /W (Write, TTL Input, Active LOW)

The Falling edge of /W registers the states of RS0-RS1, which are decoded to determine the destination for the write data. The input data must meet set-up and hold times referenced to the rising edge of the /W signal.

#### DQ0-DQ7 (Data Bus, I/O, Three-state TTL)

All Data transfers to and from the Microprocessor Port occur over DQ0-DQ7. The Mask Register and the Read/Write Address Register use all 8 bits, while Color Values use only the lower order six bits (DQ0-DQ5).

#### RS0, RS1 (Register Select 0-1, TTL Inputs)

The Register to be read or written during a Microprocessor Port cycle is determined by the state of RS0 - RS1 at the beginning of the cycle. The beginning of the cycle is initiated by the falling edge of either /R or /W, depending on the type of cycle. The chart below indicates the Register Assignments as a function of RS0 and RS1.

| RS1 | RS0 | Register Assignment                |

|-----|-----|------------------------------------|

| 0   | 0   | Pixel Address Register (RAM Write) |

| 0   | 1   | Color Value                        |

| 1   | 0   | Pixel Mask Register                |

| 1   | 1   | Pixel Address Register (RAM Read)  |

#### **FUNCTIONAL DESCRIPTION**

#### OVERVIEW

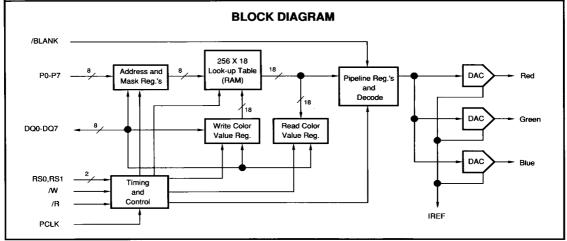

The TR9C1710 consists of a 256-word by 18-bit Look-up Table, a Mask register which is ANDed with the Look-up Table's address, a Triple six-bit Video DAC, along with the logic needed to implement a Microprocessor interface for accessing the Mask register and the Look-up table.

The TR9C1710 has three distinct sections. The first section consists of the Pixel address (P0-P7), /BLANK, and Pixel Clock (PCLK). The states of P0-P7 and /BLANK are captured at the rising edge of PCLK, corresponding to each pixel. The second section contains the 256x18 Look-up table (RAM) and the Video DACs used to drive an analog monitor. The third section contains the microprocessor port, which is used to access the Look-up table and Mask register.

#### VIDEO INPUT

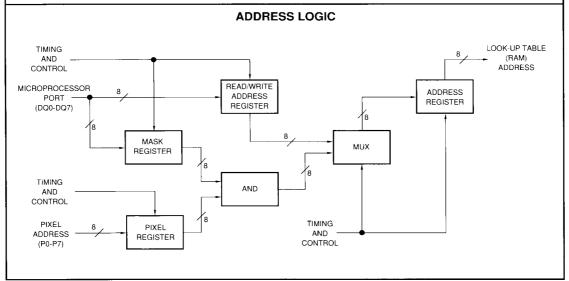

P0-P7 are ANDed with the contents of the Mask register and passed as an address to the Look-up table. The Mask register is fully synchronized. If the Mask register contains the byte value FFH, then the state of the P0-P7 is unaltered. If the Mask register contains 00H, then the Look-up table will be passed 00H. The contents of the location pointed to by the eight-bit address passed to the Look-up table is accessed with the 18-bit result transferred to the Video DACs.

The /BLANK (active LOW) input is used to blank the display during retrace. A LOW level on /BLANK will force the Video DACs to the Blanking Level without reference to the output of the Look-up table. A HIGH level on /BLANK will allow the output of the Look-up table to be converted into analog levels by the DACs. The pipeline delay for /BLANK is identical to the delay of the P0-P7 path through the Look-up table.

#### MICROPROCESSOR INTERFACE

The Microprocessor interface is used to access the Look-up table's RAM array (256 words of 18 bits). The TR9C1710 is designed to allow operations on the Look-up table at any time without waiting for retrace. Microprocessor Interface operations and Video Input cycles are synchronized with PCLK such that one Video cycle is borrowed for each 18-bit Microprocessor-interface-to-Look-up-table transfer (read or write). While this cycle is being borrowed, the data from the previous Pixel value is replicated at the DAC outputs. This feature, called Pixel Replicate™, eliminates the snow on the screen that can result from borrowing a Video cycle during active display time.

The eight-bit Mask register is programmed by the Host Processor by a Write cycle with RS0 = 0 and RS1 =1. The states of RS0 and RS1 are captured on the falling edge of /W and the state of the data bus (DQ0-DQ7) is captured on the rising edge of /W. The Mask register may be read by performing a Read cycle, again with RS0 = 0 and RS1 =1. The states of RS0 and RS1 are captured on the falling edge of /R, with the contents of the Mask register placed on the Data bus (DQ0-DQ7). The Data bus will remain active until after the rising edge of /R after which it will assume a high-impedance state.

The Look-up table is accessed by using the three registers: the Read/Write Address register (eight bits), the Color Value Write register (18 bits), or Color Value Read register (18 bits). Before any data can be placed into the Look-up table, the contents of the Read/Write Address register must be initialized by a Write cycle with RSO = 0 and RS1 = 0. The address is then placed on the Data bus. After the Read/Write Address register is initialized, the Color Value Write register

#### **FUNCTIONAL DESCRIPTION (CONT'D)**

is programmed with the information that is to be written into the selected address. This operation comprises three Write cycles to the Color Value Write register with RS0=1 and S1=0 and with the data on DQ0-DQ5. The first Write cycle is the Red field, followed by the Green and the Blue. After the third Write cycle (Blue), the contents of the Color Value Write register are written into the memory at the address in the Read/Write Address register, and the Read/Write Address register is incremented, allowing sequential addresses to be written without the need to rewrite the Read/Write Address register.

The contents of the Look-up table may be read by performing a Write cycle to the Read/Write Address register (RS0 =1 and RS1=1). The contents of the addressed location in the Look-up table are then accessed and placed in the Color Value Read register and the Address register is incremented. The contents of the Color Value Read register are then read by performing Read cycles with RS0=1 and RS1=0. The first Read cycle returns the Red field, followed by the Green and then the Blue on subsequent Read cycles. The data is output on DQ0-DQ5. After the third Read cycle (Blue Data), the address stored in the Read/Write Address register (already incremented) is accessed with its contents placed in the Color Value Read register. Sequential addresses may then be read without reprogramming the Read/Write Address register.

#### TRIPLE VIDEO DAC

The Triple Video DAC consists of three six-bit DACs capable of directly driving a doubly terminated 75-ohm transmission line (75-ohm termination resistors to ground at both ends of the line). Each DAC consists of 63 identical current sources, which are selected through a six-bit binary decoder resulting in 64 levels per DAC. With /BLANK LOW, the DAC output is the same as the Black level (all current sources off). The pipeline delay for P0-P7 is the same (four registers in the pipeline, three clock delays) as the delay for /BLANK.

The DACs may also be used to drive analog monochrome displays. One of the DAC outputs can be connected to the single video input of a monochrome monitor (see Note 10). If the video frame buffer contains information intended for display on a color monitor, the Look-up table can be reprogrammed to provide only the intensity portion of the color information. This technique allows the display of a digitized color frame in monochrome.

#### **APPLICATIONS**

The TR9C1710 incorporates two common graphics functions: a Look-up table and D/A Converters (in the form of a Triple Video DAC). The TR9C1710 provides a wide range of capabilities for a color or monochrome system. The TR9C1710 can display up to 256 colors at a time, each of which can be any combination of the 64 levels available from each of the three DACs. The TR9C1710 can display pseudo-color images where the various shades of a monochrome image are assigned unique colors, allowing image processing techniques, such as density slicing, to be

easily implemented on monochrome digitized images. Density slicing is a technique for viewing monochrome images in color by assigning each gray-scale level a unique color for display. Small differences in intensity (one bit of the gray-scale) are difficult for the eye to differentiate in monochrome, but become readily apparent when assigned unique colors. Changing only the contents of the Look-up table can transform the displayed image from monochrome into color.

#### SYSTEM DESIGN CRITERIA

VCC and ground planes are recommended for the TR9C1710 power distribution system. A 0.01uF and a 100pF high-frequency decoupling capacitors should be placed between the VCC and ground planes as near to the device as possible.

The signal lines connected to the /BLANK, P0-P7 and PCLK inputs must be either very short or terminated. It is recommended that a register be used adjacent to the TR9C1710's package to ease the timing constraints and eliminate any possibility of ringing or undershoot. This device is fabricated in CMOS technology, with high-impedance inputs that do not clamp to ground. If the P0-P7 signals are to be multiplexed, the use of three-state outputs is not recommended. Unprotected CMOS inputs should never be directly connected to traces that run off the PCB.

The IREF terminal requires a well-regulated current sink for proper operation (current flows to ground). Many different approaches to the design of the regulated current sink may be used, as long as the voltage on the IREF pin does not go below ground. Neither a resistor to a negative supply voltage nor a variable resistor is recommended. The IREF terminal may be isolated from noise by using a series inductance between IREF and the external current sink. Better results are obtained when IREF is not capacitively coupled to VCC.

This information is intended solely to stimulate design ideas. MUSIC<sup>TM</sup> accepts no liability for conceptual designs suggested herein. All users are cautioned to verify their own designs.

#### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage Voltage on all Other Pins

Temperature Under Bias Storage Temperature Maximum Reference Current Maximum DAC Output Current Maximum DC TTL Output Current -0.5 to 7.0 Volts -0.5 to VCC+0.5 Volts (-2.0 Volts for 10 ns, measured at the 50% point) -40°C to +85°C -55°C to +125°C -15 mA

45 mA (per Output) 20 mA (per Output, one at a time, one second duration) Stresses exceeding those listed under Absolute Maximum Ratings may induce failure. Exposure to absolute maximum ratings for extended periods may reduce reliability. Functionality at or above these conditions is not implied.

All voltages are referenced to GND at the device pins.

#### **OPERATING CONDITIONS**

| Symbol           | Parameter                                          | Min  | Typical | Max     | Units | Notes                                                     |

|------------------|----------------------------------------------------|------|---------|---------|-------|-----------------------------------------------------------|

| v <sub>cc</sub>  | Operating Supply Voltage                           | 4.5  | 5.0     | 5.5     | Volts |                                                           |

| V <sub>IH1</sub> | Input Voltage Logic "1" (all inputs except /W, /R) | 2.0  |         | VCC+0.5 | Volts |                                                           |

| V <sub>IH2</sub> | Input Voltage Logic "1" (/W, /R only)              | 2.2  |         | VCC+0.5 | Volts |                                                           |

| V <sub>IL</sub>  | Input Voltage Logic "0"                            | -0.5 |         | 0.8     | Volts | -1.0 Volts for 10 ns meas-<br>ured 50% amplitude (Fig. 4) |

| <sup>T</sup> A   | Ambient Operating Temperature                      | 0    |         | 70      | °C    | Still Air                                                 |

| <sup>I</sup> REF | Reference Current                                  | -3.5 | -8.88   | -10     | mA    |                                                           |

#### **ELECTRICAL CHARACTERISTICS (TTL-COMPATIBLE SIGNALS)**

| Symbol | Parameter                    | Min | Max | Units | Note                                                    |

|--------|------------------------------|-----|-----|-------|---------------------------------------------------------|

| 1cc    | Average Power Supply Current |     | 110 | mA    | PCLK=35 MHz; 1                                          |

|        |                              |     | 120 | mA    | PCLK = 50, 66 MHz; 1                                    |

|        |                              |     | 130 | mA    | PCLK = 80 MHz; 1                                        |

| V ОН   | Output Voltage Logic "1"     | 2.4 |     | Volts | I <sub>OH</sub> = -5.0 mA                               |

| VOL    | Output Voltage Logic "0"     |     | 0.4 | Volts | I <sub>OL</sub> = 5.0 mA                                |

| IILK   | Input Leakage Current        | -2  | 2   | μА    | V <sub>GND</sub> ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>    |

| IOLK   | Leakage Current (DQ0-DQ7)    | -10 | 10  | μА    | $V_{GND} \le V_{IN} \le V_{CC}$ , $/R \ge V_{IH}$ (min) |

#### **DAC SPECIFICATIONS**

| Symbol             | Parameter                | Min                  | Max  | Units  | Notes                                |

|--------------------|--------------------------|----------------------|------|--------|--------------------------------------|

| V <sub>REF</sub>   | Voltage on IREF          | V <sub>CC</sub> -3.0 | VCC  | Volts  | -10.0 ≤  REF ≤ -3.5 mA               |

| V <sub>O</sub> MAX | Maximum Output Voltage   |                      | 1.5  | Volts  | I <sub>O</sub> ≤ 10 mA; 10           |

| IO MAX             | Maximum Output Current   | 21                   |      | mA     | V <sub>O</sub> ≤ 1.0 Volts           |

|                    | Resolution               | 6                    |      | bits   |                                      |

|                    | Full Scale Error         |                      | ± 6  | %      | 2                                    |

|                    | DAC to DAC Correlation   |                      | 0.5  | %      | 3                                    |

|                    | Integral Nonlinearity    |                      | ±0.5 | LSB    | 4                                    |

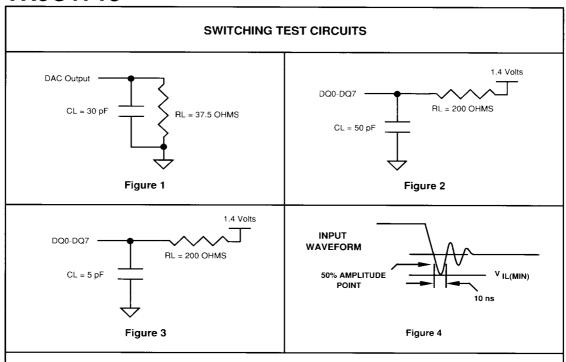

|                    | Rise Time (DAC Output)   |                      | 6    | ns     | 6; 10 to 90%; Load shown in Figure 1 |

|                    | Full Scale Settling Time |                      | 12.5 | ns     | 5, 6; Load shown in Figure 1         |

|                    | Glitch Energy            |                      | 40   | pV-sec | 6; Load shown in Figure 1            |

#### **AC TEST CONDITIONS**

Input Signal Transitions0.0 to 3.0 VoltsInput Signal Rise and Fall Times≤ 3 nsDigital Input Timing Reference Level1.5 VoltsDigital Output Timing Reference Levels.8V and 2.4VDAC Switching Test LoadFigure 1TTL Switching Test LoadFigure 2

### CAPACITANCE

$T_{\mbox{\scriptsize A}}=0$  to  $70^{\circ}\mbox{\scriptsize C};\, \mbox{\scriptsize V}_{\mbox{\scriptsize CC}}=5.0\mbox{\scriptsize V}\pm\,10\%;\, \mbox{\scriptsize f}=1.0~\mbox{\scriptsize MHz}$

| Symbol | Parameter      | Max   | Notes                              |

|--------|----------------|-------|------------------------------------|

| CI     | Digital Input  | 7 pF  | 6, Pins 5 - 13 , 15 - 16 , 25 - 27 |

| CO     | Digital Output | 7 pF  | 6, Pins 17 - 24                    |

| COA    | Analog Output  | 10 pF | 6, 9; Pins 1 - 3                   |

#### **SWITCHING CHARACTERISTICS**

#### **VIDEO PORT**

|     |                             |                    | TR9C17 | 10-80 | TR9C17 | 10-66 | 10-66 TR9C1710-50 TR9C |     | TR9C17 | 10-35 |       |       |

|-----|-----------------------------|--------------------|--------|-------|--------|-------|------------------------|-----|--------|-------|-------|-------|

| No. | Symbol                      | Parameter          | Min    | Max   | Min    | Max   | Min                    | Max | Min    | Max   | Units | Notes |

| 1   | t <sub>CHCH</sub>           | PCLK Period        | 12.5   |       | 15     |       | 20                     |     | 28     |       | ns    |       |

| 2   | <sup>t</sup> CLCH           | PCLK LOW           | 4      |       | 5      |       | 6                      |     | 9      |       | ns    |       |

| 3   | <sup>t</sup> CHCL           | PCLK HIGH          | 4      |       | 5      |       | 6                      |     | 7      |       | ns    |       |

| 4   | tpvch                       | Pixel setup        | 3      |       | 3      |       | 3                      |     | 4      |       | ns    |       |

| 5   | <sup>t</sup> CHPX           | Pixel hold         | 3      |       | 3      |       | 3                      |     | 4      |       | ns    |       |

| 6   | <sup>t</sup> BVCH           | BLANK setup        | 3      |       | 3      |       | 3                      |     | 4      |       | ns    |       |

| 7   | t <sub>CHBX</sub>           | BLANK hold         | 3      |       | 3      |       | 3                      |     | 4      |       | ns    |       |

| 8   | t <sub>CHAV</sub>           | PCLK to DAC valid  | 0      | 20    | 0      | 20    | 0                      | 25  | 0      | 3     | ns    | 7     |

| 8a  | t <sub>CHAV</sub><br>(skew) | DAC to DAC<br>Skew |        | 1     |        | 1     |                        | 1   |        | 1     | ns    | 7     |

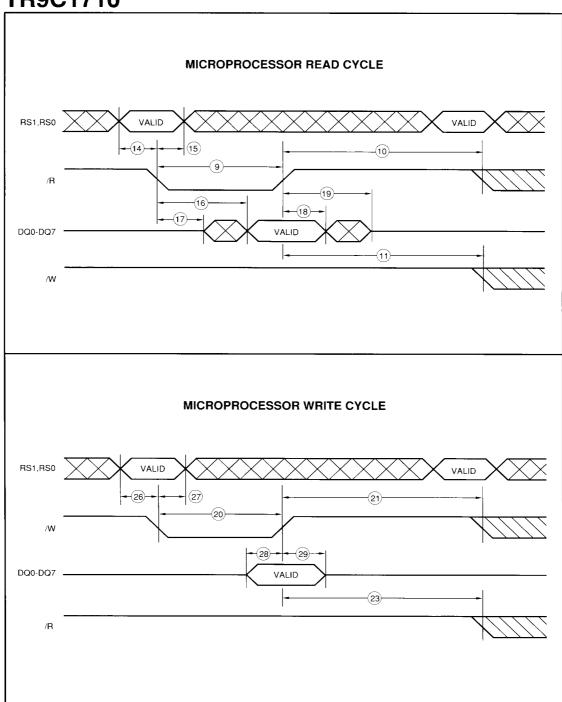

#### MICROPROCESSOR PORT READ CYCLE

|     |                    |                          | All Speed             | All Speed Grades |       |       |   |

|-----|--------------------|--------------------------|-----------------------|------------------|-------|-------|---|

| No. | Symbol             | Parameter                | Min                   | Max              | Units | Notes |   |

| 9   | t <sub>RLRH</sub>  | Read Pulse Width         | 50                    |                  | ns    |       |   |

| 10  | t <sub>RHRL1</sub> | Successive Read Interval | 3 X t <sub>CHCH</sub> | ·                | ns    |       |   |

| 11  | t <sub>RHWL1</sub> | Read to Write            | 3 X t <sub>CHCH</sub> | •                | ns    |       |   |

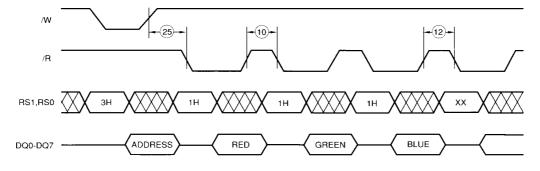

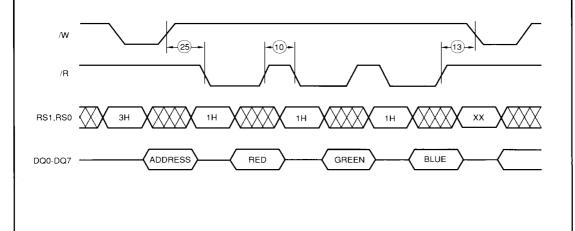

| 12  | t <sub>RHRL2</sub> | Color Read to Read       | 6 X t <sub>CHCH</sub> |                  | ns    |       |   |

| 13  | t <sub>RHWL2</sub> | Color Read to Write      | 6 X t <sub>CHCH</sub> |                  | ns    |       |   |

| 14  | tsvrl              | Register Select Setup    | 10                    |                  | ns    |       |   |

| 15  | <sup>t</sup> RLSX  | Register Select Hold     | 3                     |                  | ns    |       |   |

| 16  | t <sub>RLQV</sub>  | Data Access from /R      |                       | 40               | ns    |       |   |

| 17  | t <sub>RLQX</sub>  | Output turn-on from /R   | 3                     |                  | ns    |       | _ |

| 18  | tRHQX              | Data hold from /R        | 3                     |                  | ns    |       |   |

| 19  | t <sub>RHQZ</sub>  | Data Three-state Delay   |                       | 20               | ns    | 8     |   |

#### **SWITCHING CHARACTERISTICS (CONT'D)**

#### MICROPROCESSOR PORT WRITE CYCLE

|     |                    |                               | All Speed Grades      |     |       |       |   |

|-----|--------------------|-------------------------------|-----------------------|-----|-------|-------|---|

| No. | Symbol             | Parameter                     | Min                   | Max | Units | Notes |   |

| 20  | t <sub>WLWH</sub>  | Write Pulse Width             | 50                    |     | ns    |       |   |

| 21  | t <sub>WHW1</sub>  | Successive Write Interval     | 3 X t <sub>CHCH</sub> |     | ns    |       |   |

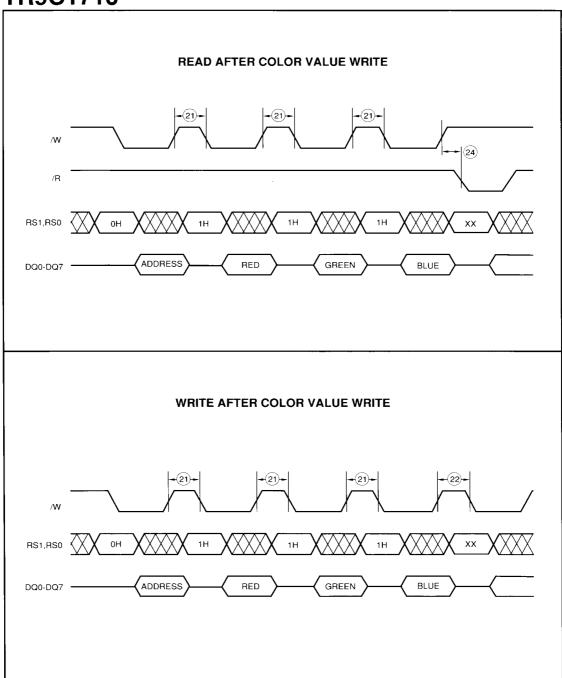

| 22  | t <sub>WHW2</sub>  | Write After Color Write       | 3 X t <sub>CHCH</sub> |     | ns    |       |   |

| 23  | t <sub>WHRL1</sub> | Write to Read                 | з x t <sub>CHCH</sub> |     | ns    |       | - |

| 24  | twhrl2             | Color Write to Read           | 3 X t <sub>CHCH</sub> |     | ns    |       |   |

| 25  | t <sub>WHRL3</sub> | Read after Read Address Write | 6 X t <sub>CHCH</sub> |     | ns    |       |   |

| 26  | tsvwL              | Register Select setup         | 10                    |     | ns    |       |   |

| 27  | twLSX              | Register Select hold          | 3                     |     | ns    |       |   |

| 28  | t <sub>DVWH</sub>  | Data setup to /W HIGH         | 10                    |     | ns    |       |   |

| 29  | twhdx              | Data hold from /W HIGH        | 3                     |     | ns    |       | - |

#### **NOTES**

- ICC is measured with VCC = VCC (max) and tCHCH = tCHCH (min). The DAC test load is as shown in Figure 1. DQ0-DQ7 are unloaded. IREF = -8.88 mA.

- 2. Full Scale Error is measured from the value given by the design equation. IREF = -8.88 mA.

- 3. Measured from the DAC output with the center value. IREF = -8.88 mA.

- 4. Measured from a straight line between the endpoints. Monotonicity is guaranteed.

- Full Scale Settling Time is measured from a 2% change in output voltage until the output voltage has settled to within ± 2% of final value.

- 6. Guaranteed but not 100% tested.

- 7. Measured at the 50% point between the starting and ending DAC values.

- 8. Measured from a  $\pm$  200 mV change from the steady-state voltage using Test Load as shown in Figure 3.

- 9.  $/BLANK \le VIL$  (MAX) to Disable RED, GREEN, and BLUE Analog outputs.

- 10. All DAC outputs must be terminated and not left floating. The equivalent of a double- or single-terminated 75-ohm transmission line (37.5-ohm or 75-ohm resistive load), can be used. Unused DAC outputs may also be directly tied to ground.

## **SWITCHING WAVEFORM** KEY **WAVEFORMS INPUTS** OUTPUTS Will be Must be steady steady May change Will be changing from H to L from H to L May change Will be changing from L to H from L to H Don't care. Undefined. Any change State unknown permitted Center line is Does not apply high impedance "off state" **VIDEO TIMING** PCLK P0-P7 /BLANK WHITE REF. LEVEL 💊 -(8)-DAC (RED, GREEN, BLUE) BLACK REF. LEVEL BLANKING LEVEL

10

# COLOR VALUE READ TO READ

#### **COLOR VALUE READ TO WRITE**

Rev 1

14

15

#### ORDERING INFORMATION

| Part Number                                                    | Speed                                | Package                                               | Temperature Range |

|----------------------------------------------------------------|--------------------------------------|-------------------------------------------------------|-------------------|

| TR9C1710- <b>XXY</b> C<br>XX= 35<br>XX= 50<br>XX= 66<br>XX= 80 | 35 MHz<br>50 MHz<br>66 MHz<br>80 MHz | -                                                     | 0 to 70°C         |

| Y= P<br>Y= D<br>Y= E                                           |                                      | 28-pin, Plastic DIP<br>44-pin, PLDCC<br>32-pin, PLDCC |                   |

#### **MUSIC™** Semiconductors

#### U.S.A. Headquarters

MUSIC Semiconductors, Inc. 1150 Academy Park Loop Suite 202 Colorado Springs, CO 80910

Telephone: (719) 570-1550 Within U.S.: (800) 933-1550 FAX: (719) 570-1555

#### U.S. Western Area Sales

MUSIC Semiconductors, Inc. 1136 E. Hamilton Avenue Suite 203 Campbell, CA 95008

Telephone: (408) 371-3993 FAX: (408) 371-0878

MUSIC<sup>TM</sup> Semiconductors agent or distributor:

#### **European Headquarters**

MUSIC Semiconductors BV PO Box 184 NL-6470 ED Eygelshoven The Netherlands

Telephone: +31 45 467878 Europe FAX: +31 45 467822 Far East and Corporate FAX: +31 45 353675

#### U.S. Eastern Area Sales

MUSIC Semiconductors, Inc. P.O. Box 415 234 West Mill Road Long Valley, NJ 07853

Telephone: (908) 876-9691 FAX: (908) 876-9542

MUSIC<sup>TM</sup> Semiconductors reserves the right to make changes to its products and specifications at any time in order to improve on performance, manufacturability or reliability. Information furnished by MUSIC<sup>TM</sup> is believed to be accurate, but no responsibility is assumed by MUSIC<sup>TM</sup> Semiconductors for the use of said information, nor for any infringements of patents or of other third-party rights which may result from said use. No license is granted by implication or otherwise under any patent or patent rights of any MUSIC<sup>TM</sup> company.

© Copyright 1991, MUSIC 151 Semiconductors NV